# THE WORLD'S FIRST ....

# S-100 Single Board Computer

# **TECHNICAL MANUAL**

for

# **SUPER QUAD**

12700-B Knott Avenue, Garden Grove, CA 92641 TELE: (714) 891-4004 / TELEX: 678401 Tabirin

#### INTRODUCTION

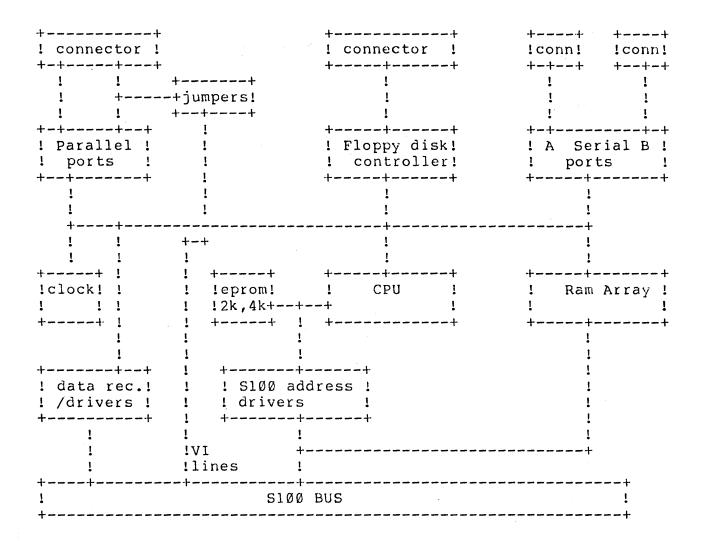

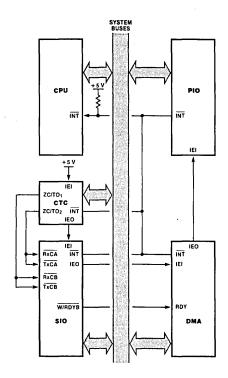

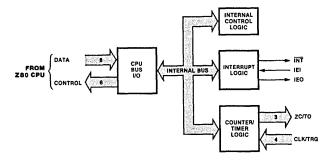

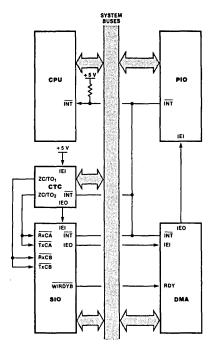

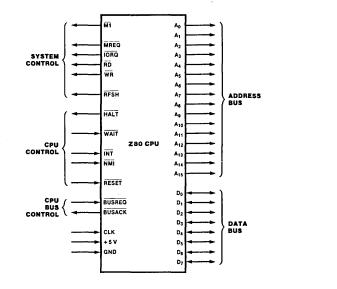

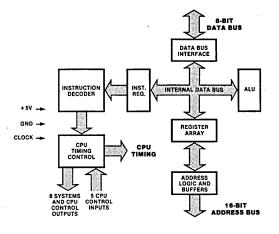

ADVANCED DIGITAL CORPORATION is proud to introduce the SUPER QUAD. The SUPER QUAD is a Z80 based single board computer designed to be a bus master in an S100 bus system. The SUPER QUAD SEC has all the hardware needed to run a single user CP/M system or 2 user MP/M system with up to 4 external floppy disk drives and an external Centronics parallel interface printer all on one board. The board also runs with TURBO-DOS tm. The SUPER QUAD SEC contains:

| 1) | Z-80A cpu                  | (4 MHZ)                                 |

|----|----------------------------|-----------------------------------------|

| 2) | Floppy disk controller     | (up to 4 drives 8" or $5\frac{1}{4}$ ") |

| 3) | 64K of dynamic memory      | (16K bank selectible)                   |

| 4) | 2K or 4K of shadow eprom   | (2716 or 2732)                          |

| 5) | 2 serial ports             | (Z80A SIO opt. syncronous)              |

| 6) | 2 12 bit parallel ports,   | (Z80A PIO)                              |

|    | one of which can be used   |                                         |

|    | for S100 vectored interrup | ts                                      |

| 7) | Real time interrupt clock  | (Z80A CTC)                              |

|    |                            |                                         |

8) Sl00 extended address Al6-A23

ONE YEAR WARRANTY.

τ

\*Note: Items 5 and 6 require external adaptation for RS-232 and Centronics. The adapter boards are 2 x 2" and are called PS NET. They hoop up to the back of the main frame with a DB-25 connector.

### TABLE OF CONTENTS

|                |                                                                                 |                                                                                                                                                                                                                                                                                                                                               | Page                                               |

|----------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Introduction . |                                                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                         | . 1                                                |

| Table of Conte | nts                                                                             |                                                                                                                                                                                                                                                                                                                                               | . 2,3                                              |

| 1.0            | Operatio<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7                       | Floppy disk<br>64 K Dynamic Ram<br>Monitor Eprom<br>Serial Ports<br>Parallel Ports<br>Real Time Clock<br>SlØØ bus interface                                                                                                                                                                                                                   | . 4<br>. 4<br>. 5<br>. 5<br>. 5<br>. 6             |

| 2.0            | EPROM ar<br>2.1<br>2.2<br>2.3<br>2.4                                            | nd Monitor<br>Enable / Disable software<br>Monitor Sign-on<br>Monitor Commands<br>Cold boot loader program                                                                                                                                                                                                                                    | . 7<br>. 8<br>. 8                                  |

| 3.0            | Input /                                                                         | Output port assignments                                                                                                                                                                                                                                                                                                                       | . 10                                               |

| 4.0            | Input /                                                                         | Output port description                                                                                                                                                                                                                                                                                                                       | . 11                                               |

|                | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                     | SIO serial port channel A<br>SIO serial port channel B<br>PIO parallel port channel A<br>PIO parallel port channel B<br>Control timer Interrupt circuit<br>Floppy Disk controller<br>Floppy disk control port<br>Extended address port<br>On-board memory control port                                                                        | <pre>. 11 . 11 . 11 . 11 . 11 . 11 . 12 . 13</pre> |

| 5.0            | Jumper d                                                                        | lefinitions                                                                                                                                                                                                                                                                                                                                   | . 15                                               |

| 6.0            | Jumper 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10 | Jumper A - CPU clock rate<br>Jumper B - SIO channel A clock<br>Jumper C - SIO channel B clock<br>Jumper D - Drive type selection<br>Jumper E - VIO / PINT<br>Jumper P - VIO / paralled bit DØ<br>Jumper N - VII / paralled bit D1<br>Jumper M - VI2 / paralled bit D2<br>Jumper K - VI3 / paralled bit D3<br>Jumper J - VI4 / paralled bit D4 |                                                    |

|                | 6.11<br>6.12                                                                    | Jumper H - VI5 / paralled bit D5<br>Jumper G - VI6 / paralled bit D6                                                                                                                                                                                                                                                                          |                                                    |

|      | 6.13<br>6.14<br>6.15                           | Jumper F - V17 / paralled bit D7<br>Jumper R - 2716 / 2732<br>Jumper S - Floppy connector                                                                                                                                                                                                                                                                                                                                  | 19<br>19                         |

|------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|      | 6.16<br>6.17                                   | Jumper T - Memory Write Signal<br>Jumper layout                                                                                                                                                                                                                                                                                                                                                                            | 2Ø<br>AA                         |

| 7.0  | Baud Rat<br>7.1                                | te Switch<br>Switch Setting                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21                         |

| 8.0  | External<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5    | <pre>L Connector pin definitions<br/>J1 - SlØØ bus<br/>J2 - Parallel Port<br/>J3 - Floppy Disk controller<br/>J4 - Serial port channel A<br/>J5 - Serial port channel B</pre>                                                                                                                                                                                                                                              | 22<br>22<br>23<br>24<br>25<br>25 |

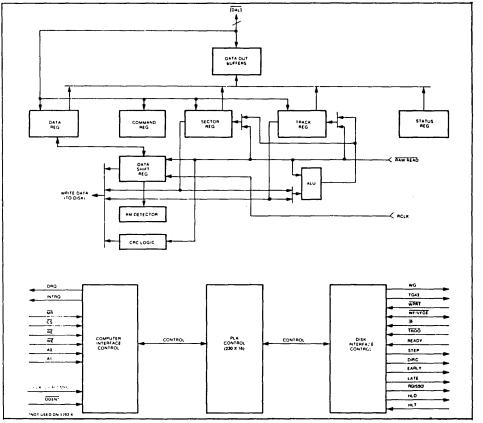

| 9.0  | Block Di                                       | iagram                                                                                                                                                                                                                                                                                                                                                                                                                     | 26                               |

| 10.0 | Factory<br>10.1                                | Installed Jumpers                                                                                                                                                                                                                                                                                                                                                                                                          | 27                               |

|      | 10.2<br>10.3<br>10.4<br>10.5<br>10.6           | 5.25 inch drive configuration<br>Shugart 800 drive<br>shugart 850<br>MPI drive<br>MFE model 700                                                                                                                                                                                                                                                                                                                            | 28<br>29                         |

|      | 10.0<br>10.7<br>10.8<br>10.9                   | TANDON SLIM LINE<br>NEC model FD1160<br>QUME Data Track 8                                                                                                                                                                                                                                                                                                                                                                  | 30                               |

|      | 10.9.1                                         | TANDON 5 1/4"                                                                                                                                                                                                                                                                                                                                                                                                              | 31                               |

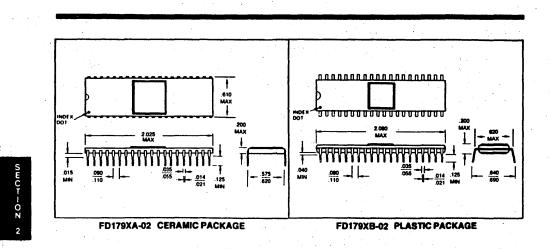

| 11.0 | 11.1<br>11.2<br>11.3<br>11.4<br>11.4.1<br>11.5 | <pre>&amp; &amp; Data sheets<br/>Appendex A - Z80A SIO / DART<br/>Appendex B - Z80A PIO<br/>Appendex C - Z80A CTC<br/>Appendex D - Floppy Disk controller<br/>WD 1691,BR1941<br/>Appendex E - Z80A CPU<br/>Appendix F- FLOPPY ERROR CODE<br/>Warranty<br/>Application notes:<br/>Turbo-Dos app. notes<br/>Additional memory boards<br/>Recomended additional S-100 boards:<br/>Hard disk: morrow designs,konan,xcomp</pre> | 32                               |

|      |                                                | Memory: measurement systems,PCE<br>Graphics: micro angelo<br>Slave Processor: Advanced Digital, Musys                                                                                                                                                                                                                                                                                                                      | corp.                            |

- 12.0 Parts list

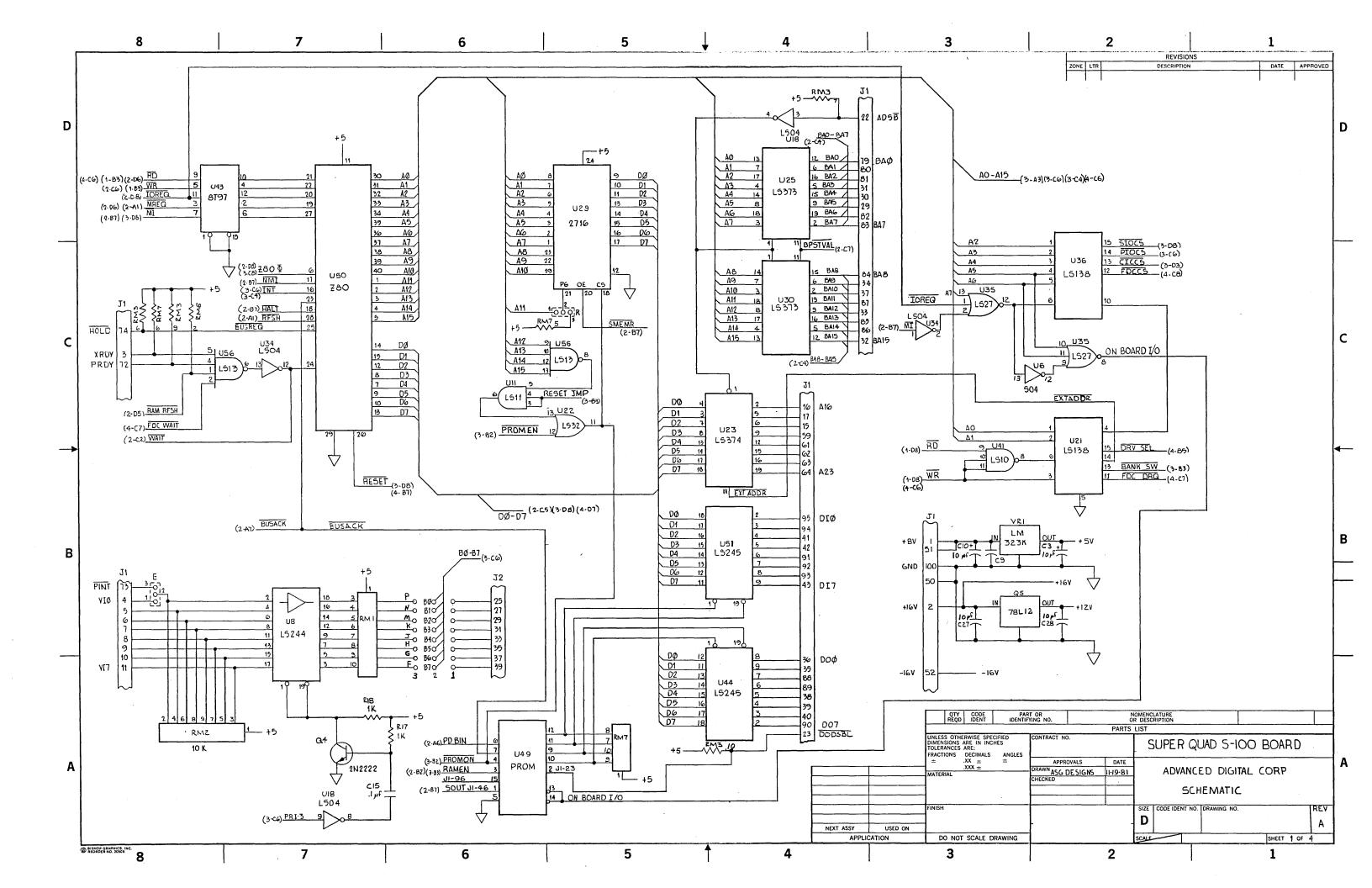

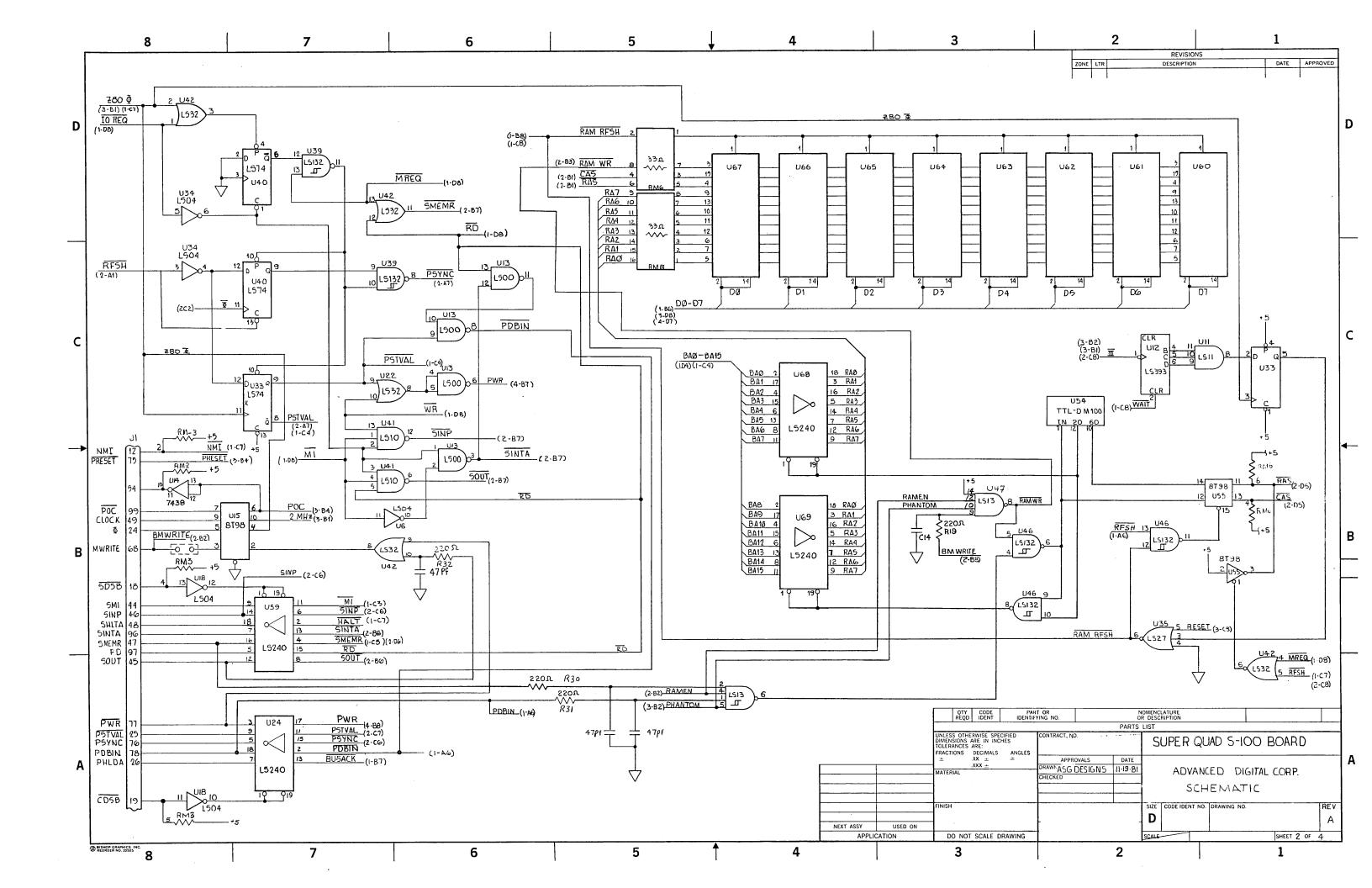

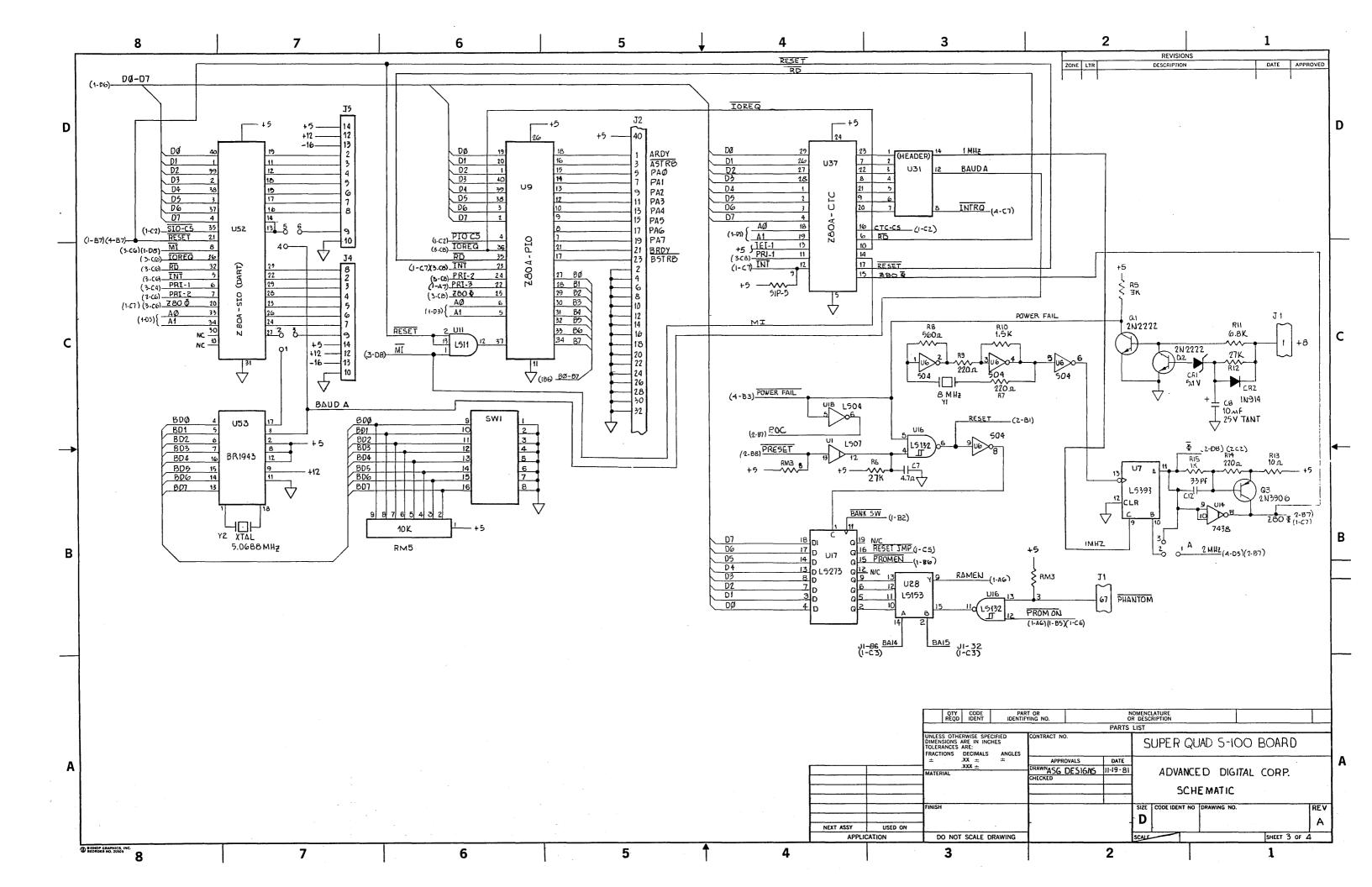

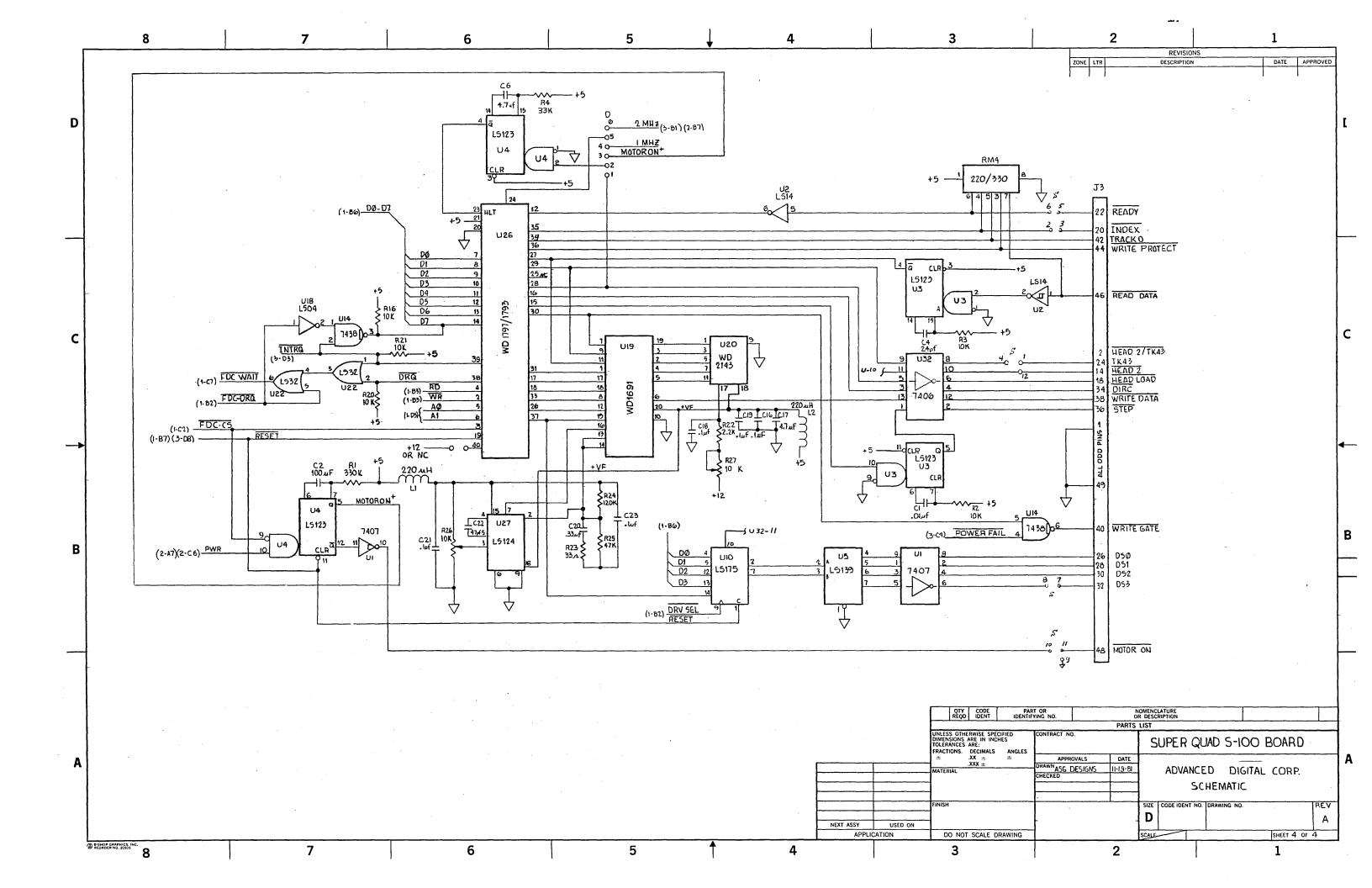

- 13.0 Schematic Diagram

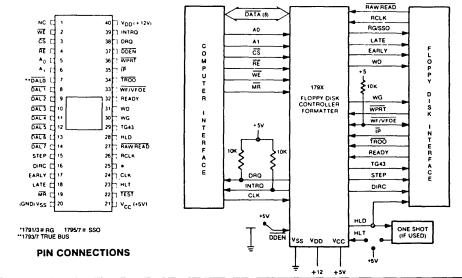

### 1.1 The Floppy Disk Controller

The floppy disk controller can access up to four 8 inch or 5.25 inch floppy disk drives. It can read and write IBM 374Ø single density format and double density 128,256,512,1024 sector size formats. Data transfer is done by programmed I/O with wait and interrupt syncronization.

Note : The controller cannot access both 8 inch and 5.25 inch drives simultaniously, The controller is switched from 8 inch to 5.25 inch drives by hardware jumper options.

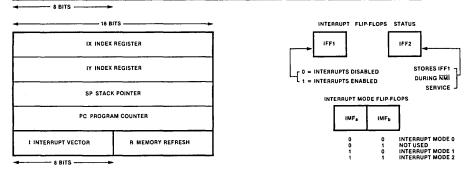

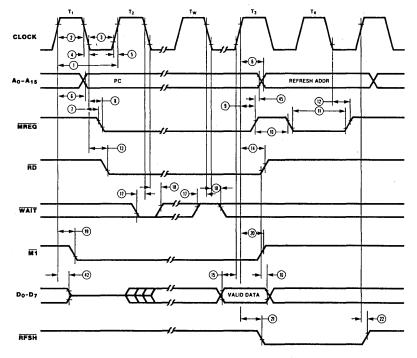

### 1.2 The 64 k Dynamic ram

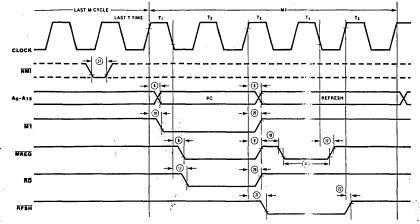

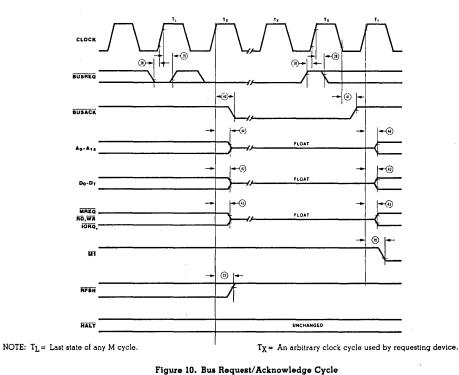

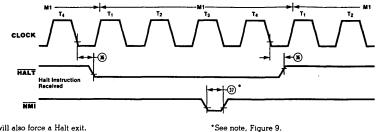

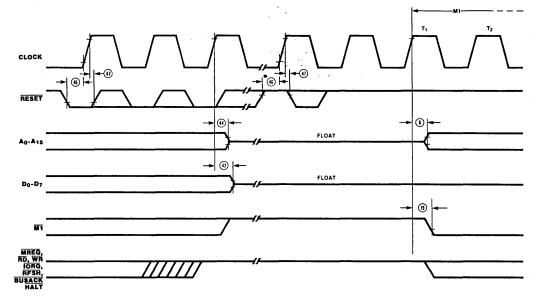

The 64 k ram array can be switched on and off in 16 k increments (Ø-16K,16K-32K,32K-48K,48K-64K) under software control. This allows the CPU to access bank switchable external memory on the S100 bus. The memory has an access time of 200ns. Refresh is done during Z80 Ml cycles and during wait and reset states. The memory can be accessed by an external DMA device on the S100 bus. Note : Any external DMA device that is using continous mode DMA cycles must transfer data at an average rate of 15 us per byte or faster when holding the DMA request line for more than 1.5 ms This is not a problem because most designers are smart enough to use byte-at-a-time or burst transfer modes when dealing with slow DMA transfer rates. The ram row address is the low order address therefor the entire ram array is refreshed by the DMA device every 128 contiguous memory cycles.

### 1.3 System Monitor Eprom

The system monitor eprom is switched on during reset. It can be disabled and enabled under software control. It resides when enabled at FØØØh to FFFFh. It has commands that allow the user to load the CP/M , MP/M or other boot loaders from floppy disk. In addition it can be used to load , examine goto and test memory. When the prom is disabled it does not use any system address space.

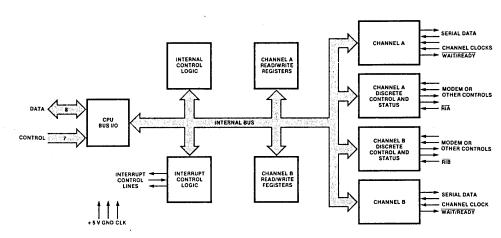

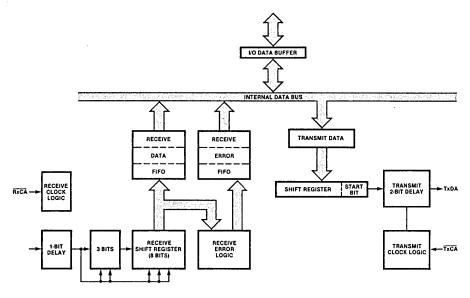

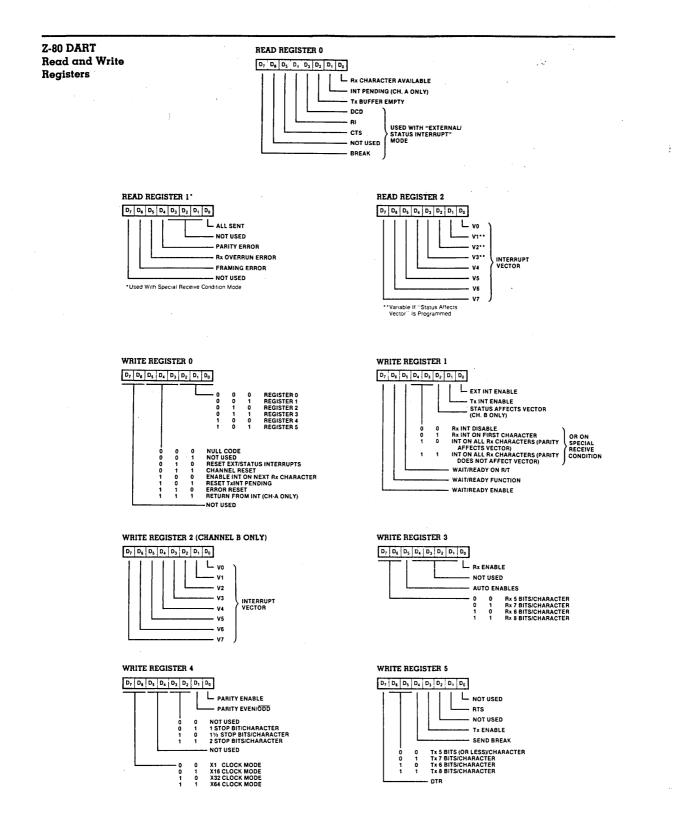

#### 1.4 Serial ports

A Z80A DART is used for the two serial ports , but a Z80A SIO/0 chip can be used in it's place. This allows asyncronous and synchronous serial data communications plus a variety of interrupt modes. Modem control signals are available at each serial connector. There are two switch selectible baud rate generators for baud rates of 50 to 19.2 k baud. Note : The serial ports are TTL and must be connected to external interface boards for RS232 communications.

(PS NET/I)

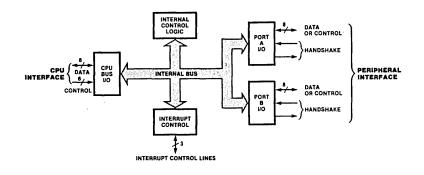

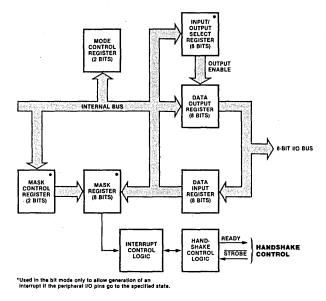

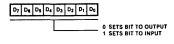

1.5 Parallel ports

A Z80A PIO is used as the parallel port. The "A" channel of this chip is connected to the parallel port connector. This port has 8 bi-directional data lines and two hand shake lines. The "B" port can be split between the parallel port connector and the S100 bus vectored interrupt lines by jumper options. This allows the port to be used as an additional parallel port or interrupt controller or both. In the output mode the parallel ports can drive one TTL load .

### 1.6 Real Time Interrupt clock

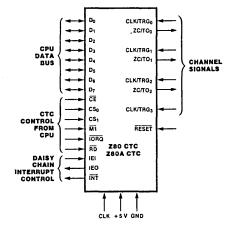

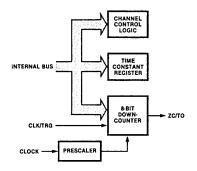

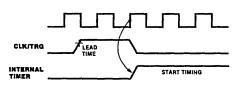

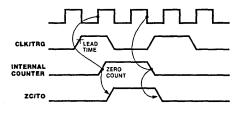

A Z80A CTC is used for providing a real time system clock for MP/M. Three channels of the CTC are available to the user for strapping via a jumper header for synchronous baud rates or long clock times.

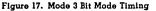

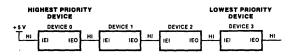

#### 1.7 SlØØ Bus Interface

The S100 bus interface provides the signals necessary for an 8 bit bus master as described by the IEEE 696 bus specification. Vectored interrupt lines VIO - VI7 are supported via jumper options and A16 - A23 are also supported vis an I/O port. The PAMNTON line is also implemented for the dynamic ram array.

#### 2.0 EPROM and Monitor operation

The onboard EPROM occupies address FØØØH-FFFFH. The EPROM is switched on automatically during reset or power on, the EPROM contains SIO and FDC initialization code along with a simple debugger and floppy disk cold start loader. After the operating system is loaded the EPROM can be turned off so that the ram at address FØØØH-FFFFH can be accessed. The EPROM can be turned on and off at any time so that hardware dependent I/O routines can be called.

2.1 Eprom Enable / Disable

Switching EPROM on :

| FØ33 3E4F             | MVI A,01001111B | ;RESET POWER ON JUMP<br>; AND ENABLE MEMORY, EPROM ON  |

|-----------------------|-----------------|--------------------------------------------------------|

| FØ35 D316             | OUT 16H         | WRITE TO CONTROL PORT                                  |

| Switching EPROM off : |                 |                                                        |

| FØ33 3E4F             | MVI A,Ø1101111B | ;RESET POWER ON JUMP<br>; AND ENABLE MEMORY, EPROM OFF |

| FØ35 D316             | OUT 16H         | WRITE TO CONTROL PORT                                  |

Jumper R configures the board to accept a 2716 or 2732 EPROM. Note : The EPROM is always addressed at F800H and can not be moved. Since the 2716 EPROM is 2K long it appears

twice , F800H-FC00H and FBFFH-FFFFH.

2.2 Monitor Signon

The EPROM contains a simple debugger. The monitor signs on with :

> ADVANCED DIGITAL CORP. Monitor Version 1.1 Mar - 1982 Press "H" for help >

2.3 Monitor Commands

The monitor commands are :

•

| •                      |                                    |                                       |

|------------------------|------------------------------------|---------------------------------------|

| Control B              | = Load disk boot loader 5.25"      |                                       |

| Control C              | = Load disk boot loader 8 "        |                                       |

| D SSSS QQQQ            | = Dump memory in hex from SSSS     | to QQQQ                               |

| F SSSS QQQQ BB         | = Fill memory from SSSS to QQQ     | Q with BB                             |

| G AAAA                 | = Go to address AAAA               |                                       |

| L AAAA                 | = Load memory starting at AAAA     |                                       |

| M SSSS QQQQ DD         | = Move from S to Q to ADDR DD      |                                       |

| P SSSS QQQQ            | = Print in ascii from SSSS to      | QQQQ                                  |

| Т                      | = Test Memory                      |                                       |

| ESC will termin        | ate any command                    |                                       |

| The cold best          | and ar will coloct and home driv   | 10 <i>A</i>                           |

| The cord boot 1        | loader will select and home driv   |                                       |

| Track Ø sector         | 1 will be read into memory at 1    | ocation Ø.                            |

| Single density         | is assumed for track $\emptyset$ . |                                       |

| If an error occ        | ures an error code will be prin    | ited.                                 |

| The error code         | must be translated using the t     | able                                  |

|                        | BOOT ERROR 80= DISK NOT DETECTED   | )<br>IO DATA ON DISK OR BAD PHASE LOC |

| 2.4 Cold Bo            | oot Program                        |                                       |

|                        | ; READ TRACK O SECTOR 1 INTO M     | 1EMORY                                |

|                        | BOOT 5: MVI A,Ø8H<br>OUT WAIT      | ;set double for 5 inch                |

|                        | BOOT:                              | DECEM EDC                             |

| F4B5 3EØD<br>F4B7 D3ØC | MVI A,ØDH<br>OUT FDC               | ; RESET FDC<br>; ISSUE COMMAND        |

| F4B9 ØØ                | NOP                                | , 10000 COLUMNO                       |

|                        | FDCW1:                             |                                       |

| F4BA DBØC<br>F4BC ØF   | IN FDC<br>RRC                      | ; CHECK BUSY                          |

| F4BD DABAF4            | JC FDCW1                           |                                       |

| F4CØ ØØ                | NOP                                | ; KILL TIME                           |

|                        |                                    |                                       |

| F4C1<br>F4C2                                 |                                    |         | NOP<br>NOP                                            |                                                       |       |                                                                                                      |

|----------------------------------------------|------------------------------------|---------|-------------------------------------------------------|-------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------|

| F4C3                                         | ØØ                                 |         | NOP                                                   |                                                       |       |                                                                                                      |

|                                              | 3EØ3<br>D3ØC<br>ØØ                 |         | MVI<br>OUT<br>NOP                                     | A,3<br>FDC                                            | •     | GET A RESTORE<br>ISSUE COMMAND                                                                       |

| F4C9<br>F4CB                                 | DB14<br>ØØ                         | TKØ:    | IN<br>NOP                                             | WAIT                                                  | •     | WAIT FOR<br>INTRQ                                                                                    |

| F4CE                                         | DBØC<br>E604<br>CACCF4             |         | IN<br>ANI<br>JZ                                       | FDC<br>4<br>TKØ                                       | ;     | CHECK TRACK Ø                                                                                        |

| F4D3<br>F4D4<br>F4D5<br>F4D6                 | 6F<br>67                           |         | XRA<br>MOV<br>MOV<br>INR                              | A<br>L,A<br>H,A<br>A                                  | ;     | POINT AT LOC Ø                                                                                       |

| F4D7<br>F4D9                                 | D3ØE<br>3E8C<br>D3ØC               |         | OUT<br>MVI<br>OUT<br>NOP                              | FDCSEC<br>A,Ø8CH<br>FDC                               | ;     | SET SECTOR<br>GET READ COMMAND<br>ISSUE COMMAND                                                      |

| F4DE<br>F4EØ<br>F4E1<br>F4E4<br>F4E6<br>F4E7 | DB14<br>B7<br>F2EBF4<br>DBØF<br>77 | FDCRD:  | IN<br>ORA<br>JP<br>IN<br>MOV<br>INX<br>JMP            | WAIT<br>A<br>BOOTDN<br>FDCDATA<br>M,A<br>H<br>FDCRD   | ;;;   | WAIT FOR INTRQ<br>OR DRQ<br>EXIT IF INTRQ<br>GET DATA<br>STORE<br>POINT NEXT                         |

| F4ED<br>F4EE<br>F4F1<br>F4F2<br>F4F5<br>F4F8 | CAØØØØ<br>F5<br>210FF6<br>CDE6FØ   | BOOTDN: | IN<br>ORA<br>JZ<br>PUSH<br>LXI<br>CALL<br>POP<br>CALL | FDC<br>A<br>Ø<br>PSW<br>H,BTERR<br>MSG<br>PSW<br>THXB | ;;;;; | CHECK STATUS<br>Ø = NO ERROR<br>OK, GO<br>SAVE ERROR<br>PRINT<br>DISK ERROR<br>GET ERROR<br>PRINT IT |

3.Ø

| Add | re | ss |  |

|-----|----|----|--|

|-----|----|----|--|

#### Function

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>09<br>08 | Read/Write<br>Read/Write<br>Read/Write<br>Read/Write<br>Read/Write<br>Write<br>Write<br>Read/Write<br>Read/Write<br>Read/Write<br>Read/Write | <pre>SIO Channel A Data port SIO Channel A Status/Control Port SIO Channel B Data port SIO Channel B Status/Control Port PIO Channel A Data port PIO Channel B Data port PIO Channel B Control port PIO Channel B Control Port CTC Channel Ø Control Port CTC Channel 1 Control Port CTC Channel 2 Control Port</pre> |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ØB                                                             | Read/Write                                                                                                                                   | CTC Channel 3 Control Port                                                                                                                                                                                                                                                                                            |

| ØC                                                             | Read/Write                                                                                                                                   | FDC Command/States Port                                                                                                                                                                                                                                                                                               |

| ØD                                                             | Read/Write                                                                                                                                   | FDC Track Register                                                                                                                                                                                                                                                                                                    |

| ØE                                                             | Read/Write                                                                                                                                   | FDC Sector Register                                                                                                                                                                                                                                                                                                   |

| ØF                                                             | Read/Write                                                                                                                                   | FDC Data Port                                                                                                                                                                                                                                                                                                         |

| 10                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 11                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 12                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 13                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 14                                                             | Read/Write                                                                                                                                   | FDC Syncronization/Drive/Density                                                                                                                                                                                                                                                                                      |

| 15                                                             | Write                                                                                                                                        | SlØØ Buss Extended Address Al6-A24                                                                                                                                                                                                                                                                                    |

| 16<br>17                                                       | Write                                                                                                                                        | On-Board Memory Control Port                                                                                                                                                                                                                                                                                          |

| 17                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 18                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 19<br>1A                                                       |                                                                                                                                              | Unused<br>Unused                                                                                                                                                                                                                                                                                                      |

| 1A<br>1B                                                       |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 16<br>1C                                                       |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 10<br>1D                                                       |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 1D<br>1E                                                       |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| 1F                                                             |                                                                                                                                              | Unused                                                                                                                                                                                                                                                                                                                |

| - <del>-</del>                                                 |                                                                                                                                              |                                                                                                                                                                                                                                                                                                                       |

All addresses are listed in Hexidecimal.

The unused input / output ports are internally decoded and should not be used by external S100 1/0 boards.

4.0 INPUT / OUTPUT FORT DISCRIPTIONS

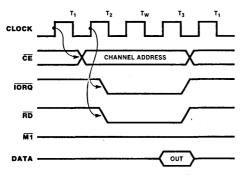

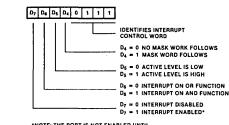

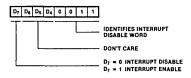

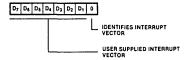

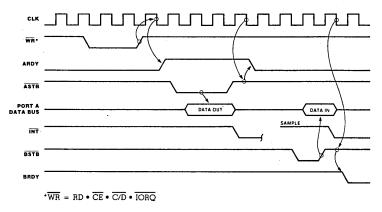

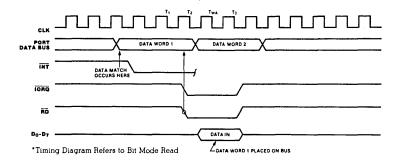

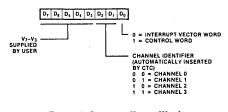

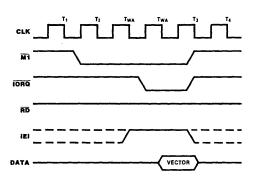

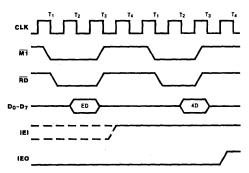

Serial Communications Port A --- See Appendex A 4.1 ØØ Read/Write SIO Channel A Data port Øl Read/Write SIO Channel A Status/Control Port Serial Communications Port B --- See Appendex A 4.2 Ø2 Read/Write SIO Channel B Data port 03 Read/Write SIO Channel B Status/Control Port Paralled Interface Port A ---4.3 See Appendix B 04 Read/Write PIO Channel A Data port Ø6 Write PIO Channel A Control Port 4.4 Parallel Interface Port B ---See Appendix B This port can be jumpered via jumpers E through P to the S100 Vectored Interrupt lines or to connector J2 (see sec 6.0 ) Ø5 Read/Write PIO Channel B Data port 07 Write PIO Channel B Control Port 4.5 Control Timmer Interrupt circuit --- See Appendix C Ø8 Read/Write CTC Channel Ø Control Port CTC Channel 1 Control Port Ø9 Read/Write ØA Read/Write CTC Channel 2 Control Port ØВ Read/Write CTC Channel 3 Control Port 4.6 Floppy Disk Controller See Appendix D \_\_\_\_ Read/Write FDC Command/States Port ØC ØD Read/Write FDC Track Register Rcad/Write FDC Sector Register ØE ØF Read/Write FDC Data Port

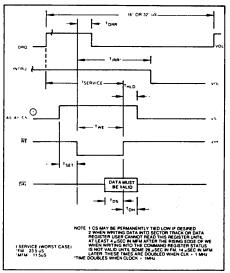

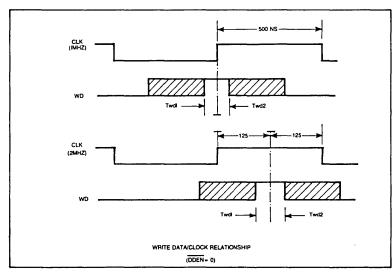

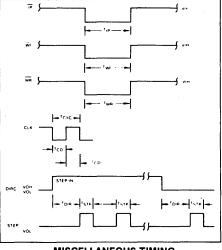

#### 4.7 Floppy Disk Control Port 14 Read/Write

FDC Syncronization/Drive/Density

# Port Read : CC

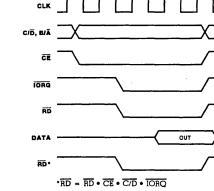

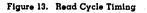

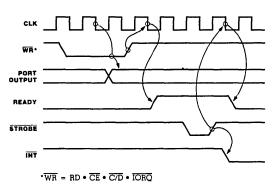

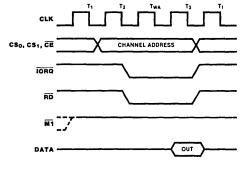

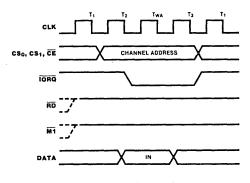

When the cpu reads this port the cpu is placed into a wait state until a data byte can be transfered to or from the floppy disk controller or untill the command complete/terminate status (INTRQ) is set by the floppy disk controller. The floppy disk controller INTRQ status bit is placed on the data bus as bit D7. This bit can be tested to determine if data is to be transfered of if the command is complete.

| +. |    | +-  |    | -+- |    | •+• |    | -+- |    | -+- |    | -+- |    | -+- |    | +       |        |     |         |     |

|----|----|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|---------|--------|-----|---------|-----|

| 1  | D7 | 1   | D6 | ŗ   | D5 | !   | D4 | l   | D3 | 1   | D2 | !   | Dl | 1   | DO | ! D7    | = MSB, | DØ  | = LSB   | . 1 |

| +- |    | +-  |    | -+- |    | •+• |    | -+- |    | -+- |    | -+- |    | -+- |    | +       |        |     |         |     |

|    | 1  |     | 1  |     | !  |     | 1  |     | 1  |     | 1  |     | !  |     | 1  |         |        |     |         |     |

|    | 1  |     | 1  |     | !  |     | !  |     | 1  |     | 1  |     | 1  |     | +  | Don't c | are    |     |         |     |

|    | 1  |     | 1  |     | 1  |     | 1  |     | 1  |     | 1  |     | +  |     |    | Don't c | are    |     |         |     |

|    | 1  |     | 1  |     | 1  |     | 1  |     | 1  |     | +  |     |    |     |    | Don't c | are    |     |         |     |

|    | 1  |     | !  |     | 1  |     | 1  |     | +  |     |    |     |    |     |    | Don't c | are    |     |         |     |

|    | 1  |     | 1  |     | 1  |     | +  |     |    |     |    |     |    |     |    | Don't c | are    |     |         |     |

|    | 1  |     | 1  |     | +  |     |    |     |    |     |    |     |    |     |    | Don't c | are    |     |         |     |

|    | 1  |     | +  |     |    |     |    |     |    |     |    |     |    |     |    | Don't c | are    |     |         |     |

|    | +  | · · |    |     |    |     |    |     |    |     |    |     |    |     |    | INTRQ*  | Ø=acti | ve, | l=inact | ive |

#### Port Write :

The low two bits DØ and Dl of this port control which drive is selected.

| d |

|---|

| d |

| d |

| d |

|   |

Bit D3 sets the density mode. When bit D3 =  $\emptyset$ , single density is selected. When bit D3 = 1, double density is selected. +---+---+----+----+----+----+----+ ! D7 ! D6 ! D5 ! D4 ! D3 ! D2 ! D1 ! D0 ! D7 = MSB, D0 = LSB1 1 1 1 1 1 1 1 1 +-- Disk drive select bit DØ 1 1 1 1 1 1 1 ľ 1 1 ! 1 +---- Disk drive select bit Dl 1 1 1 +----- SIDE SELECT, Ø=HEAD Ø,1=HEAD 1 ļ 1 +----- Density, Ø=single, l=double 1 1 1 1 . +---- Don't care 1 ! 1 ----- Don't care 1 1 +----+---- Don't care 1 ----- Don't care Extended address port --- See Section 8.1 (buss defination) 4.8 Write S100 Buss Extended Address A16-A23 15 Port Write : This port controls the S100 Extended address lines. +---+ ! D7 ! D6 ! D5 ! D4 ! D3 ! D2 ! D1 ! D0 ! D7 = MSB,  $D\emptyset = LSB$ +---+ 1 1 1 1 1 1 1 1 . 1 ! 1 1 ! 1 +-- A16 1 +---- A17 1 1 1 1 1 Ţ +---- A18 1 1 1 1 ! 1 1 +---- A19 t 1 +---- A20 1 11 ----- A21 t 1 +------ A22 I ---- A23

4.9 On-Board Memory Control Port

16 Write On-Board Memory Control Port This port controls the onboard memory managment circuit, Prom enable and disable and power on jump reset circuits. Port write :

The four low order bits DØ,D1,D2 and D3 switch the on board memory in 16k banks corresponding to address 0000h-3FFFh,4000H-7FFFH, 8000H-BFFFH and C000-FFFFH on and off. When a particular bank is switched off, external S100 memory can be accessed in that banks address range. This feature allows external memory to be added to the system for multi-user operating systems. Bit D5 of this port switches the on-board EPROM on and off. The onboard EPROM occupies address F000H-FFFFH. The EPROM is switched on automatically during reset or power on, the EPROM contains SIO and FDC initialization code along with a simple debugger and floppy disk cold start loader. After the operating system is loaded the EPROM can be turned off so that the ram at address F000H-FFFFH can be accessed. Bit D6 reset the power on jump circuit. Bit D6 must be set high after a reset or power on situation before ram can be accessed.

| +          | -+- |   | -+- |            | -+- |   | -+- |   | -+- |   | + |   | -+- |    | +                        |

|------------|-----|---|-----|------------|-----|---|-----|---|-----|---|---|---|-----|----|--------------------------|

|            | -   |   | -   |            |     |   |     |   |     |   |   |   |     | DO | •                        |

| +!         |     | ! |     | !          |     | ! |     | ! |     |   |   |   |     | !  |                          |

| · <b>!</b> |     | 1 |     | 1          |     | 1 |     | ! |     | 1 |   | 1 |     | +  | Memory Bank ØØØØH-3FFFH  |

| - 1        |     | 1 |     | · <b>!</b> |     | 1 |     | 1 |     | 1 |   | + |     |    | Memory Bank 4000H-7FFFH  |

| 1          |     | 1 |     | !          |     | ī |     | ! |     |   |   |   |     |    | Memory Bank 8000H-BFFFH  |

| 1          |     | 1 |     | !          |     | ! |     | + |     |   |   |   |     |    | Menory Bank CØØØH-FFFFH  |

| !          |     | ! |     | !          |     | + |     |   |     |   |   |   |     |    | Don't care               |

| 1          |     | 1 |     | +          |     |   |     |   |     |   |   |   |     |    | PROM enable=0, Disable=1 |

| 1          |     | + |     |            |     |   |     |   |     |   |   |   |     |    | Power on jump reset=1    |

| +-         |     |   |     |            |     |   |     |   |     |   |   |   |     |    | Don't care               |

Jumper Definitions

|                                           | Jumper   | Function                                                                     |

|-------------------------------------------|----------|------------------------------------------------------------------------------|

|                                           | <br>А    | CPU clock rate 2mhz/4mhz                                                     |

|                                           | В        | External/Enternal Tx/Rx clock for SIO channel A                              |

|                                           | C        | External/Enternal Tx/Rx clock for SIO channel B                              |

|                                           | D        | Eight inch - five inch Drive selection                                       |

|                                           | E        | Select SlØØ interrupt vector line VIØ OR PINT.                               |

|                                           | P        | Select S100 interrupt vector VIO/PINT or Parallel<br>Port B bit D0 on J2-25. |

|                                           | N        | Port B bit DØ on J2-25.<br>Select S100 interrupt vector VI1 or Parallel      |

|                                           |          | Port B bit D1 on J2-27.                                                      |

| κ.                                        | м        | Select S100 interrupt vector VI2 or Parallel                                 |

|                                           | ••       | Port B bit D2 on $J2-29$ .                                                   |

|                                           | К        | Select S100 interrupt vector VI3 or Parallel                                 |

|                                           |          | Port B bit D3 on $J2-31$ .                                                   |

|                                           | J        | Select S100 interrupt vector V14 or Parallel                                 |

|                                           |          | Port B bit D4 on J2-33.                                                      |

|                                           | н        | Select S100 interrupt vector VI5 or Parallel                                 |

|                                           |          | Port B bit D5 on J2-35.                                                      |

|                                           | G        | Select S100 interrupt vector VI6 or Parallel                                 |

|                                           |          | Port B bit D6 on J2-37.                                                      |

|                                           | F        | Select S100 interrupt vector VI7 or Parallel                                 |

|                                           |          | Port B bit D7 on J2-39.                                                      |

|                                           | R        | Select 2716 or 2732 EPROM.                                                   |

|                                           | S        | Define floppy disk connector for eight ad five inch                          |

| 1. A. |          | drives.                                                                      |

| •                                         | Т        | Enable / Disable S100 bus memory write signal on                             |

|                                           |          | J1 - 68                                                                      |

| 6 9                                       |          | Turney Degarithiens                                                          |

| 6.0                                       |          | Jumper Descriptions                                                          |

|                                           |          | *****************                                                            |

| 6.1                                       | A        | CPU clock rate 2mhz/4mhz                                                     |

|                                           |          | ermines the cpu clock rate.                                                  |

|                                           |          | ocated below IC U7.                                                          |

| The Juli                                  | ber 19 1 | · · · · · · · · · · · · · · · · · · ·                                        |

|                                           |          | +++                                                                          |

|                                           |          | 1 1 1 2 1 3 1                                                                |

|                                           |          | ++++                                                                         |

| Install                                   | Plug be  | tween posts 1 & 2 for 4mhz operation.                                        |

|                                           | -        | •                                                                            |

| Install                                   | Plug be  | tween posts 2 & 3 for 2mhz operation.                                        |

| 6.2                                       | В        | External/internal Tx/Rx clock for SIO channel A                              |

|                                           |          |                                                                              |

Jumper B connects the SIO channel A to either the internal baud rate generator or to the connector  $J_A^5$  pin 9 for use in sycronous applications.

15

5.0

! 1 ! Connector J5 pin 9

+---+

! 2 ! SIO Tx/Rx clock input

+---+

.! 3 ! Baud rate generator channel A

+---+

Install Plug between posts 1 & 2 for external SIO clock. Install Plug between posts 2 & 3 for Baud rate generator.

6.3 C External/internal Tx/Rx clock for SIO channel B Jumper C connects the SIO channel B to either the internal baud rate generator or to connector J5 pin 9 for use in sycronous applications. Jumper C is located near J5.

! 1 ! Connector J5 pin 9

+---+

! 2 ! SIO Tx/Rx clock input

+---+

! 3 ! Baud rate generator channel B

+---+

Install Plug between posts 1 & 2 for external SIO clock. Install Plug between posts 2 & 3 for Baud rate generator.

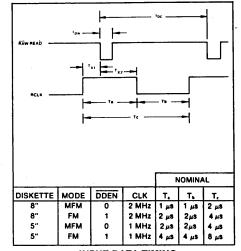

6.4 D Eight inch – five inch Drive selection Jumper D is located near IC U2.

+---+

' 6 ! 8 inch floppy clock source

+---+

' 5 ! FDC clock input

+---+

! 4 ! 5.25 inch floppy clock source

+---+

! 3 ! 5.25 head load/motor

+---+

' 2 ! Head load source

+---+

' 1 ! 8 inch head load

+---+

Install Plug between posts 1 & 2 and 5 & 6 for 8 drives. Install Plug between posts 2 & 3 and 4 & 5 for 5.25 inch drives.

Note : There are other board modifications needed to interface the FDC to a 5.25 inch drive.

6.5 E Select SlØØ interrupt vector line VIØ OR PINT. Jumper E selects the interrupt line to be used when channel B bit DØ is programmed for interrupts.

Jumper E is located below IC U8.

+---+ ! 1 ! 2 ! 3 ! +---+--+

Install Plug between posts 1 & 2 for VIØ interrupt pin. (J1-4) Install Plug between posts 2 & 3 for PINT interrupt pin. (J1-73)

6.6 𝒴 ⊨ Select S100 interrupt vector VIO/PINT or Parallel Port B bit DØ on J2-25.

This jumper is located near connector J2.

! 1 ! 2 ! 3 ! +---+---+

Install Plug between posts 1 & 2 to connect the PIO bit DØ to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit DØ to the jumper selector area E, VIØ/PINT (when the PIO bit is programmed for interrupt mode).

6.7 NG Select S100 interrupt vector V11 or Parallel Port B bit D1 on J2-27. This jumper is located near connector J2. +---+-------+ ! 1 ! 2 ! 3 ! +---+---+

Install Plug between posts 1 & 2 to connect the PIO bit Dl to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit Dl to the vectored interrupt line VII (when the PIO bit is programmed for interrupt mode).

6.8 MH Select S100 interrupt vector VI2 or Parallel Port B bit D2 on J2-29. This jumper is located near connector J2. +---+------+ ! 1 ! 2 ! 3 ! +---+---+---+ Install Plug between posts 1 & 2 to connect the PIO bit D2 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D2 to the vectored interrupt line VI2 (when the PIO bit is programmed for interrupt mode). 6.9 ΚJ Select S100 interrupt vector VI3 or Parallel Port B bit D3 on J2-31. This jumper is located near connector J2. ! 1 ! 2 ! 3 ! +---+--+--+ Install Plug between posts 1 & 2 to connect the PIO bit D3 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D3 to the vectored interrupt line VI3 (when the PIO bit is programmed for interrupt mode). 6.10 JK Select Sl00 interrupt vector VI4 or Parallel Port B bit D4 on J2-33. This jumper is located near connector J2. +---+-1-4---+ 112131 +---+--+ Install Plug between posts 1 & 2 to connect the PIO bit D4 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D4 to the vectored interrupt linr VI4 (when the PIO bit is programmed for interrupt mode).

6.11 AT M Select S100 interrupt vector VI5 or Parallel Port B bit D5 on J2-35.

This jumper is located near connector J2.

```

/-F-7

+---+--+--+--+

! 1 ! 2 ! 3 !

+---+--+--+

```

Install Plug between posts 1 & 2 to connect the PIO bit D5 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D5 to the vectored interrupt line V15 (when the PIO bit is programmed for interrupt mode). 6.12 ØN Select S100 interrupt vector VI6 or Parallel Port B bit D6 on J2-37. This jumper is located near connector J2. ! 1 ! 2 ! 3 ! +---+---+ Install Plug between posts 1 & 2 to connect the PIO bit D6 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D6 to the vectored interrupt line VI6 (when the PIO bit is programmed for interrupt mode). 6.13 р Select S100 interrupt vector VI7 or Parallel Port B bit D7 on J2-39. This jumper is located near connector J2. +---+------+ ! 1 ! 2 ! 3 ! ---+ Install Plug between posts 1 & 2 to connect the P10 bit D7 to J2 pin 25 (when the PIO bit is programmed for input/output). Install Plug between posts 2 & 3 to connect the PIO bit D7 to the vectored interrupt line VI7 (when the P10 bit is programmed for interrupt mode).

6.14 R Select 2716 or 2732 EPROM.

Jumper R configures the board to accept a 2716 or 2732 EPROM.

Jumper R is located near the 280 chip.

+---+ ! 1 ! Address line All +---+ ! 2 ! EPROM input +---+ ! 3 ! +5 volts +---+

Install Plug between posts 1 & 2 for a 2732 EPROM. Install Plug between posts 2 & 3 for a 2716 EPROM. Note : The EPROM is always addressed at F800H and can not be moved. Since the 2716 EPROM is 2K long it appears twice , F800H-FC00H and FBFFH-FFFFH.

6.15 S Define floppy disk connector for eight, five inch drives and FDC chip type.

This jumper is located U26. 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 : 3 : 1 : 2 :1 : 1 : 1 : 2 :

For 8" set-up plug the following jumpers: 1to4,2to3,5to6,7to8.

For 5 1/4" plug the following jumpers: lto2,5to8,6to9,7to10,11to12.(see factory installed jumpers for additional jumpers or changes.)

+---+

6.16 T Enable / Disable SlØØ bus memory write signal on J1 - 68 This jumper is located near Ul8.

+-----+ 1 1 1 2 1

Install Plug between posts 1 & 2 to connect the memory write signal (MEMWR) to the S100 bus pin 68.

7.Ø Baud Rate Switch

The baud rate of the two serial channels can be select separately by setting the baud rate switch. The baud rate switch is an 8 pole switch located near U54. It is split into two sections. Switches 1,2,3,4 set the baud rate for the SIO channel B and switches 5,6,7,8 set the baud rate for the SIO channel A.

|     | ++                              | OFF | (up)   |

|-----|---------------------------------|-----|--------|

| SW1 | 18171615141312111               |     |        |

|     | ++                              | ON  | (down) |

|     | <- Channel B -> <- Channel A -> |     |        |

7.1 Baud rate switch setting

|    | Switcł<br>Switcł |        |     |        |        | Channel<br>Channel |     |        |   |  |

|----|------------------|--------|-----|--------|--------|--------------------|-----|--------|---|--|

|    |                  | <br>on | on  | <br>on | <br>on | <br>5Ø             |     |        |   |  |

|    |                  |        | on  |        | on     | 75                 |     |        |   |  |

|    |                  |        |     | on     |        | 110                |     |        |   |  |

|    |                  |        |     | on     |        | 134                |     | 5      |   |  |

|    |                  |        |     | off    |        | 150                |     |        |   |  |

|    |                  |        |     | off    |        | 300                |     |        |   |  |

|    |                  | on     | off | off    | on     | 600                |     |        |   |  |

|    |                  | off    | off | off    | on     | 120                |     |        |   |  |

|    |                  | on     | on  | on     | off    | 180                | ØØ  |        |   |  |

|    |                  | off    | on  | on     | off    | 200                | ØØ  |        |   |  |

|    |                  | on     | off | on     | off    | 240                | ØØ  |        |   |  |

|    |                  | off    | off | on     | off    | 366                | ØØ  |        |   |  |

|    |                  | on     | on  | off    | off    | 480                | ØØ  |        |   |  |

|    |                  | off    | on  | off    | off    | 720                | ØØ  |        |   |  |

|    |                  | on     | off | off    | off    | 966                | ΰØ  |        |   |  |

|    |                  | off    | off | off    | off    | 19,                | ,20 | Ø      |   |  |

| or | exact            | baud r | ate | frec   | uenci  | es see A           | \pr | pendix | D |  |

For exact baud rate frequencies see Appendix D

# 8.Ø External Connector Pin definitions

.

8.1 Connector J1 - S100 bus connector

| PIN#  | NAME          | PIN #     | NAME        |

|-------|---------------|-----------|-------------|

| 1     | +8V           | 51        | +8V         |

| 2     | +16V          | 52        | -16V        |

| 3     | XRDY          | 53        | GND         |

| 4     | VIØ*          | 54        | SLAVE CLR*  |

| 5     | VIl*          | 55-57     | DMAO*-DMA2* |

| 6     | VI2*          | 58        | SXTRQ*      |

| 7     | VI3*          | 59        | A19         |

| 8     | VI4*          | 60        | SIXTN*      |

| 9     | V15*          | 61-64     | A2Ø-A23     |

| 10    | VI6*          | 65,65     | NDEF        |

| 11    | V17*          | 67        | PHANTOM*    |

| 12    | NMI*          | 68        | MWRT        |

| 13    | PWRFAIL*      | 69        | RFU         |

| 14    | DMA3*         | 7Ø        | GND         |

| 15    | A18           | 71        | RFU         |

| 16    | A17           | 72        | RDY         |

| 17    | A16           | 73        | INT*        |

| 18    | SDSB*         | 74        | HOLD*       |

| 19    | CDSB*         | 75        | RESET*      |

| 20    | GND           | 76        | PSYNCH      |

| 21    | NDEF          | 77        | PWR*        |

| 22    | ADSB*         | 78        | PDBIN       |

| 23    | DODSB*        | 79-87     | AØ-A11      |

| 24    | Ø             | 88-95     | DO2-DIØ     |

| 25    | PSTVAL*       | 96        | SINTA       |

| 26    | PHLDA         | 97        | SWO*        |

| 27,28 | RFU           | 98        | ERROR*      |

| 29-34 | A5, A4, A3, A | 15,A12,A9 |             |

| 35    | DO1/DATA 1    | 99        | POC*        |

| 36    | DOØ/DATA Ø    | 100       | GND         |

| 37    | AlØ           |           |             |

| 38    | D04           |           |             |

| 39    | D05           |           |             |

| 40-43 | DO6,DI2,DI    | 3,DI7     |             |

| 44    | SMI           |           |             |

| 45    | SOUT          |           |             |

| 46    | SINP          |           |             |

| 47    | SMEMR         |           |             |

| 48    | SHLTA         |           |             |

| 49    | CLOCK         |           |             |

| 50    | GND           |           |             |

8.2 Connector J2 - Parallel port connector

\*

\*

\*

\*

ャ

\*

\*

\*

| 1  | ARDY      |             | А | ready signal |

|----|-----------|-------------|---|--------------|

| 2  | ARDY RET  | ground      |   |              |

| 3  | ASTRB*    | PIO Channel | А | strobe       |

| 4  | ASTRB RET | ground      |   |              |

| 5  | PAØ       | PIO Channel | А | data bit DØ  |

| 6  | PAØ RET   | ground      |   |              |

| 7  | PAl       | PIO Channel | А | data bit Dl  |

| 8  | PAl RET   | ground      |   |              |

| 9  | PA2       |             | А | data bit D2  |

| 10 | PA2 RET   | ground      |   |              |

| 11 | PA3       | PIO Channel | А | data bit D3  |

| 12 | PA3 RET   | ground      |   |              |

| 13 | PA4       |             | А | data bit D4  |

| 14 | PA4 RET   | ground      |   |              |

| 15 | PA5       | PIO Channel | А | data bit D5  |

| 16 | PA5 RET   | ground      |   |              |

| 17 | PAG       | PIO Channel | А | data bit D6  |

| 18 | PA6 RET   | ground      |   |              |

| 19 | PA7       | PIO Channel | А | data bit D7  |

| 20 | PA7 RET   | ground      |   |              |

| 21 | BRDY      |             | В | ready signal |

| 22 | BRDY RET  | ground      |   |              |

| 23 | BSTRB*    | PIO Channel | В | strobe       |

| 24 | BSTRB RET | grounď      |   |              |

| 25 | PBØ       |             | В | data bit DØ  |

| 26 | PBØ RET   | ground      |   |              |

| 27 | PBl       |             | В | data bit Dl  |

| 28 | PB1 RET   | ground      |   |              |

| 29 | PB2       |             | В | data bit D2  |

| 30 | PB2 RET   | ground      |   |              |

| 31 | PB3       | PIO Channel | В | data bit D3  |

| 32 | PB3 RET   | ground      |   |              |

| 33 | PB4       | PIO Channel | В | data bit D4  |

| 34 | PB4 RET   | ground      |   |              |

| 35 | PB5       |             | В | data bit D5  |

| 36 | PB5 RET   | ground      |   |              |

| 37 | PB6       | PIO Channel | В | data bit D6  |

|    |           |             |   |              |

| 38 | PB6 RET   | ground      |   |              |

| 39 | PB7       | PIO Channel | В | data bit D7  |

| 4Ø | + 5 VOLTS |             |   |              |

|    |           |             |   |              |

\* Note : These pins can can be jumpered to the S100 bus vectored interrupt lines.

8 inch 5.25 inch

| $\begin{array}{c}1\\2\\3\\4\\5\\6\\7\\8\\9\\1\\1\\2\\1\\3\\1\\4\\1\\5\\1\\7\\8\\9\\0\\1\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2\\2$ | $     \begin{array}{c}       1 \\       2 \\       3 \\       4 \\       5 \\       6 \\       7 \\       8 \\       9 \\       10 \\       11 \\       12 \\       13 \\       14 \\       15 \\       16 \\       17 \\       18 \\       19 \\       20 \\       21 \\       22 \\       23 \\       24 \\       25 \\       26 \\       27 \\       28 \\       29 \\       30 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       33 \\       31 \\       32 \\       31 \\       32 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       31 \\       32 \\       31 \\       31 \\       32 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       32 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31 \\       31$ | ground<br>Alternate Head 2*<br>ground<br>N/C<br>ground<br>N/C<br>ground<br>N/C<br>ground<br>N/C<br>ground<br>Head 2*<br>ground<br>Head 2*<br>ground<br>Head load*<br>ground<br>Head load*<br>ground<br>Index*<br>ground<br>Above Track 43*<br>ground<br>Drive select 0*<br>ground<br>Drive select 1*<br>ground<br>Drive select 1*<br>ground<br>Drive select 2*<br>ground<br>Drive select 2*<br>ground<br>Drive select 3*<br>ground<br>Drive select 3*<br>ground<br>Direction<br>ground<br>Step*<br>ground<br>Write Data*<br>ground<br>Write gate*<br>ground<br>Write protect*<br>ground<br>Write protect*<br>ground<br>Motor on*<br>ground |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49                                                                                                                                             | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5Ø                                                                                                                                             | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

4 Connector J4 - Serial port Channel A

|    |           | •                              |

|----|-----------|--------------------------------|

| 1  | N/C       |                                |

| 2  | DCDA*     | Data Carrer Detect Channel A * |

| 3  | SYNCA*    | Sync Detect                    |

| 4  | RxDA      | Receive data                   |

| 5  | CTSA*     | Clear to send                  |

| 6  | TxDA      | Transmit data                  |

| 7  | RTSA*     | Request to send                |

| 8  | DTRA*     | Data terminal ready            |

| 9  | Tx/RxCA*  | Transmitt / receive clock      |

| 10 | GND       |                                |

| 11 | N/C       |                                |

| 12 | +16 VOLTS |                                |

| 13 | -16 VOLTS |                                |

| 14 | +5 VOLTS  |                                |

|    |           |                                |

8.5 Connector J5 - Serial port Channel B

| 1  | N/C       |                                |

|----|-----------|--------------------------------|

| 2  | DCDA*     | Data Carrer Detect Channel A * |

| 3  | SYNCA*    | Sync Detect                    |

| 4  | RxDA      | Receive data                   |

| 5  | CTSA*     | Clear to send                  |

| 6  | TXDA      | Transmit data                  |

| 7  | RTSA*     | Request to send                |

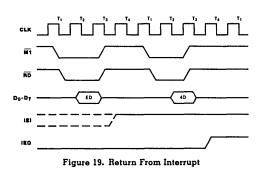

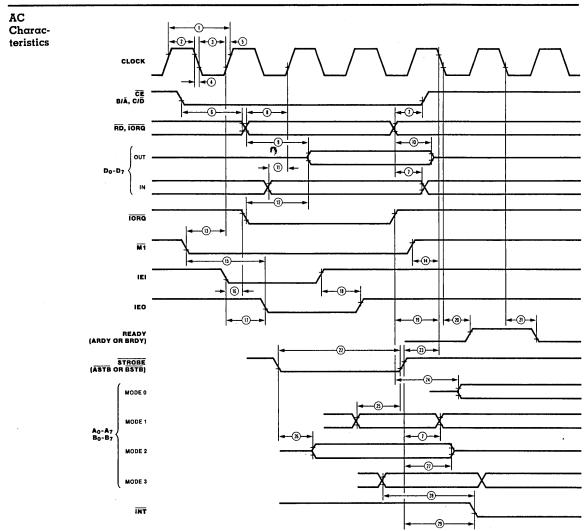

| 8  | DTRA*     | Data terminal ready            |