THEORY of OPERATION & SIMPLIFIED DRAWINGS for

# CONTROL DATA° G-15 COMPUTER

|            | Record of Revisions |

|------------|---------------------|

| REVISION   | NOTES               |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

| <b>***</b> |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

| _          |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

|            |                     |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in back of this manual.

# PART I - THEORY OF OPERATION

## PREFACE

This manual is designed to clarify the internal logic and circuitry of the G-15. It presents both theory of operation (Part I) and simplified drawings (Part II) to illustrate the reasoning behind the circuits.

While the material presented assumes some familiarity with the G-15 as well as knowledge of Binary Arithmetic and Boolean Algebra, outlines of fundamental operations are provided in the APPENDIX, along with two fundamental test routines.

# TABLE OF CONTENTS

|          | 3 · · · · · · · · · · · · · · · · · · · |                                                |

|----------|-----------------------------------------|------------------------------------------------|

| PAGE NO. | SEC. NO.                                | TITLE                                          |

| 1        | : <u>A</u>                              | SECTION A: FUNDAMENTAL CIRCUITS                |

| _        | 、北                                      |                                                |

| 2        | A-1                                     | "OR" GATES                                     |

| 3        | A-2                                     | "AND" GATES                                    |

| 4        | A-3                                     | "AND" GATES and "OR" GATES - COUPLING          |

| 5        | A-4                                     | CATHODE-FOLLOWERS                              |

| 6        | A-5                                     | BUFFER-INVERTERS                               |

| 7        | A-6                                     | FLIP-FLOPS                                     |

| 9        | A-7                                     | MEMORY LINES                                   |

| 12       | A-8                                     | THE MEMORY                                     |

| 13       | A-9                                     | PHYSICAL LOCATION OF LOGICAL CIRCUITS          |

| 14       | A-10                                    | MISCELLANEOUS                                  |

| 15       | <u>B</u>                                | SECTION B: BASIC TIMING                        |

| 16       | B-1                                     | G-15D IN GENERAL                               |

| 16       | B-2                                     | TIMING SUBDIVISIONS                            |

| 17       | B-3                                     | WRITE PULSE, CLOCK, READ CLOCK - UNCONDITIONAL |

| 19       | B-4                                     | SHIFT PULSE - CONDITIONAL                      |

| 19       | B-5                                     | TIMING PULSES - THE TIMING TRACK (TM)          |

| 19       | B-6                                     | WORD-TIME INFORMATION - THE NUMBER TRACK (CN)  |

| 21       | С                                       | SECTION C: GENERAL COMPUTER ACTIVITY           |

| 22       | C-1                                     | COMPUTER SEQUENCE OF ACTIVITY                  |

| 22       | C-2                                     | COMMANDS                                       |

| 23       | C-3                                     | NUMBERS                                        |

| 26       | C-4                                     | SOURCES and DESTINATIONS IN GENERAL            |

| 27       | C-5                                     | THE CONTROL SWITCH                             |

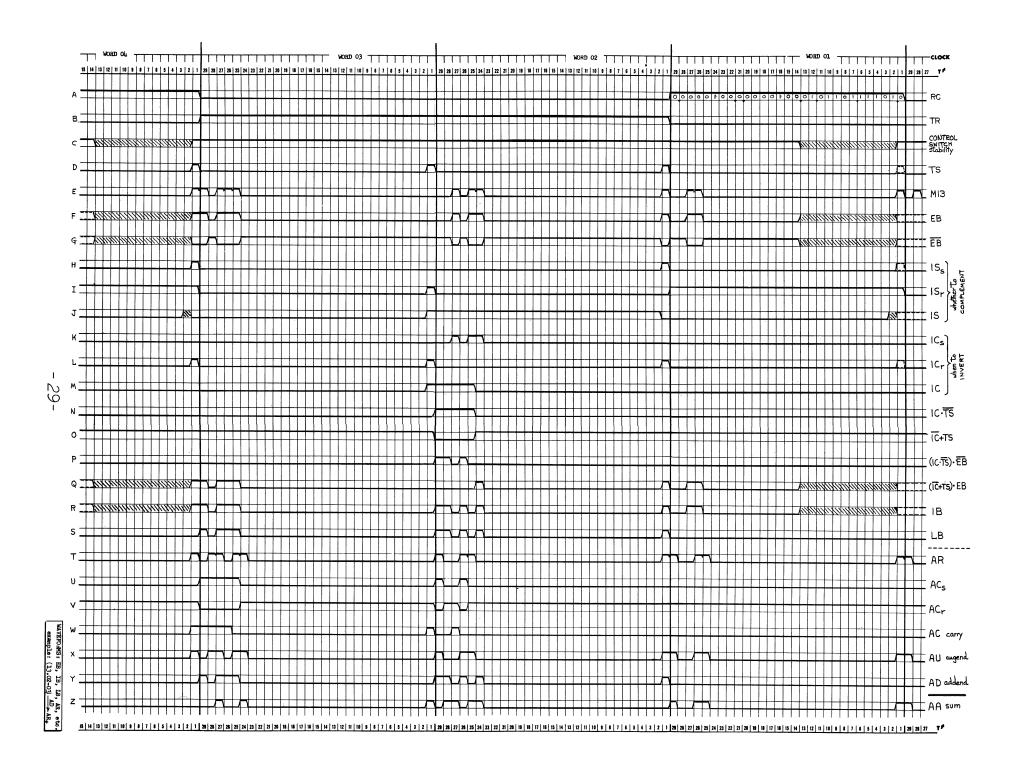

| 28       | C-6                                     | TRANSFER TIMING                                |

| 29       | C-7                                     | THE INVERTING GATES (EB→IB)                    |

| 30       | C-8                                     | IB→LB                                          |

| 30       | C-9                                     | EXECUTION OF A SAMPLE COMMAND                  |

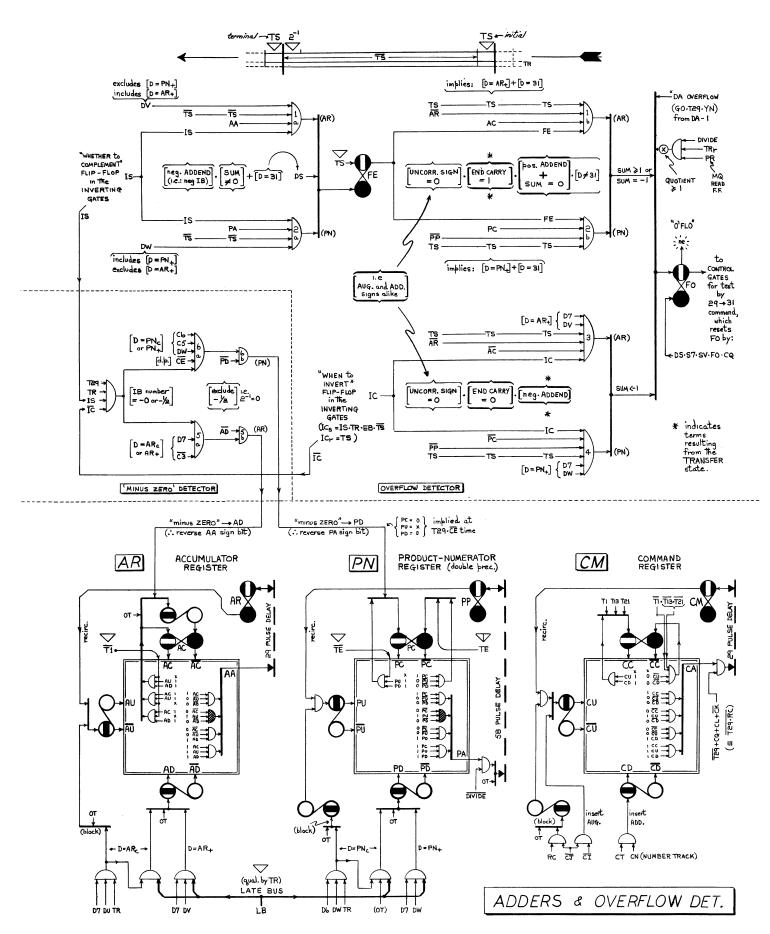

| 32       | C-10                                    | ADDERS                                         |

| 36       | C-11                                    | OVERFLOW DETECTOR (FO)                         |

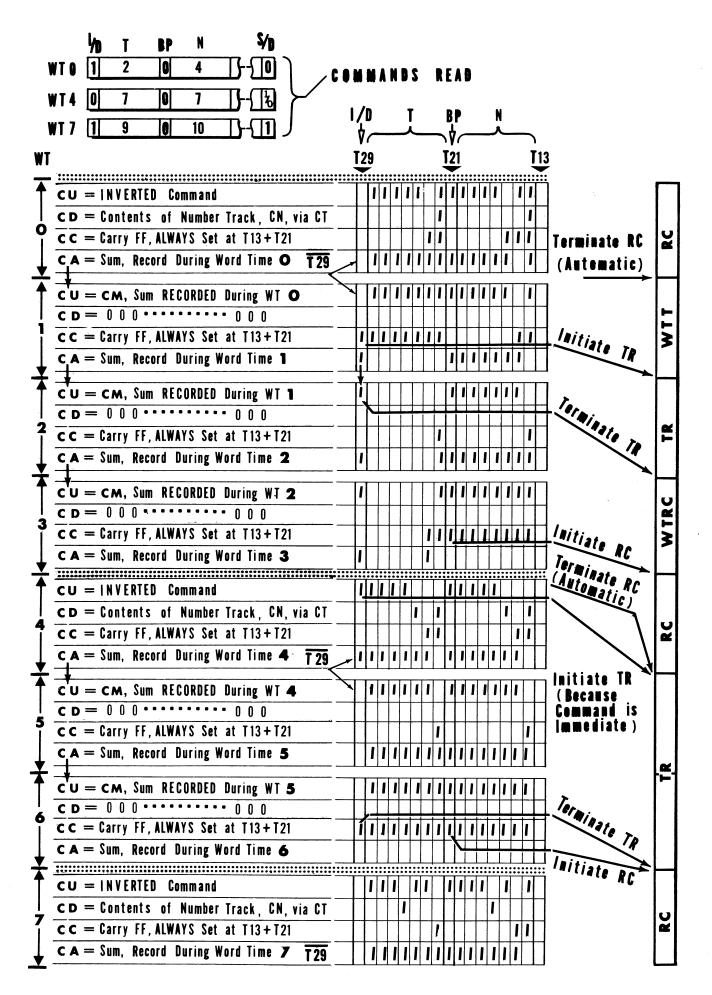

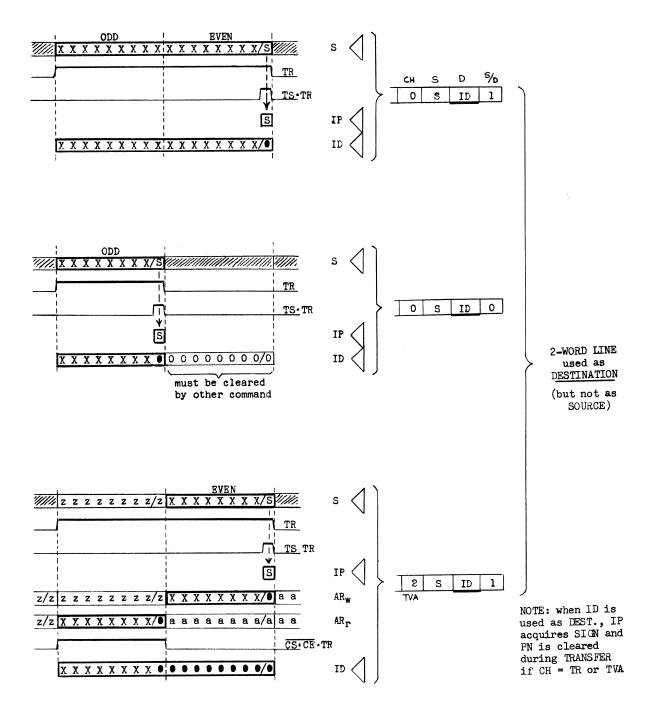

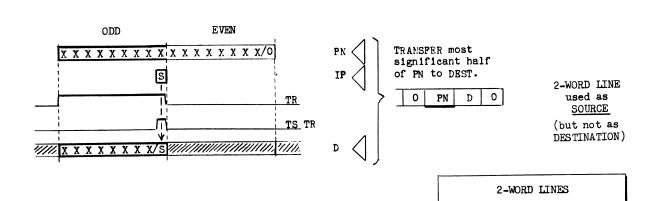

| 37       | C-12                                    | THE TWO-WORD LINES: ID, MQ, and PN             |

| 38       | C-13                                    | THE IP FLIP-FLOP                               |

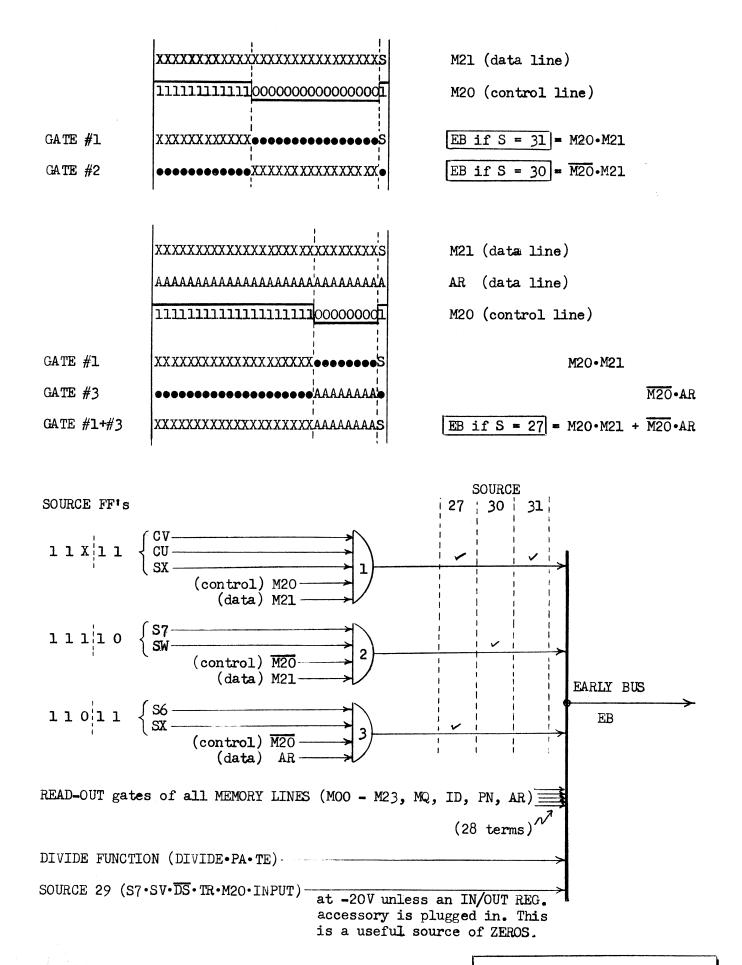

| 39       | C-14                                    | THE "LOGICAL" SOURCES and SOURCE 29            |

| 39       | C-15                                    | THE FOUR-WORD LINES (M20 - M23)                |

| 39       | C-16                                    | SOURCE and DESTINATION RESTRICTIONS            |

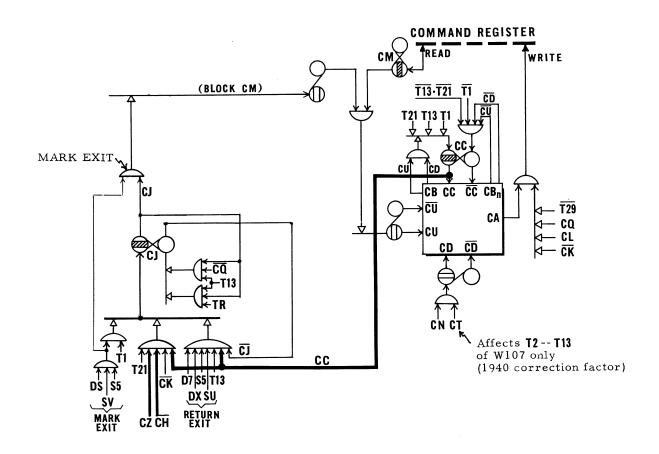

| 40       | C-17                                    | THE COMMAND REGISTER                           |

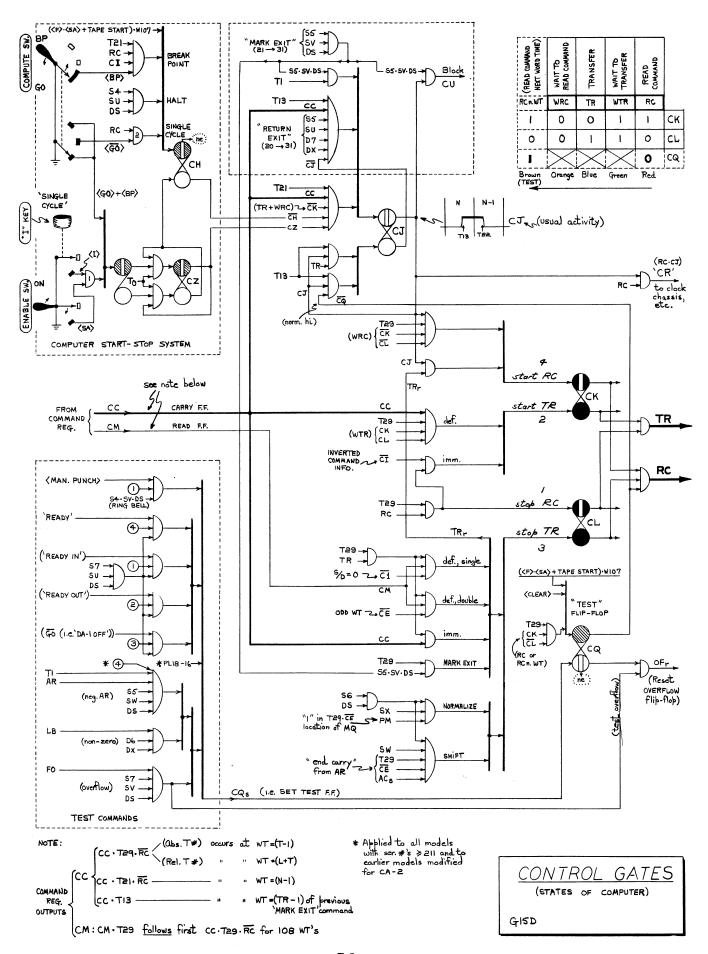

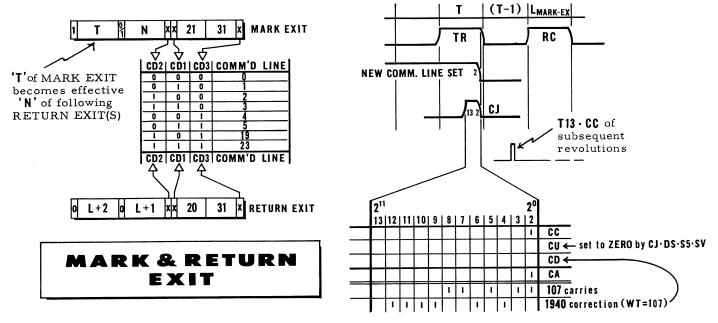

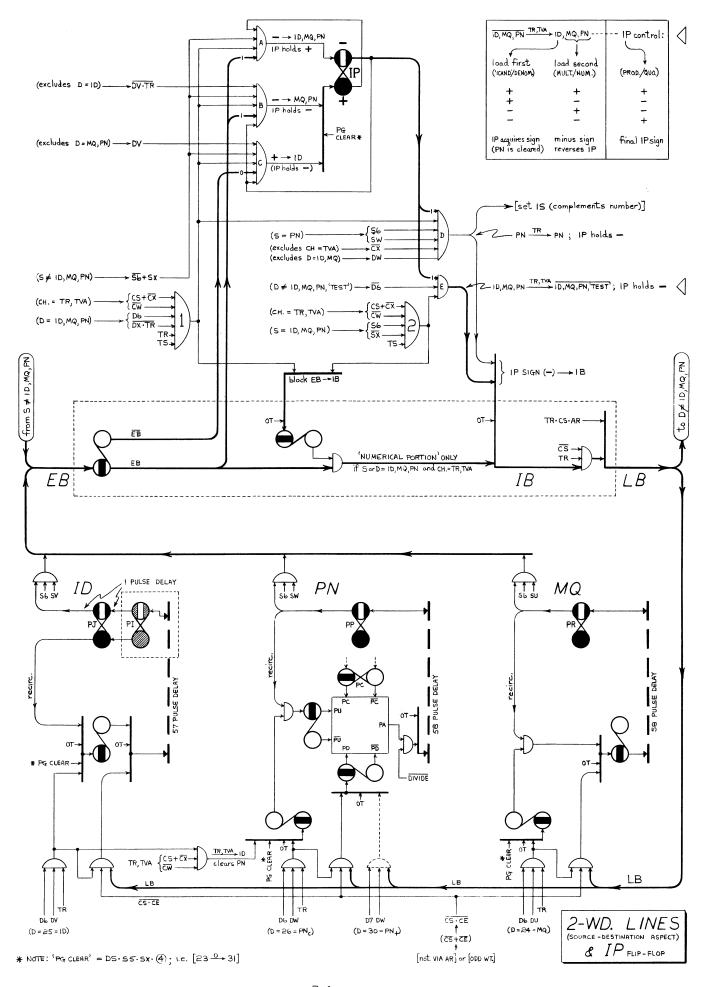

| 45<br>45 | C-18                                    | RC - WTR - TR - WRC CONTROL                    |

| 47       | C-19                                    | THE "WRC NEXT WT" STATE (TEST COMMANDS)        |

| 47       | C-20                                    | COMPUTER START-STOP                            |

| 48       | C-21                                    | DESTINATION 27: TEST (NON-ZERO)                |

| 49       | D                                       | SECTION D: THE SPECIAL COMMANDS                |

| 50       | D-1                                     | THE SPECIAL COMMANDS - GENERAL                 |

| 50       | D-2                                     | SOURCE 16: HALT                                |

| 50       | D-3                                     | SOURCE 17: RING BELL, ETC.                     |

```

SOURCE 18: TRANSFER M20 · ID to OUTPUT REGISTER

51

D-4

SOURCE 19: DA-1 CONTROL

D-5

51

SOURCES 20 and 21: MARK EXIT AND RETURN EXIT

51

D-6

53

D-7

SOURCE 22: SIGN OF AR to TEST

SOURCE 23 · CH=0: CLEAR MQ, ID, PN, AND IP FLIP-FLOP

53

D-8

SOURCE 23 · CH=3: PN·M2 to ID and PN·\overline{\text{M2}} to PN

53

D-9

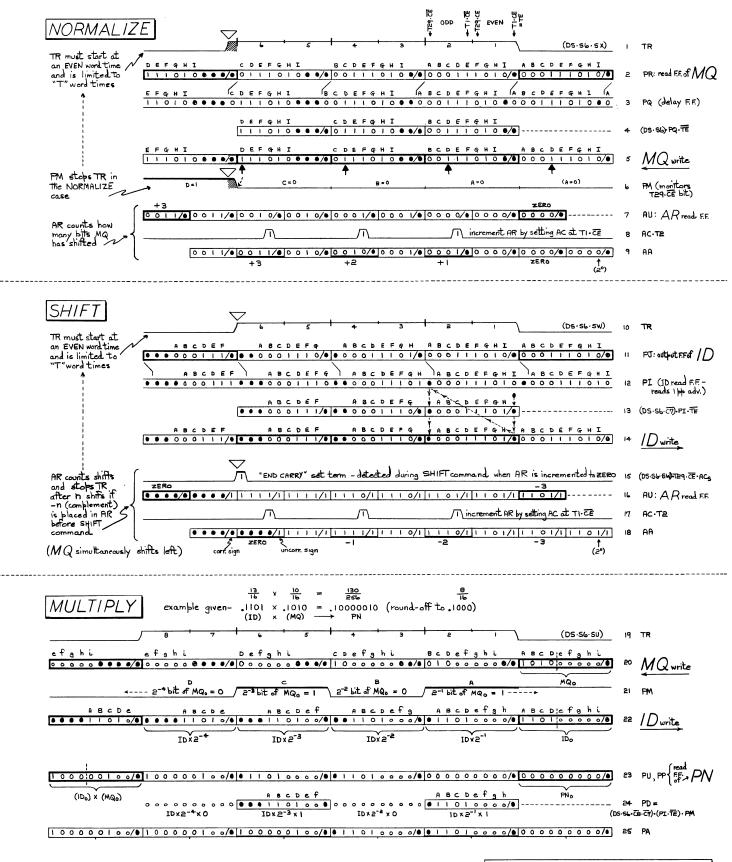

SOURCE 24: MULTIPLY

53

D-10

55

D-11

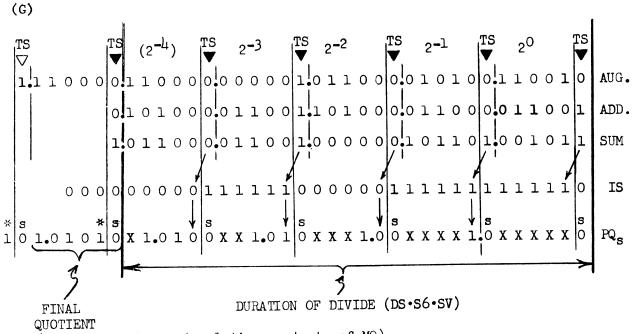

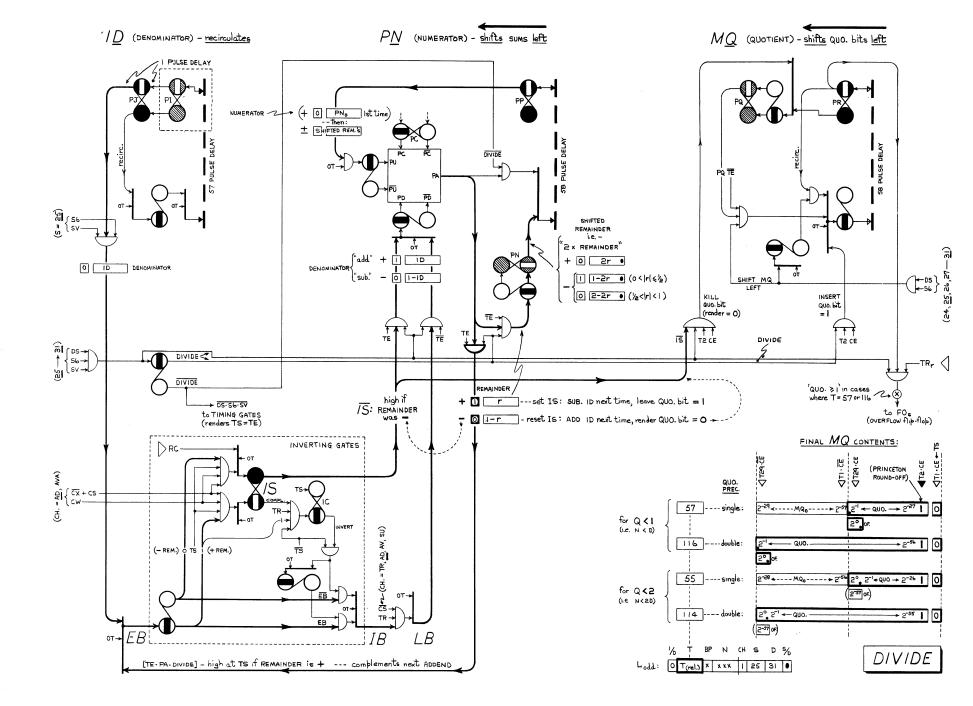

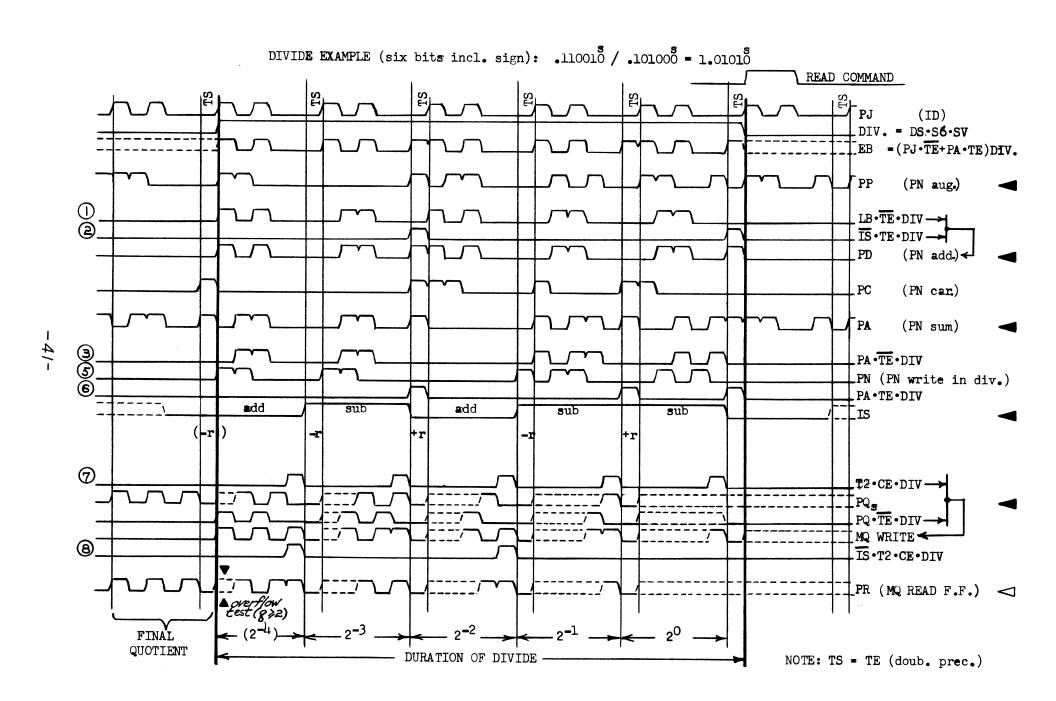

SOURCE 25: DIVIDE

SOURCE 26: SHIFT MO LEFT AND ID RIGHT

59

D-12

60

D-13

SOURCE 27: NORMALIZE MQ

SOURCES 28 and 29: TEST COMMANDS

61

D-14

61

(SOURCE 30: MAGNETIC TAPE WRITE FILE CODE)

D-15

62

D-16

SOURCE 31 · CH=0: NEXT COMMAND FROM AR

SOURCE 31 CH=1: TRANSFER NT to LINE 18

62

D-17

D-18

"DO NOTHING" COMMANDS

62

63

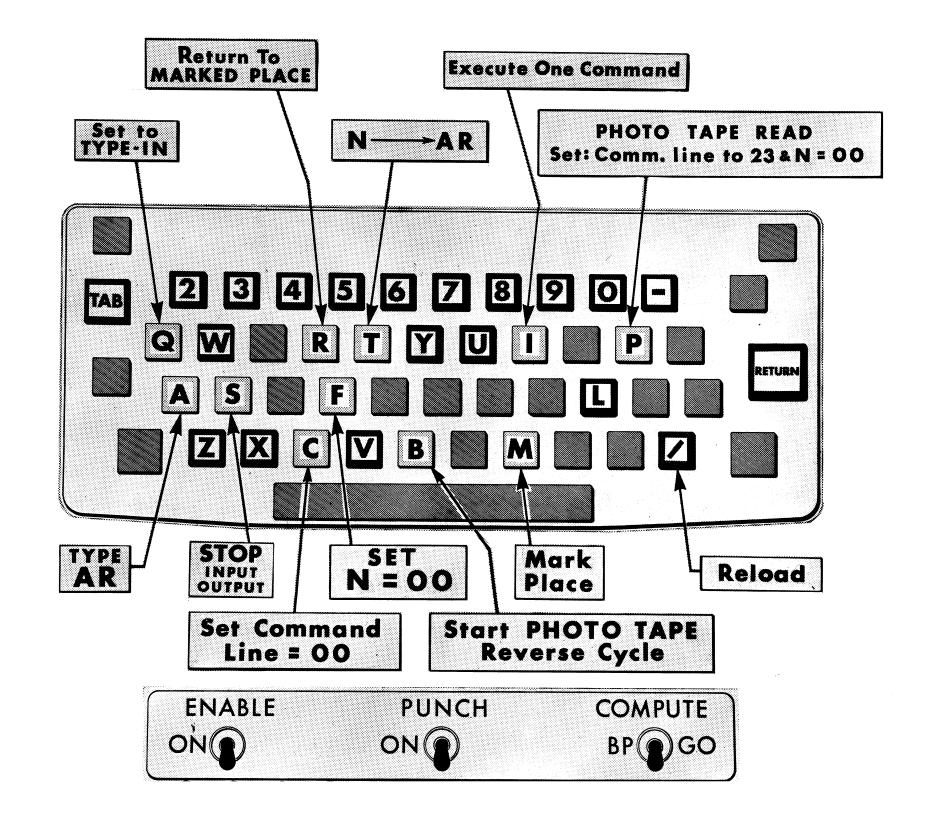

SECTION E: MANUAL CONTROLS

E

E-1

64

MANUAL CONTROLS - GENERAL

E-2

THE ENABLE SWITCH - (SA)

64

64

E-3

THE PUNCH SWITCH - (MAN PUNCH)

THE COMPUTE SWITCH - \langle \overline{GO} \rangle, \langle GO \rangle, and \langle BP \rangle

64

E-4

65

E-5

"I" KEY - SINGLE CYCLE - <I>

"C" KEY - SET COMMAND LINE = 00 - (C)

65

E-6

"1" - "7" KEYS - SET COMMAND LINE

65

E-7

"F" KEY - SET "N" = 00 - \langle F \rangle

66

E-8

"M "and "R" KEYS - MARK and RETURN - (M) and (R)

66

E-9

"T" KEY - "N" to AR - <T>

67

E-10

"A", "Q", "P", "B", and "S" KEYS - INPUT/OUTPUT

67

E-11

LOGIC PUSH-BUTTON MAINTENANCE SWITCHES

68

E-12

69

F

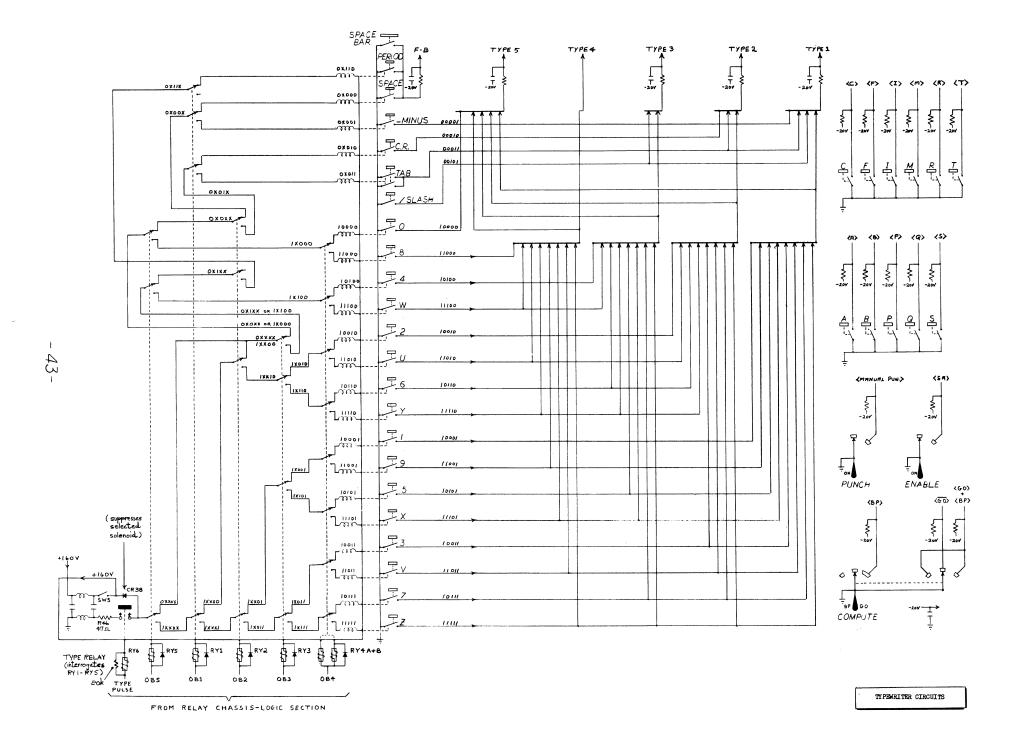

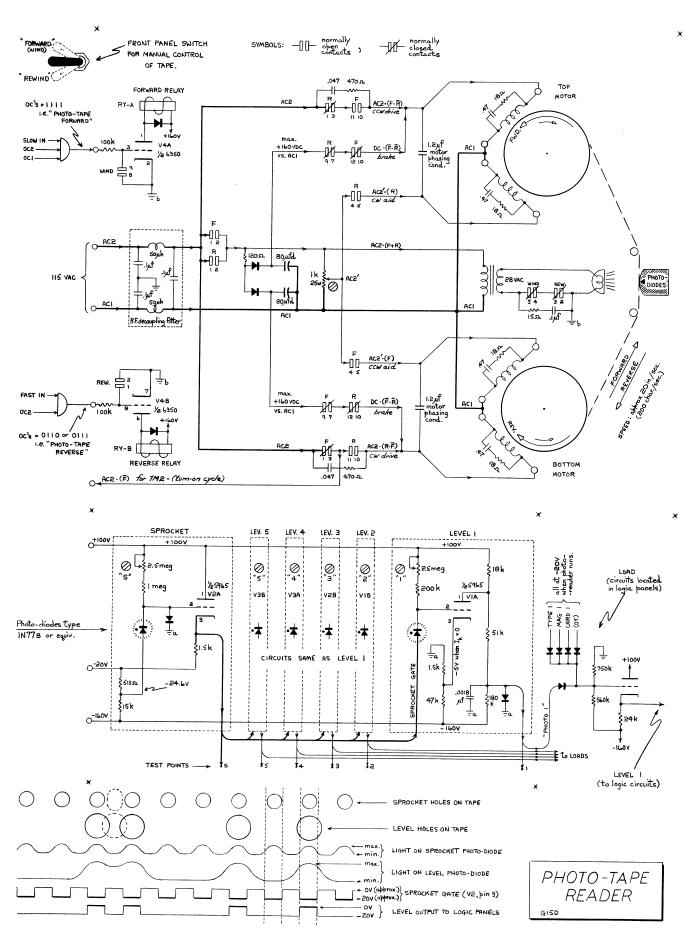

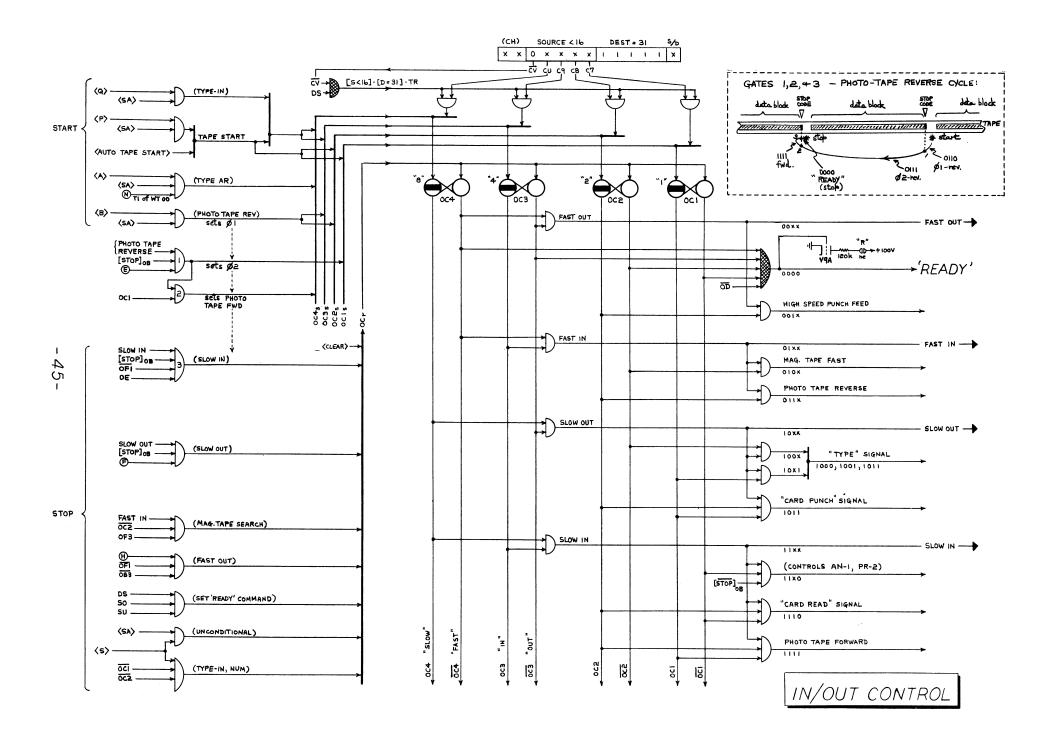

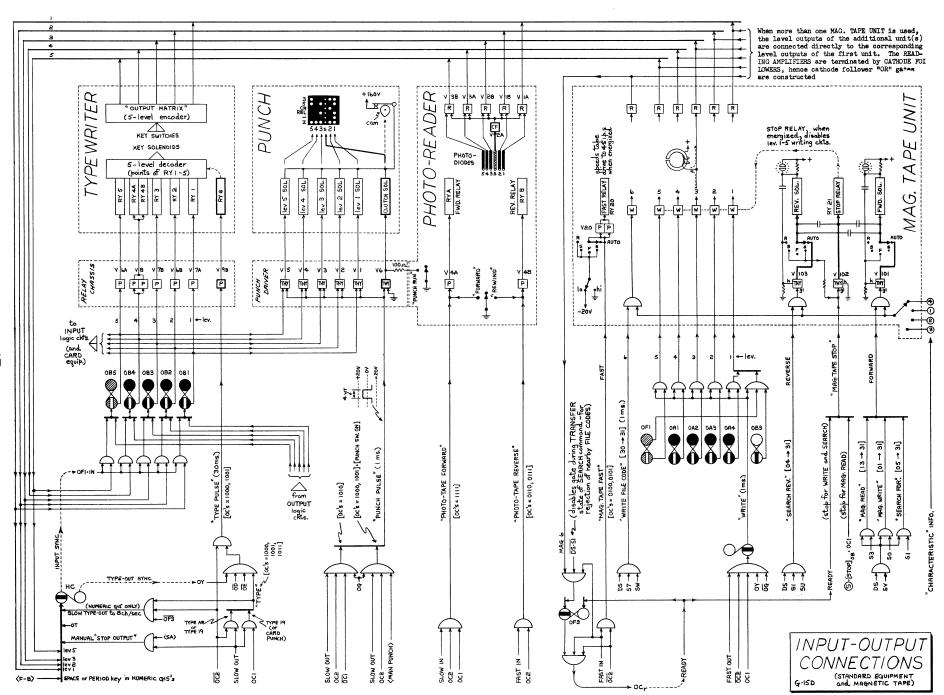

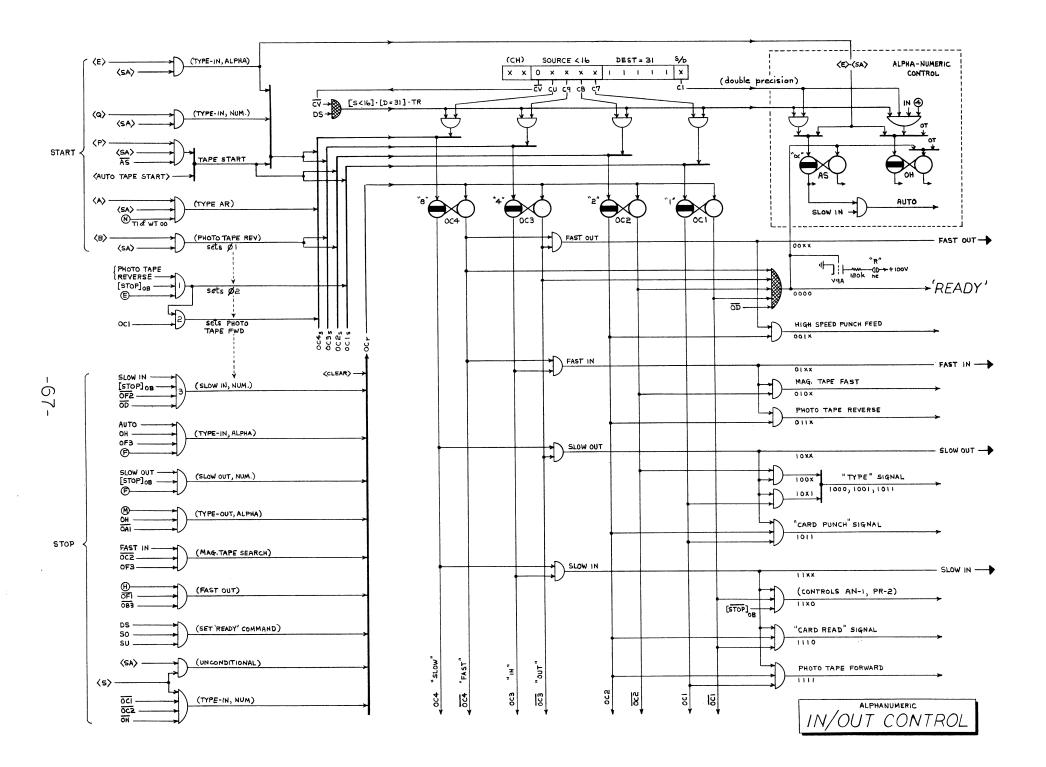

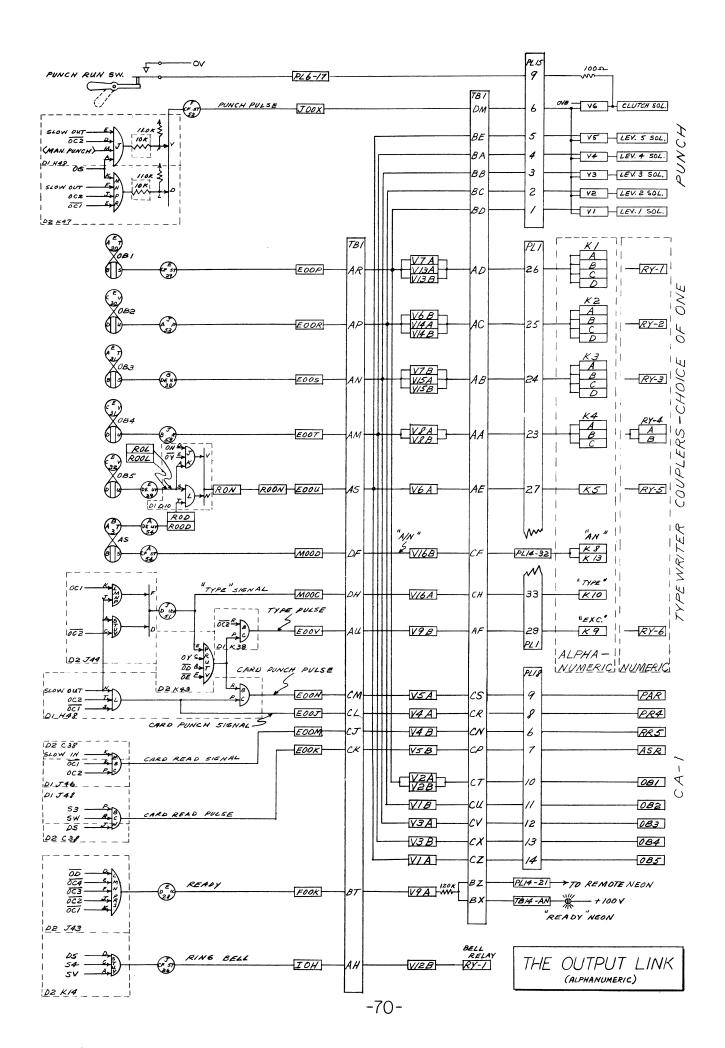

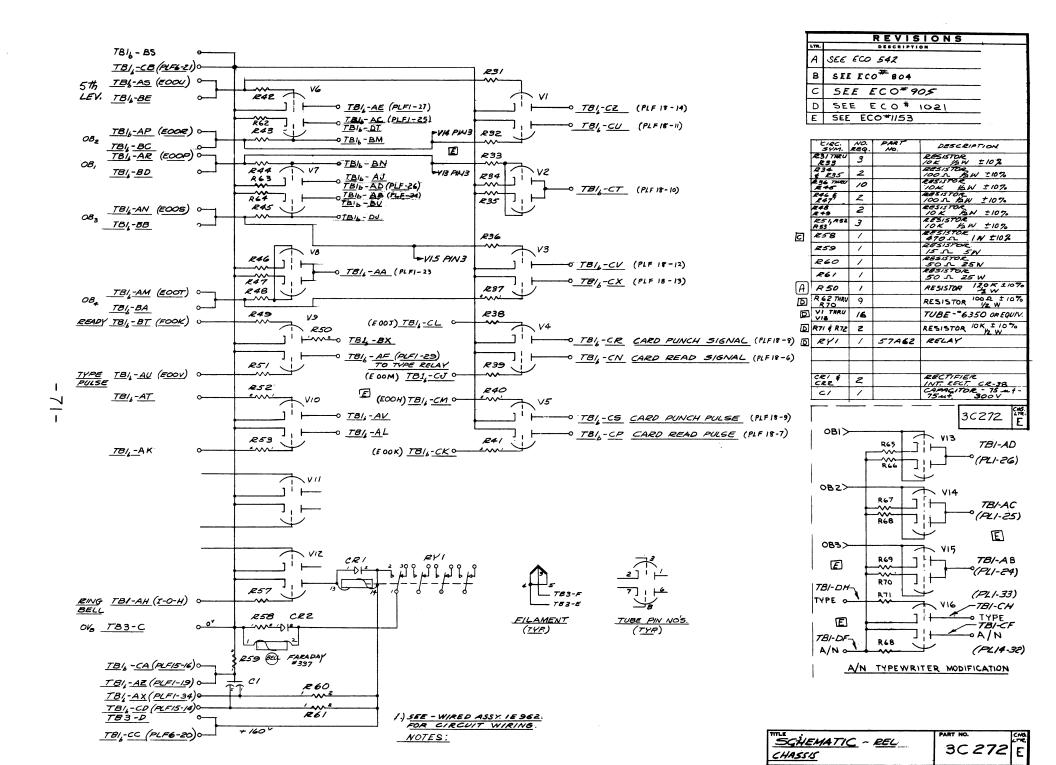

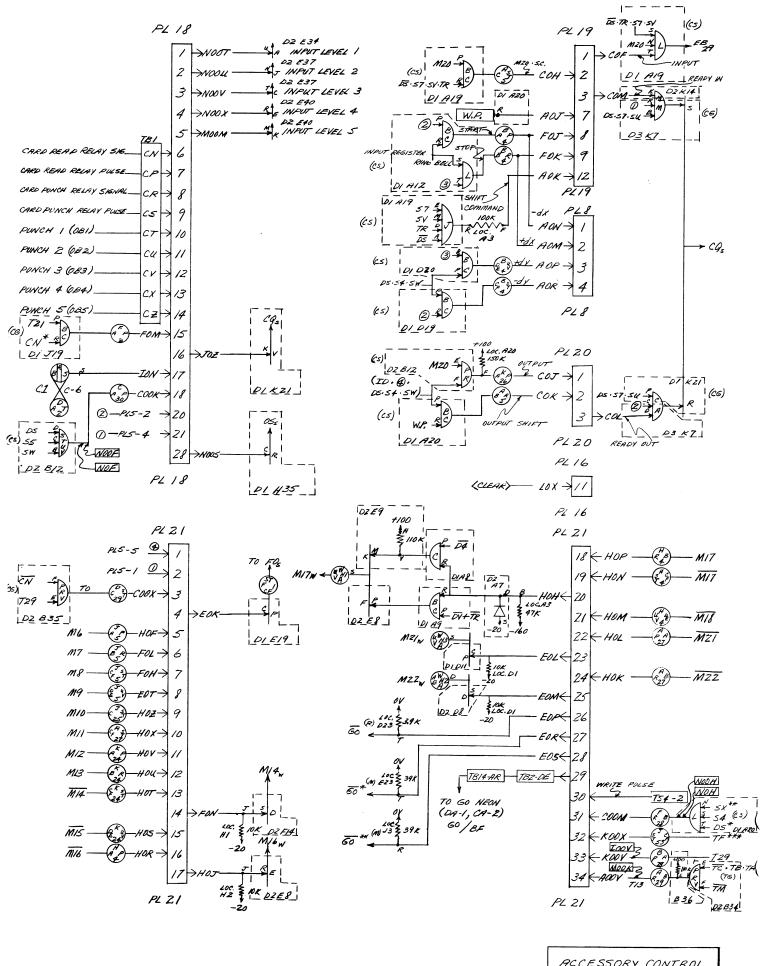

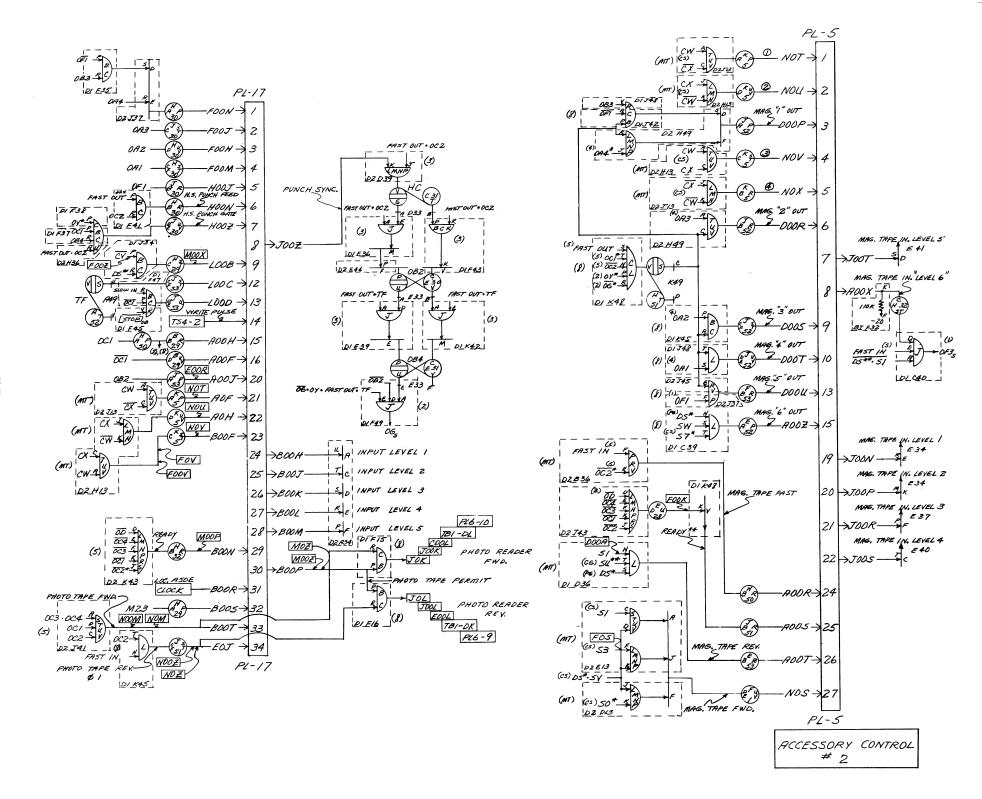

SECTION F: THE INPUT-OUTPUT SYSTEM

70

F-1

THE INPUT-OUTPUT SYSTEM - GENERAL

70

F-2

OC FLIP-FLOP CONTROL

F-3

71

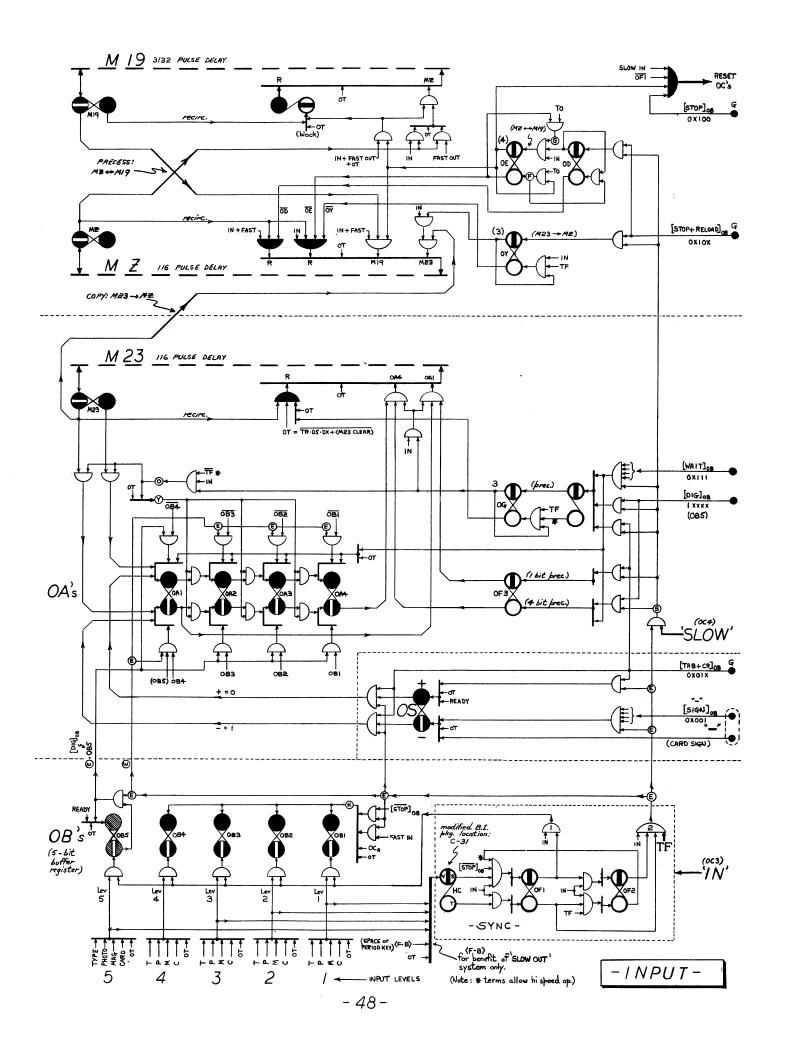

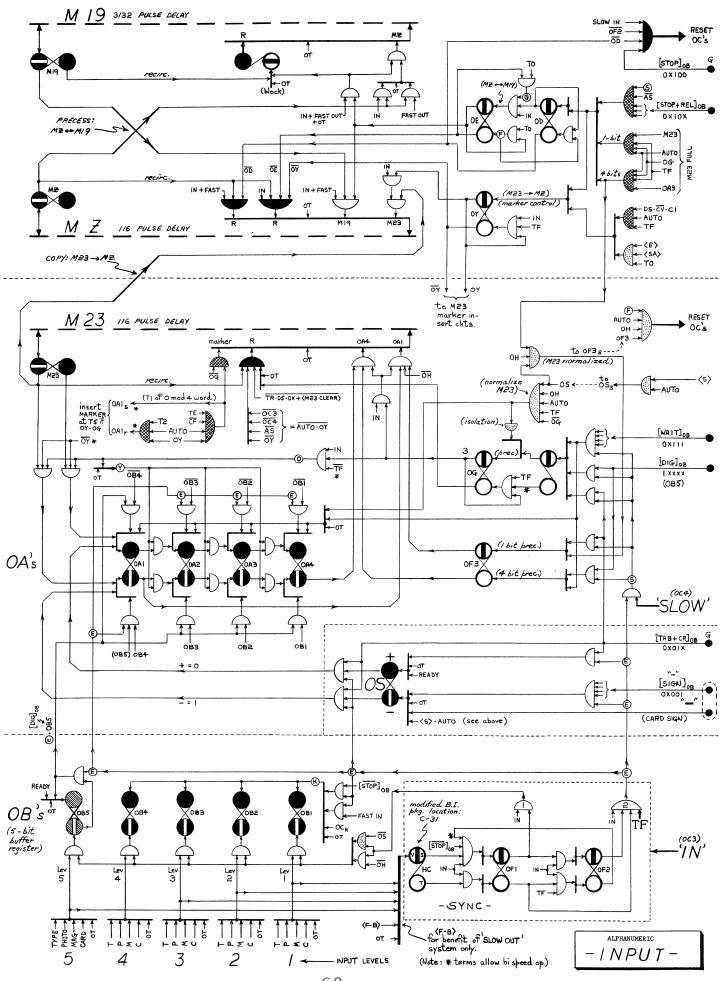

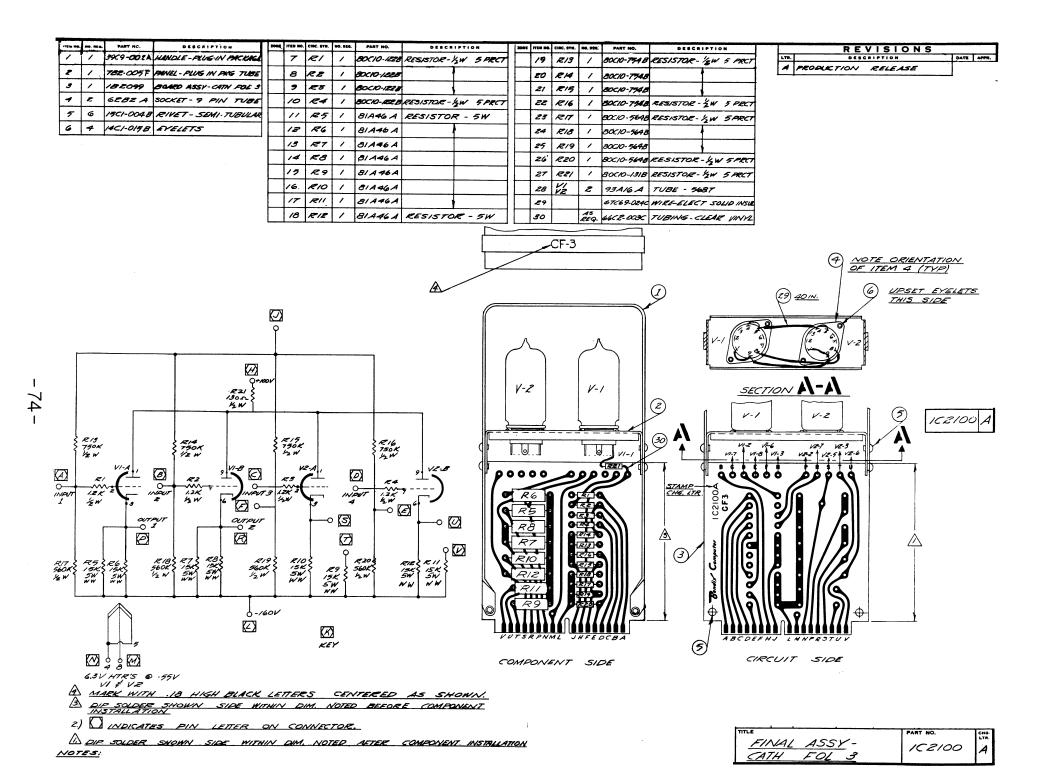

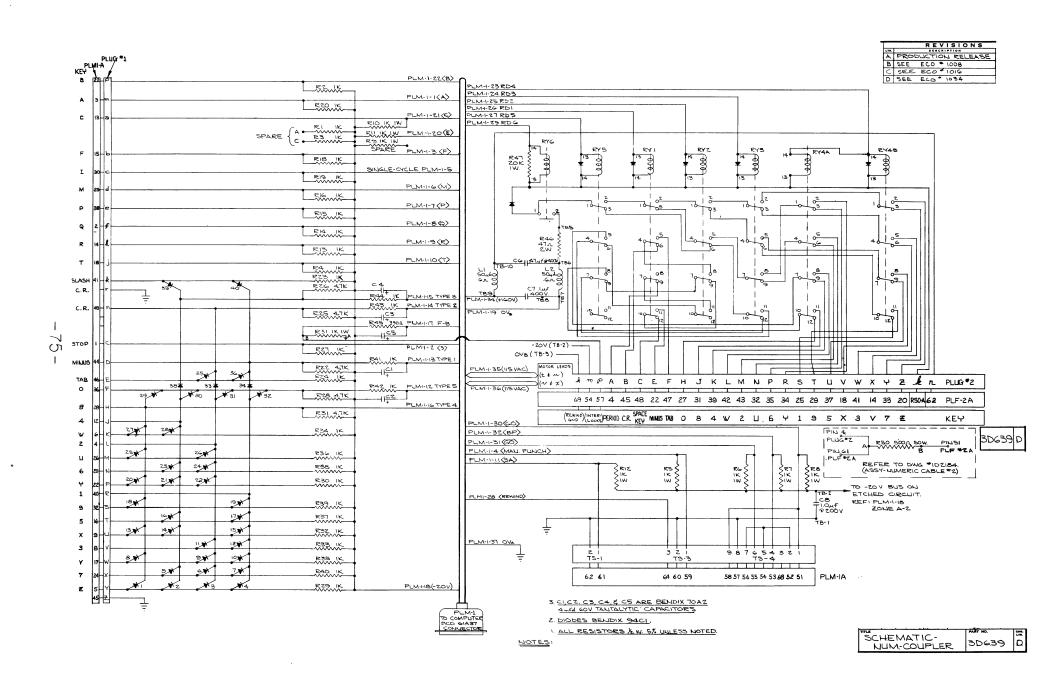

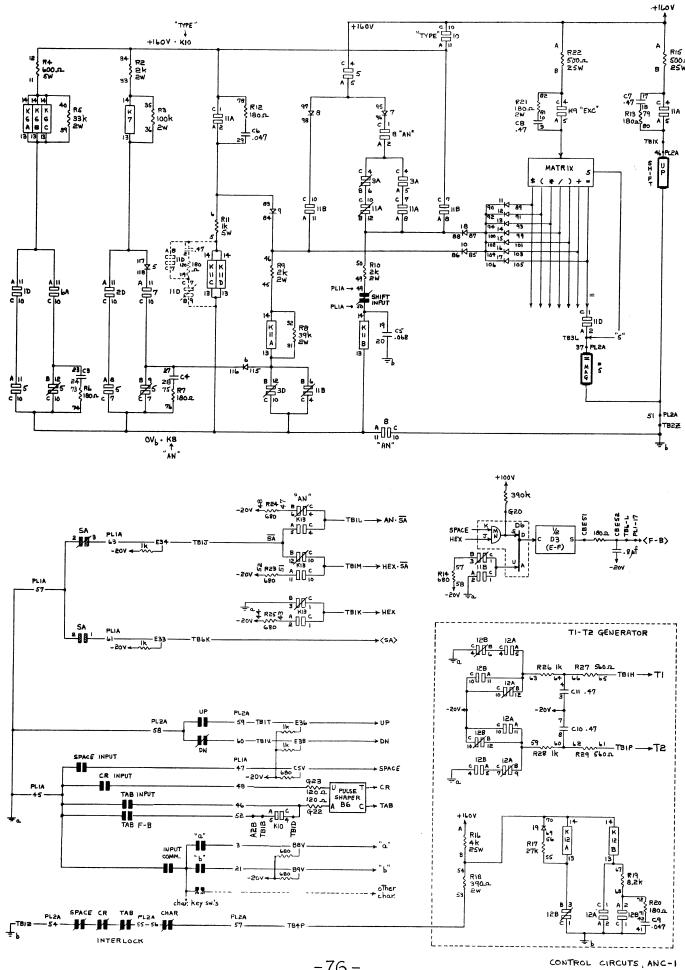

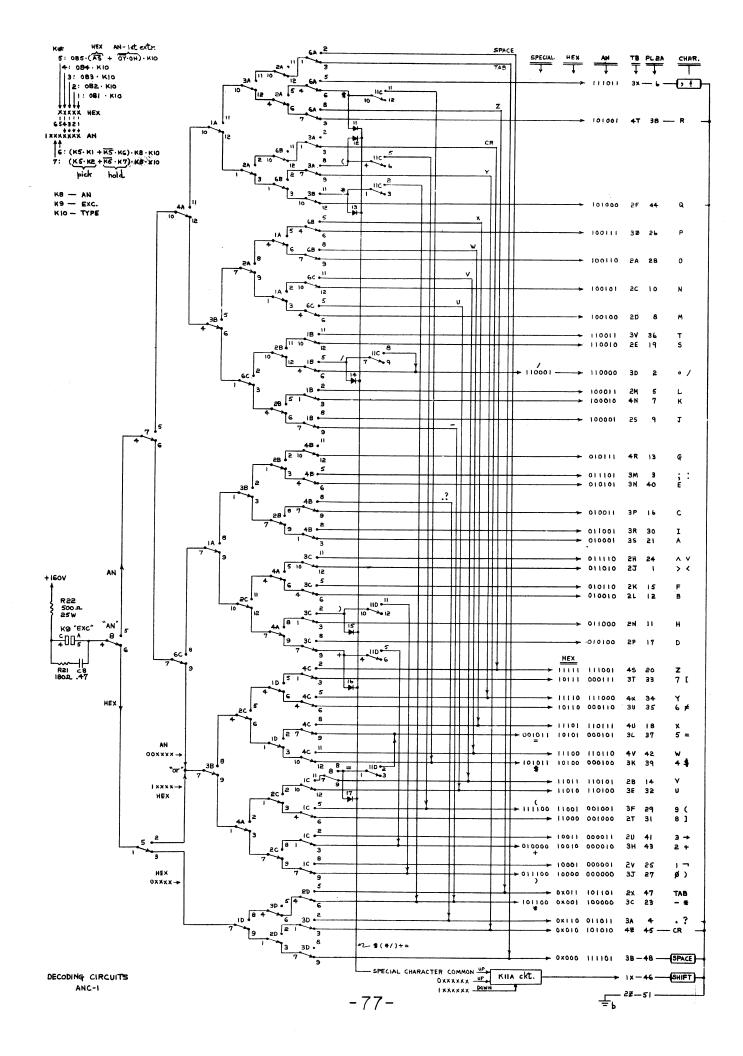

THE INPUT MEDIA

74

F-4

SLOW-IN LOGIC

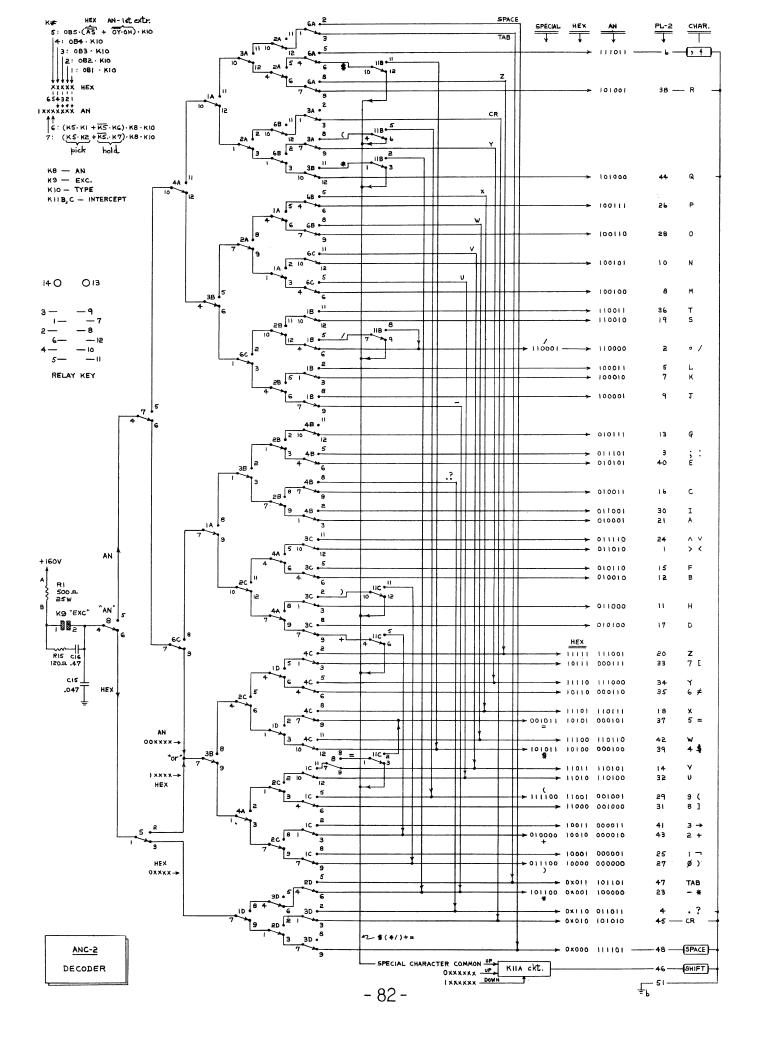

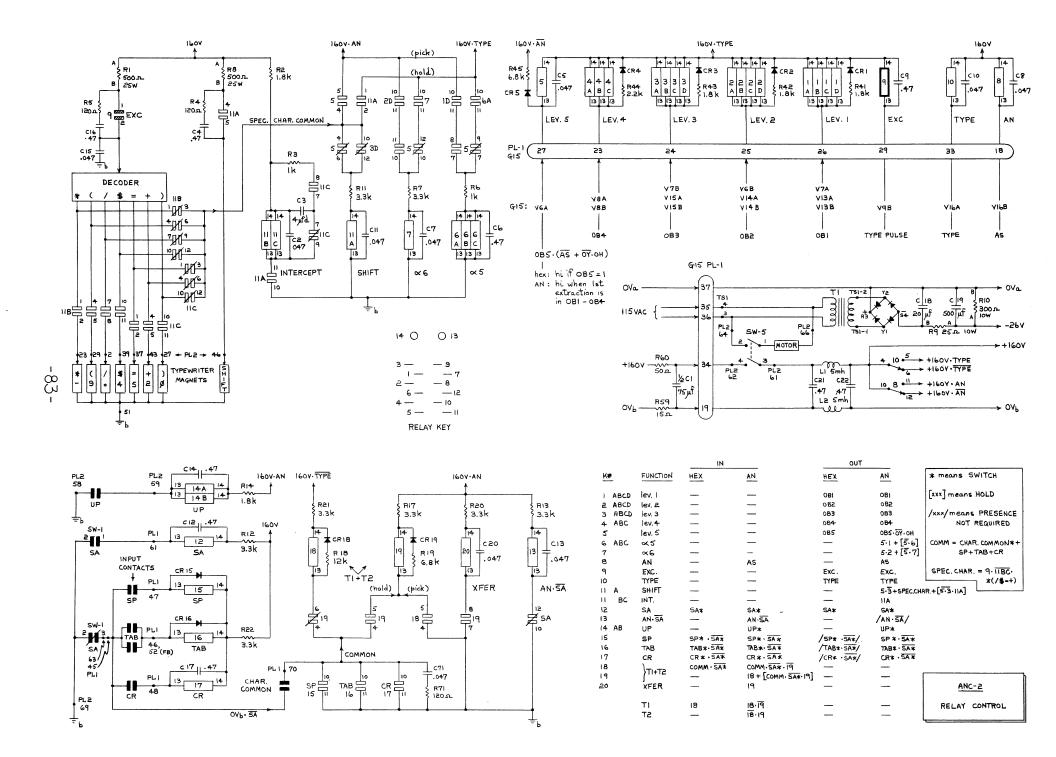

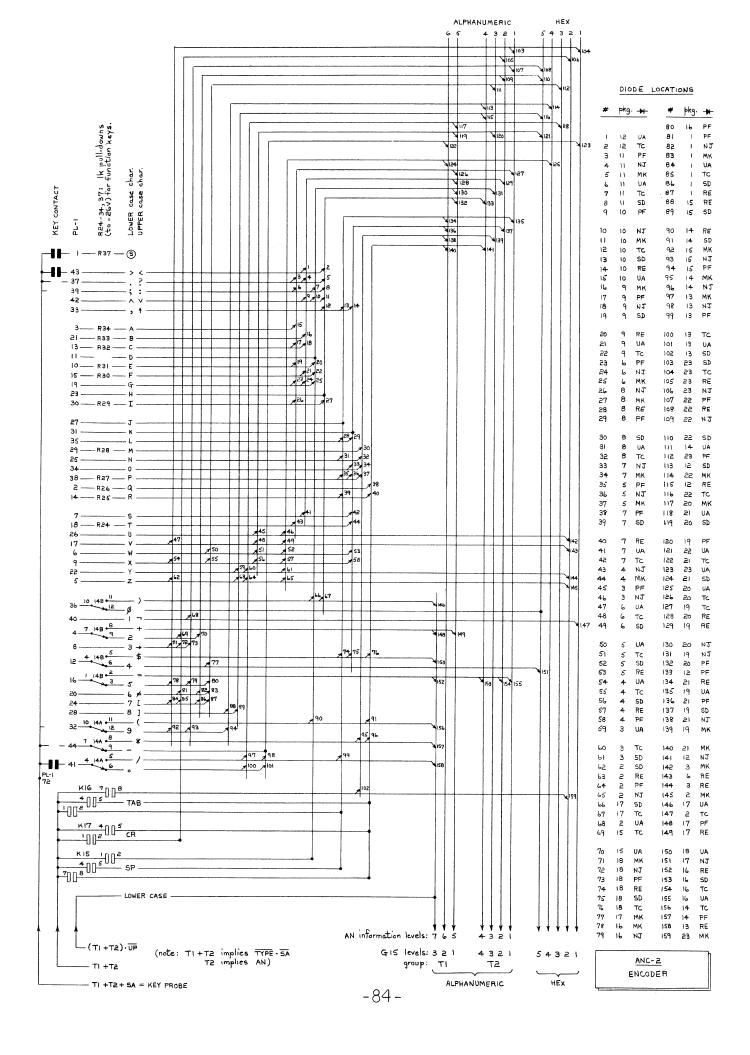

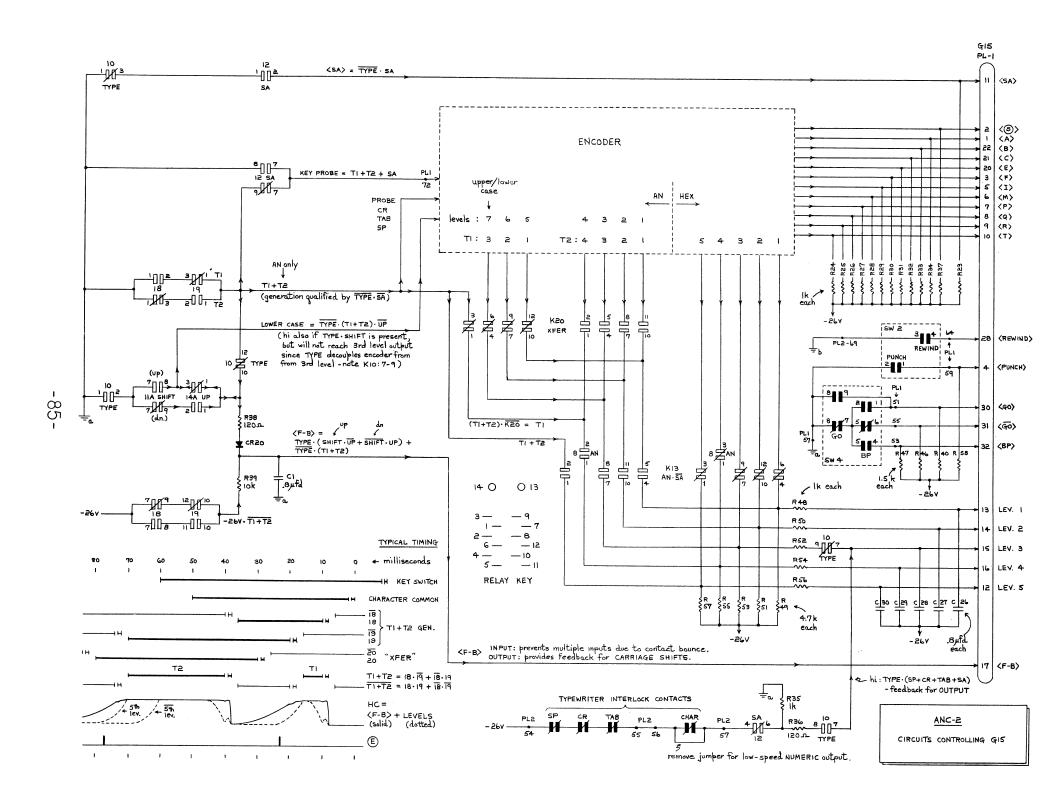

80

F-5

PHOTO-TAPE SEARCH (FAST-IN)

81

F-6

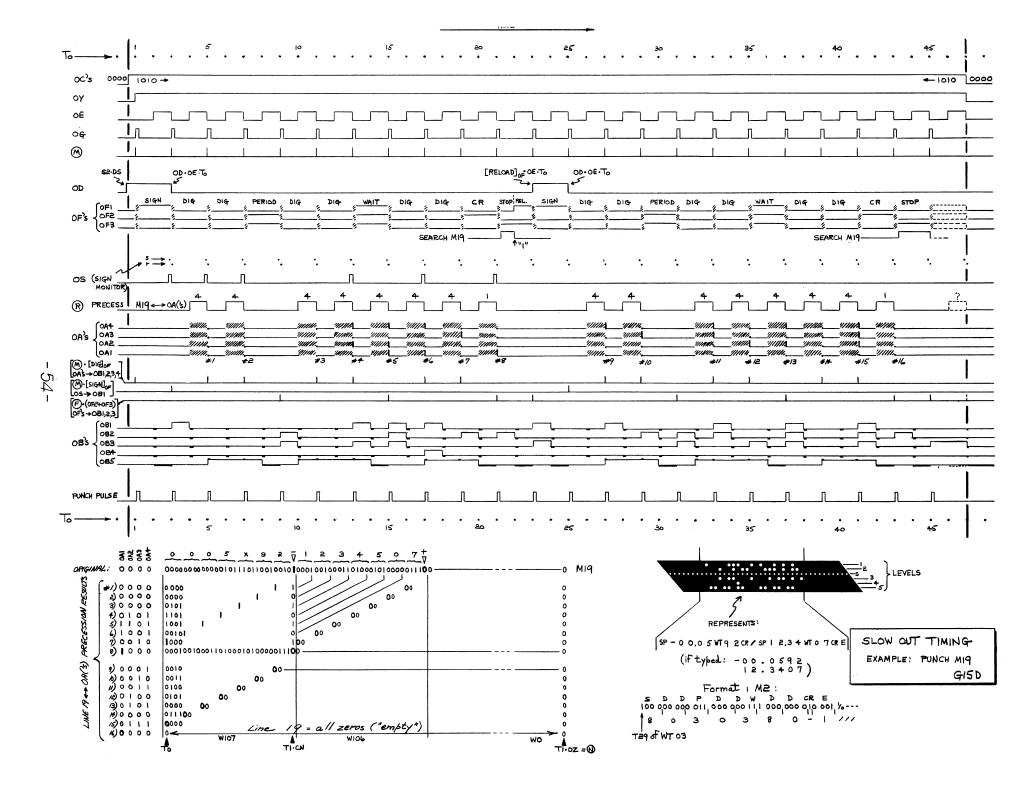

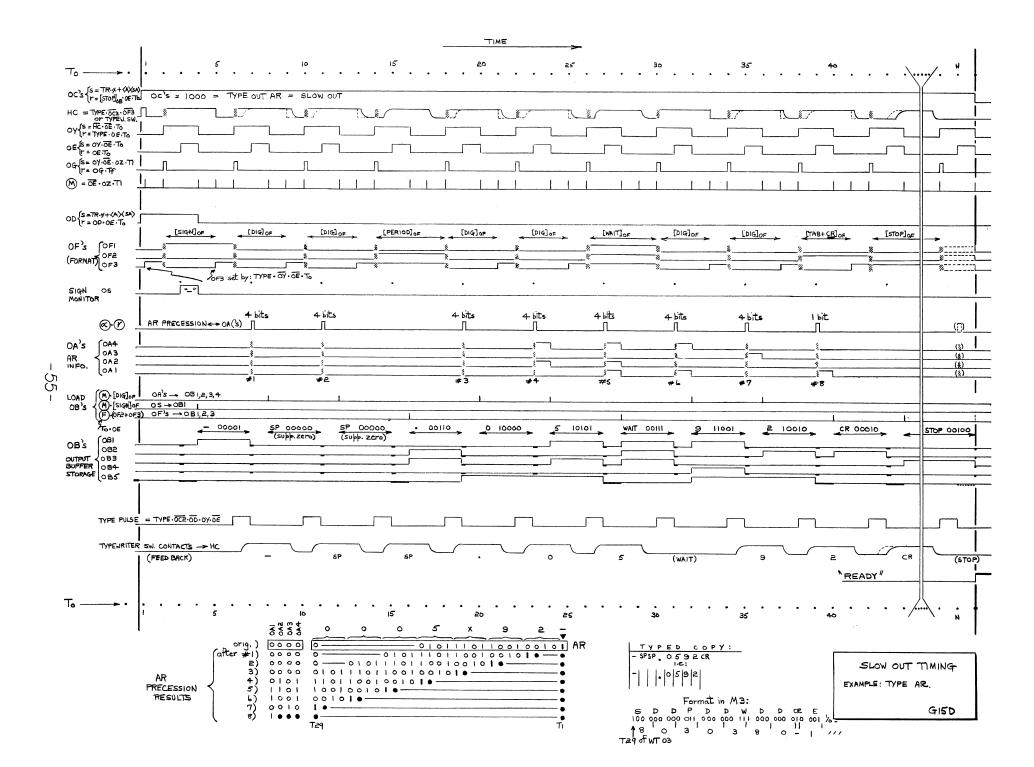

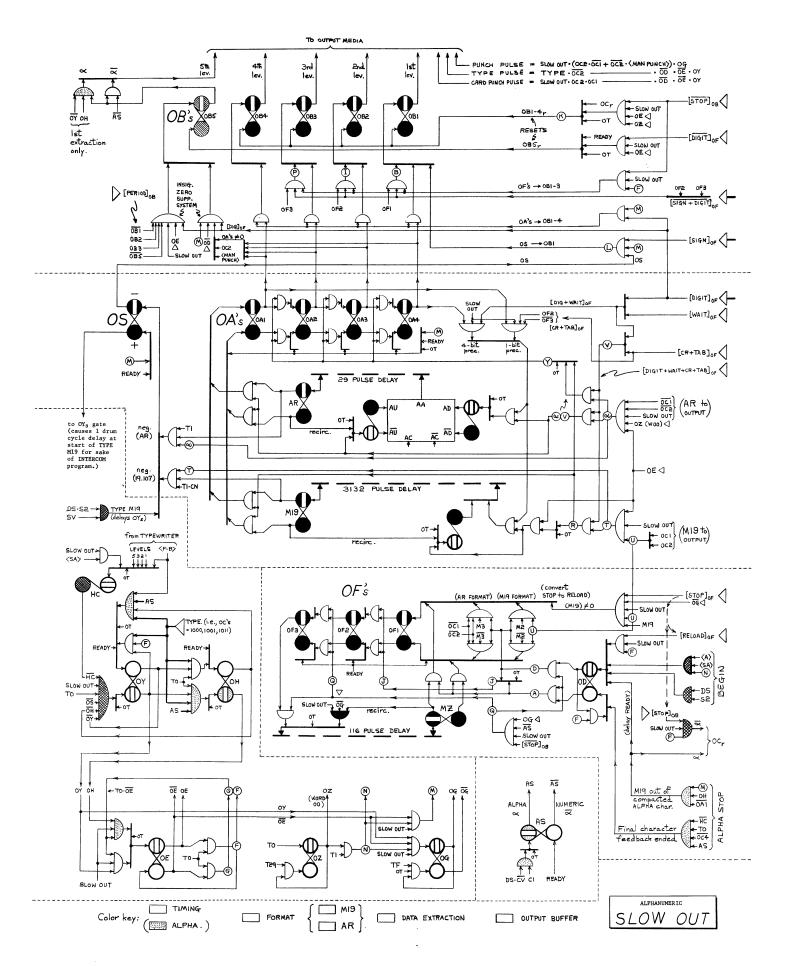

SLOW-OUT - GENERAL

F-7

81

THE SLOW OUTPUT MEDIA

83

F-8

SLOW-OUT LOGIC

88

F-9

FAST-OUT - GENERAL

88

F-10

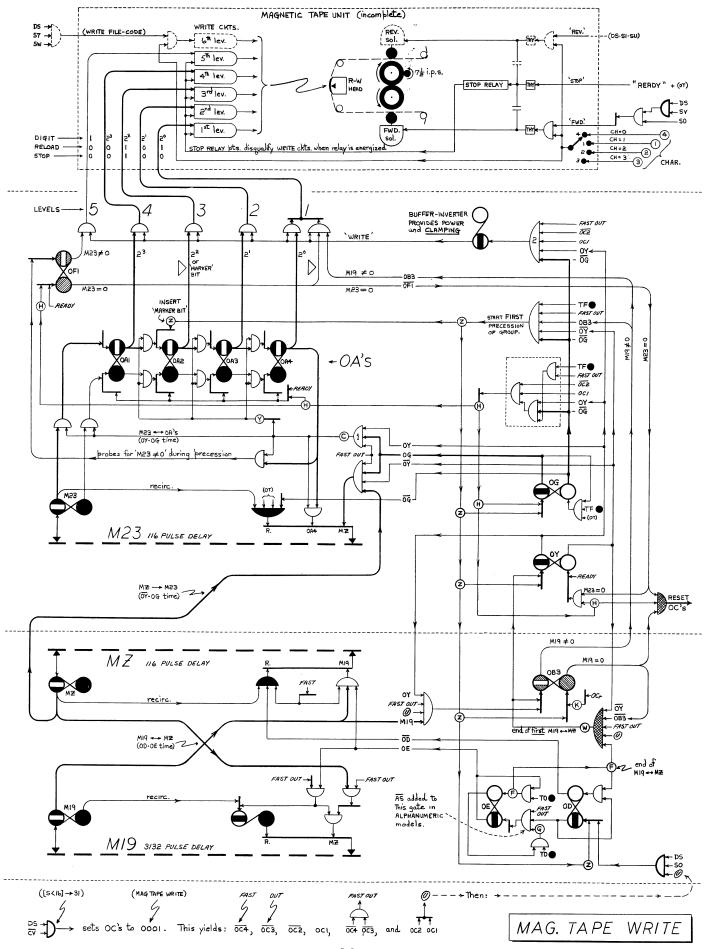

MAGNETIC TAPE WRITE (FAST-OUT)

90

F-11

MAGNETIC TAPE READ (SLOW-IN)

MULTIPLE MAGNETIC TAPE UNITS

91

F - 12

MAGNETIC TAPE

91

F-13

MAGNETIC TAPE WRITE FILE CODE

91

F-14

MAGNETIC TAPE SEARCH (FAST-IN)

92

F-15

TIME ALLOWANCES - MAG. TAPE

92

FAST PUNCH OPERATIONS (FAST-OUT)

F-16

92

F-17

"SET READY" COMMAND (00 \rightarrow 31)

```

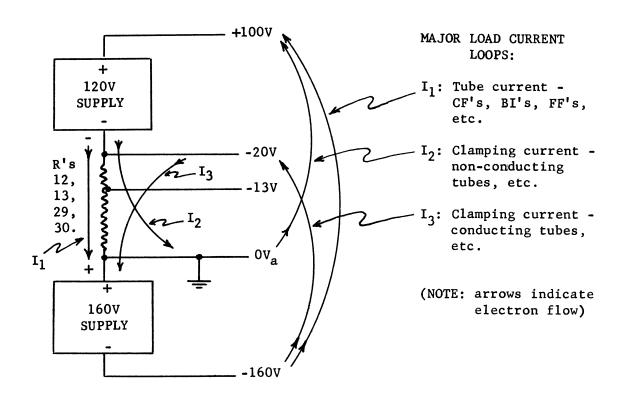

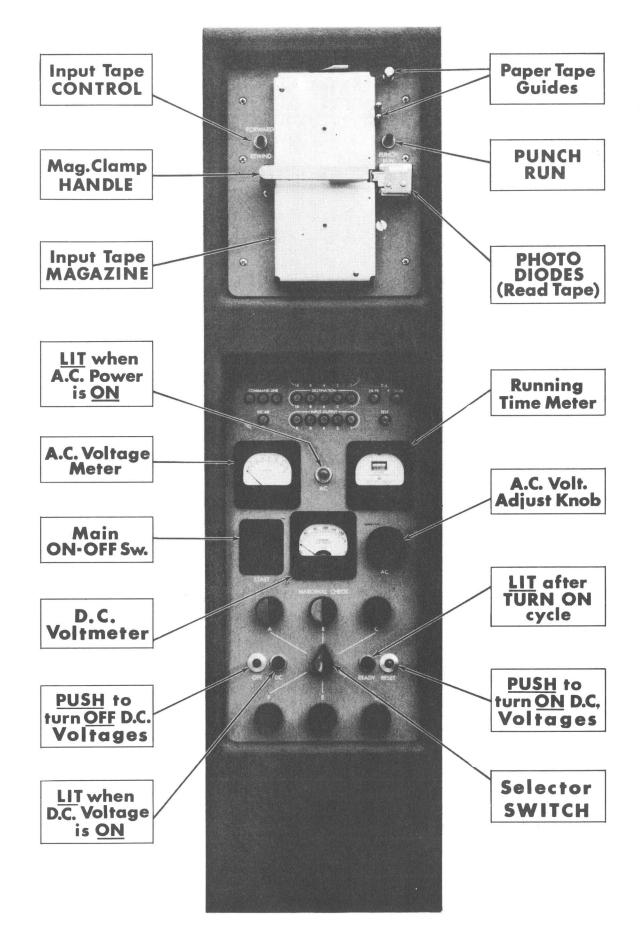

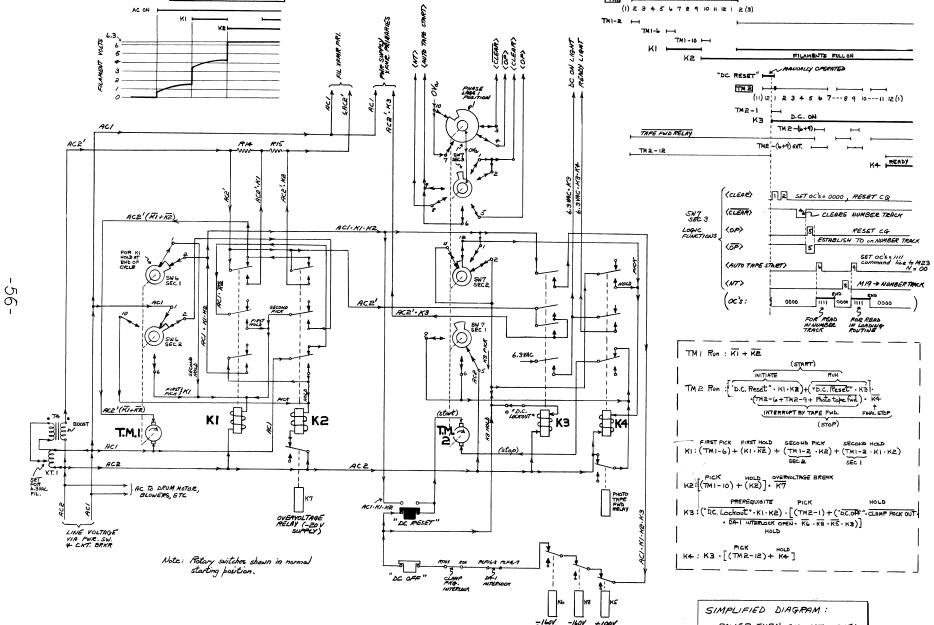

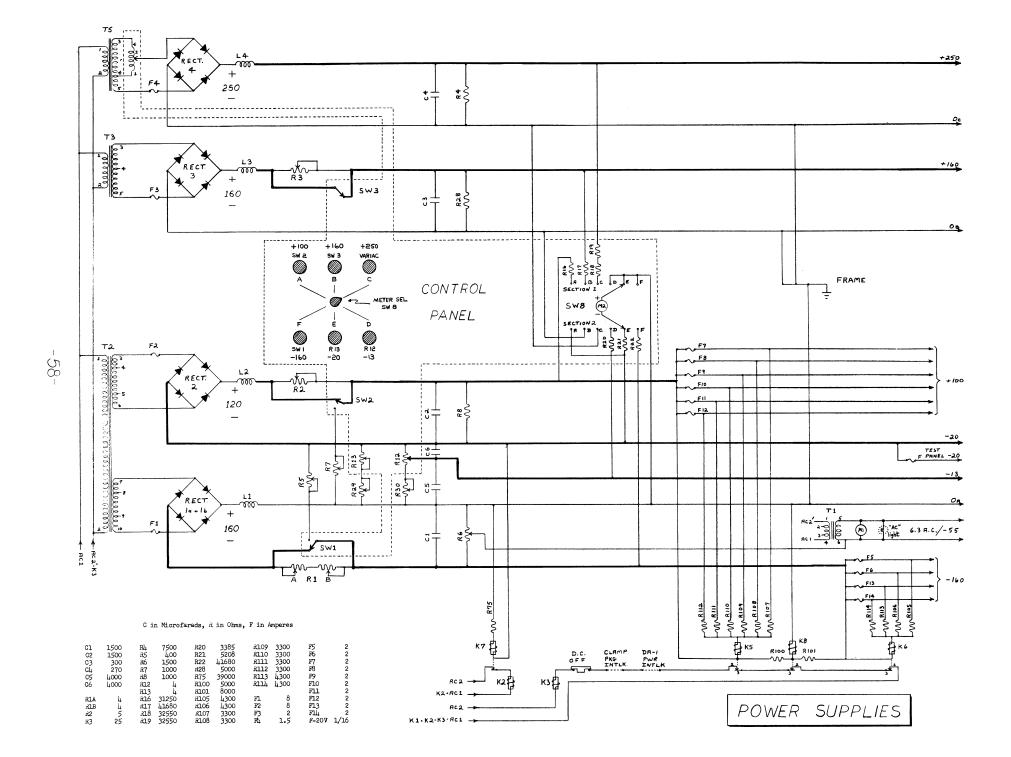

| 93             | G                 | SECTION G: | POWER SUPPLIES                      | AND | TURN-ON | CYCLE |

|----------------|-------------------|------------|-------------------------------------|-----|---------|-------|

| 94<br>96<br>97 | G-1<br>G-2<br>G-3 |            | PPLIES<br>-ON CYCLE<br>NCE SWITCHES |     |         |       |

# SECTION A

# FUNDAMENTAL CIRCUITS

This section is devoted to the fundamental circuits which constitute the "building blocks" of which the G-15D is composed. It is suggested that the reader thoroughly digest this section prior to proceeding further, for in the sections to follow an understanding of these circuits is taken for granted.

# "OR" GATES

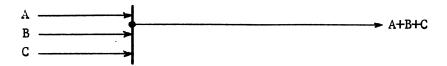

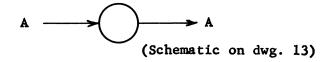

A-la An OR gate is a device for the purpose of yielding a high output signal if any of its input terms are high. Symbolically an OR gate is represented as shown:

schematically:

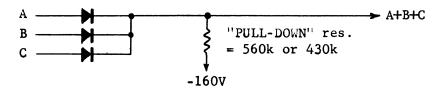

A-1b Considering the connection of the diodes, the input terms are isolated from one another by diode back resistance. The common connection of the diodes will yield an output which, for all practical purposes, is short-circuited to the input term having the highest potential. Assuming the inputs are (individually) either at -20V or 0V, the output should be at the highest input potential. That is, if one or more input terms reach 0V the output will reach 0V; if none are above -20V, the output will be at -20V. The loading resistance to -160V is known as the PULL-DOWN resistor; its function is to "pull" the output potential "down", while the input terms pull it up.

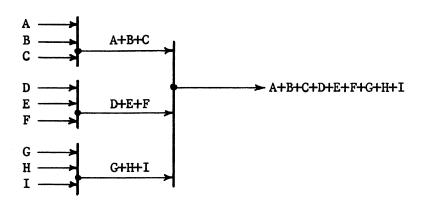

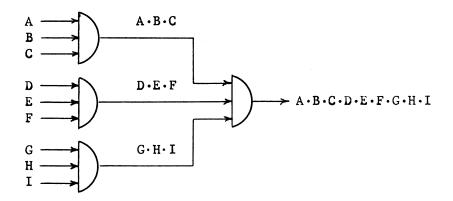

A-1c Should only one input term be high (OV), its diode must handle all of the current required to drop 160V across the PULL-DOWN resistor. The other diodes will be "biased off"; however, a certain amount of reverse current will exist in the "biased off" diodes. This will be a function of the reverse voltage applied (-20V) and the back resistance of each diode. As the number of terms entering an OR gate is increased, the back current loading problem increases. For this reason a limit is placed on how many terms can feed one OR gate. If more than the allowable limit is to be exceeded, a series of OR gates may be employed to relieve the problem. For example, if nine terms are to feed an OR gate, the following arrangement can be used:

A-1d Logically, the function is identical to that of a single nineterm OR gate. Although the total forward resistance may be increased by a trivial amount, the back resistance loading problem is substantially reduced. Drawing #3D293 illustrates the distribution of diodes comprising the "EB", which is a multi-term OR gate.

A-le Dynamic properties: If an OR gate is fed by a square-wave, and the output is loaded by distributed capacitance to ground, the output signal will rise (from -20V to OV) quite rapidly since the capacitance will discharge through the forward resistance of the active diode; however, when the output signal drops, the capacitance must charge through the PULL-DOWN resistor, which has a relatively high value. Hence, the decay time of the TRAILING EDGE of an OR gate's output signal is liable to be SLOW.

A-1f Cathode-follower OR gates: Cathode-followers may be used in the construction of an OR gate as follows:

This circuit is advantageous in that (1) loading of the inputs is light, (2) inputs are isolated from the output, and (3) the circuit supplies a power boost to the output term. Only a few such gates exist in the G-15D. One such circuit may be seen on Drawing #3D293 - see "EB". (Cathodefollower OR gates are sometimes referred to as "FAST 'OR' GATES" since they do not suffer from the phenomenon described in section A-le.)

# "AND" GATES

A-2a An AND gate is a logical circuit for the purpose of yielding a high output only if all of its input terms are high. Symbolically, an AND gate is illustrated as follows:

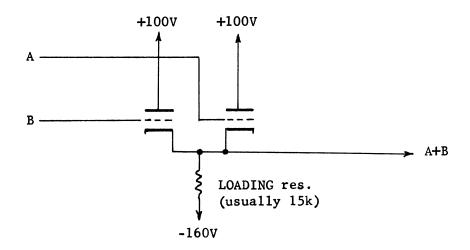

schematically:

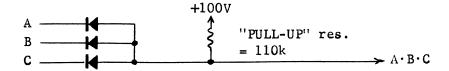

A-2b The output is virtually short-circuited to the lowest input term. Therefore, only if <u>all</u> inputs are high (OV) will the output be high. The loading resistor is known as the PULL-UP resistor; its function is to "pull" the output potential "up", while the input terms pull it down.

A-2c As in the case of an OR gate, the input terms are isolated from one another by diode back resistance; also, a single AND gate with an excessive number of input terms will yield a significant back resistance loading problem. Splitting multi-term AND gates as shown below will relieve the back resistance problem (similar to the OR gate case) without altering the logic of the circuit:

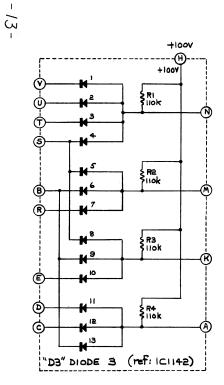

A-2d Dynamic properties: If an AND gate is fed by a square-wave, and the output is loaded by distributed capacitance to ground, the output will rise (from -20V to OV) by virtue of the capacitance discharging through the PULL-UP resistor; therefore, the rise time of the <u>LEADING EDGE</u> of an AND gate's output is liable to be <u>SLOW</u>. The trailing edge (decline from OV to -20V) will be rapid since the capacitance will charge through the forward resistance of the active diode. (In some cases, to reduce rise time, PULL-UP resistors have been shunted by "FREE RESISTORS", which are 110k and 150k resistors to +100V and are available in D1 and D2 packages.)

## AND GATES and OR GATES - COUPLING

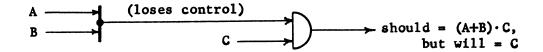

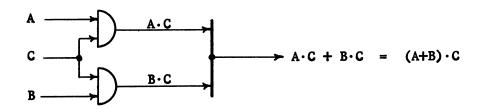

A-3a OR gates and AND gates may be connected to one another subject to the following major restriction: It is permissible for an AND gate to feed an OR gate directly; however, an OR gate may not feed an AND gate without an intervening stage of isolation. (A CATHODE-FOLLOWER or BUFFER-INVERTER can supply the necessary isolation.)

A-3b The reason for this restriction may be attributed to the fact that an OR gate (with or without PULL-DOWN resistor - ref. A-10a) is unable to carry enough current to drop 120V across the 110k PULL-UP resistor in the AND gate; consequently the OR gate cannot render the AND gate's output equal to -20V when the logic calls for such a case. Ohm's law will prove the point.

A-3c As an example, the circuit below should yield  $(A+B) \cdot C$ , but will actually yield C since the (A+B) combination cannot disqualify the AND gate.

a satisfactory alternative circuit is:

#### CATHODE-FOLLOWERS

A-4a A CATHODE-FOLLOWER is symbolically noted as follows:

A-4b Cathode Followers serve no purpose as far as logic is concerned. They handle certain technicalities in the electronics. The proposition of an OR gate feeding an AND gate (above) is one example. They are installed whenever necessary for purposes such as the following:

- 1) Isolation (hi Z in, lo Z out).

- 2) Power boost

- a) Resistive loads

- b) Reactive loads (i.e. preservation of wave shape when distributed capacitance loading is heavy).

- 3) Addition of constant voltage to input.

A-4c The CATHODE-FOLLOWER circuits available in the packages provide loading flexibility in some cases. These cases provide optional amounts of cathode loading resistance within the CATHODE-FOLLOWER package itself, allowing a variety of loads. The grid circuits also provide a degree of flexibility in some cases.

Note that the grid return resistances in the packages involve voltage dividers. The reason for this is to render the grid potential -92V (instead of -160V), in the event of removal of the package supplying the input signal. This will prevent the cathode from approaching -160V which could result in (1) exceeding the filament-to-cathode voltage rating of the tube (filaments are returned to -55VDC), and (2) applying excessive inverse voltage to diodes controlled by the cathode-follower.

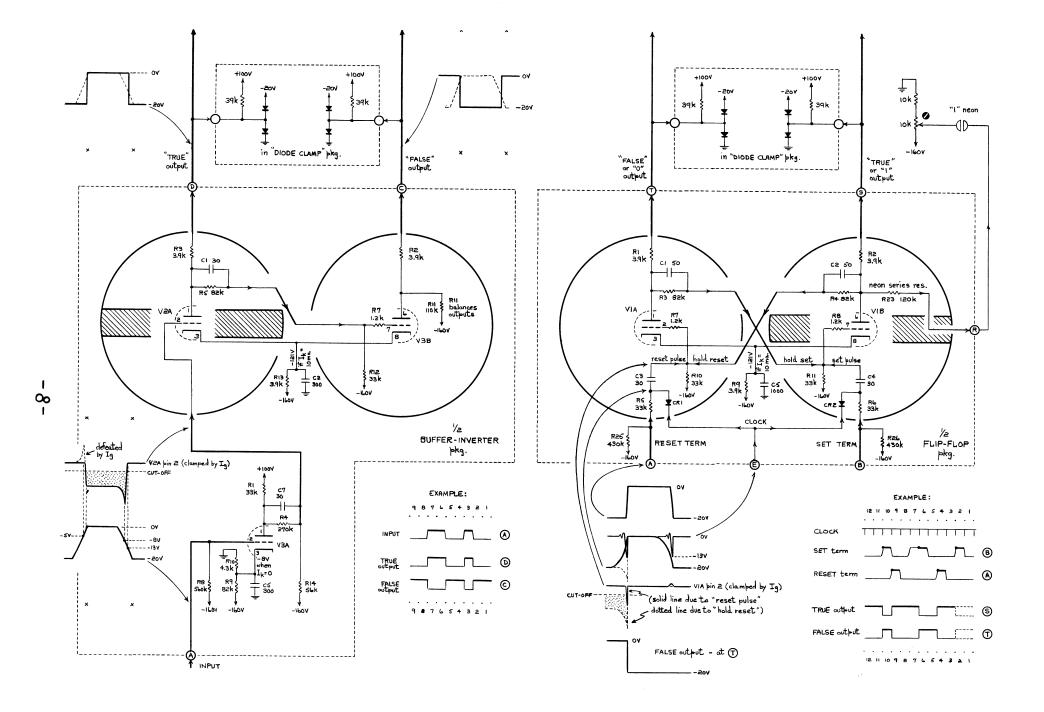

#### **BUFFER-INVERTER**

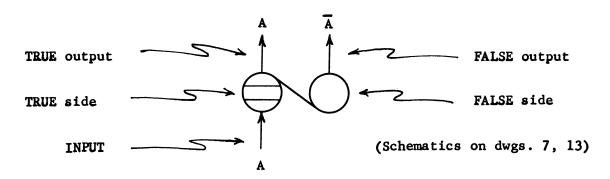

A-5a A BUFFER-INVERTER is symbolically noted as follows:

A-5b A BUFFER-INVERTER is a follower. Its true output "A" follows the input "A". The false output " $\overline{A}$ " is the exact opposite of "A" (i.e. " $\overline{A}$ " is "A" inverted, hence the term "inverter").

A-5c The outputs are clamped at -20V or OV and are capable of feeding several loads. Furthermore, loading of the outputs does not affect the input (hence the term "buffer").

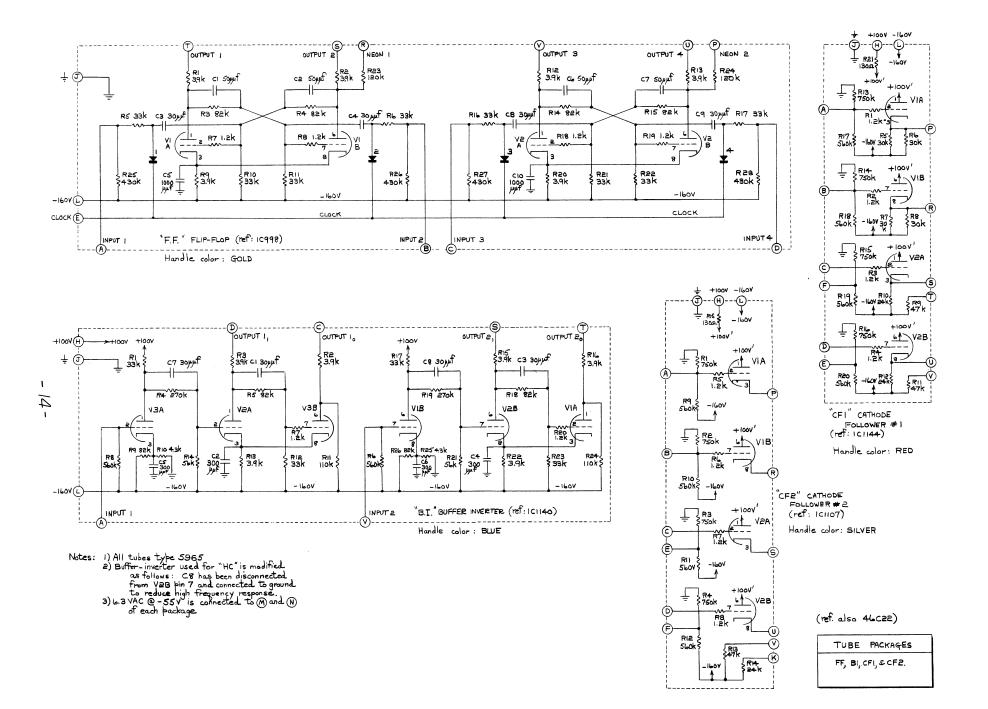

A-5d Refer to Drawing 7 (left), BUFFER-INVERTER schematic: The first inverter (V3A) receives the input signal "A" at pin 2. This signal should be at OV, -2OV, or in transition - subject to integration. The plate output should yield a potential at the grid of the next inverter (V2A) such that it will either be cut off or fully conducting. C5 and C7 both contribute to high frequency peaking to compensate for possible integration suffered by the incoming signal (V3A, pin 2) due to distributed capacitance. This peaking results in rapid transit time in the output current of V2A (and V3B), effectively "cleaning up" the leading and trailing edges of the incoming signal, hence synthesizing its ideal shape.

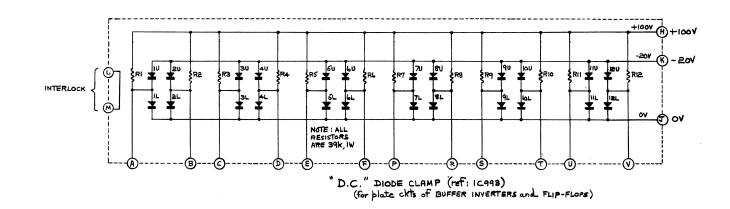

A,5e The V2A and V3B plate circuits are completed by components located in DIODE CLAMP package. A schematic of such a package is shown on

Drawing 12. This packaging system keeps the diodes physically separated from the heat-producing components in the BUFFER-INVERTER package.

A-5f When V2A conducts, its plate will be low consequently cutting off V3B; conversely, if V2A is cut off, its plate will be high causing V3B to conduct. Output pin D will yield the TRUE output "A" - pin C the FALSE output "A". Normally either V2A or V3B (but not both) will conduct providing a potential of approximately -121V to their common cathode connection; C2 holds this potential during transitions.

A-5g The DIODE CLAMP circuit terminating the W2A and V3B plate circuits assure that output pins D and C will be clamped either at -20V or OV. Loading of the outputs should only serve to add to or subtract from the clamping current. Overloading of these outputs can prevent clamping current, resulting in instability. Low emission triodes can also result in inadequate current for loading and/or clamping.

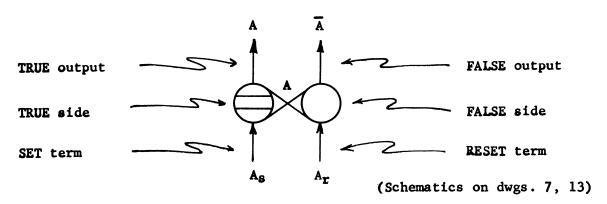

#### FLIP-FLOP

A-6a A FLIP-FLOP is symbolically noted as follows:

A-6b A FLIP-FLOP is an ELECTRONIC SWITCH consisting of two D.C. inverters and a trigger circuit. It has two stable states known as SET and RESET. SET is the state in which the TRUE OUTPUT (striped side of symbol) is high (OV) while the FALSE OUTPUT is low (-20V). RESET is the state in which the FALSE OUTPUT is high (OV) and the TRUE OUTPUT is low (-20V). The SET STATE results from the application of a SET TERM, while the RESET STATE results from the application of a RESET TERM. The FLIP-FLOP once rendered in one of its two stable states (SET or RESET) will remain in that state until caused to change by an input term calling for a change in state.

A-6c Drawing 7 (right) shows a schematic of a complete FLIP-FLOP circuit. It can be seen that, with the exception of the NEON SERIES RESISTOR, the two inverters are drawn as mirror-images of each other and that each one feeds the other.

- A-6d Normally, one tube will be conducting, thereby holding the other cut off. If VIA is conducting, it will hold VIB cut off maintaining the SET state of the FLIP-FLOP. VIA, by conducting, will render the FALSE output (pin T) low (-20V), while VIB, by not conducting, will allow the TRUE OUT-PUT (pin S) to be high (OV). If the above state were reversed, the FLIP-FLOP would be in the RESET state.

- A-6e To bring about a change in state, the conducting tube will be driven into cut-off by a negative trigger signal. This will cause a rise in its plate voltage which will turn the non-conducting tube on; this, in turn, will hold the previously conducting tube cut off. This establishes the new stable state in which the FLIP-FLOP will remain until another trigger signal, applied to the opposite side, causes it to change.

- A-6f The trigger circuit consists of two identical gates: one for SET and the other for RESET. CLOCK is applied to both, CLOCK consisting of negative pulses of short duration (.3 .5 microseconds) appearing at 9.3 microsecond intervals. The CLOCK line is normally at OV, but reaches -13V during a CLOCK pulse. CLOCK is the synchronizing signal that causes the FLIP-FLOP to be SET or RESET depending upon logical presence or absence of the SET TERM or RESET TERM.

- A-6g Consider now the RESET circuit. If the RESET TERM is logically absent (at -20V), CLOCK is decoupled from C3 by virtue of the back resistance of CR1, which will be "baised off." In consequence no negative pip should be coupled through C3 to the grid of VIA. On the other hand, if the RESET TERM were to be logically present (at OV) at CLOCK pulse time, electrons would be transmitted through CR1's forward resistance into the bottom plate of C3 and to R5, which acts as a load resistance. Discharge of electrons from the top plate of C3 causes a negative-going "reset pulse" at the grid of VIA; this will cut VIA off.

- A-6h Regenerative action takes over as VlA's current drops: VlA's plate voltage rises, turning on VlB. VlB's plate voltage drops, cutting off VlA, which is the triode which the "reset pulse" was cutting off in the first place. Cl and C2 accelerate the transition. The FLIP-FLOP will remain in this new state until VlB is cut off by a "set pulse."

- A-6i Whenever a FLIP-FLOP experiences a change in state, the charges on C1, C2, C3, and C4 will change. Until these charges are almost stabilized, the FLIP-FLOP will not be receptive to further trigger pulses were they to occur in rapid succession. Ample time is available for this stabilization since CLOCK pulses, available for trigger, occur at 9.3 microsecond intervals (i.e. rep. rate = 108 kc.)

- A-6j Drawing 7 indicates by waveform that when a CLOCK pulse is concurrent with the leading edge of the RESET TERM, the diode (CR1) will remain "baised-off." Even if the RESET TERM has a steep leading edge this will hold true. The potential at the top of the diode is the controlling potential. This potential will not rise instantly when a square-wave RESET TERM appears since C3 requires time to charge, with R5 (33k) limiting charge current. R5 and C3 then, constitute an integrating circuit in which high frequency components are dropped across R5. Hence, when CLOCK and the leading

edge of a RESET TERM are concurrent, CRl will remain "baised-off" during the first CLOCK pulse and the "reset pulse" will not appear until the next CLOCK pulse.

A-6k Should the trailing edge of a RESET TERM and CLOCK be concurrent the same reasoning holds true. As the RESET TERM drops. C3 will maintain a qualifying potential at the top of CRl sufficiently long to permit CLOCK to be transmitted through the diode.

A-61 The RESET TERM itself does not appear to any significant extent at the grid of VIA. The high frequency components of the RESET TERM signal are dropped across R5, while the low frequency components are dropped across C3. If VIA and VIB were removed from the circuit and CLOCK were to be decoupled, the RESET TERM would appear at VIA-pin 2 as a small positive-going signal at leading-edge time and a small negative-going signal at trailing edge time. Neither of these are of any consequence unless marginal conditions exist in the circuit when operating with a weak tube. In such cases, the only malfunction would be a function of the leading-edge of a RESET TERM applied the FLIP-FLOP when it is already in the RESET state. The positive-going signal remnant at VIA-pin 2 could cause VIA to conduct; this could result in SET-TING the FLIP-FLOP. This would only occur when VIB is weak and is unable to hold VIA cut off with an adequate safety margin.

A-6m Obviously the analysis of the RESET circuit applies also to the SET circuit since they are identical.

A-6n The example in the lower right section of Drawing 7 indicates FLIP-FLOP reaction to SET and RESET terms.

A-60 FLIP-FLOP SUMMARY: A FLIP-FLOP is an electronic switch which may be SET or RESET by means of CLOCK, which can be gated by the SET or RESET TERMS. Transition can take place only at CLOCK time. If a CLOCK pulse occurs at the instant a SET or RESET TERM begins to rise, it will be the following CLOCK pulse that causes transition. Also, a CLOCK pulse coincident with the beginning of the decline of a SET or RESET TERM will still consider that term high. If the SET TERM occurs during one pulse period, the TRUE OUTPUT of the FLIP-FLOP will not be high until the next pulse period. Similarly, if the RESET TERM occurs during one pulse period the FALSE OUTPUT of the FLIP-FLOP will not be high until the next pulse period.

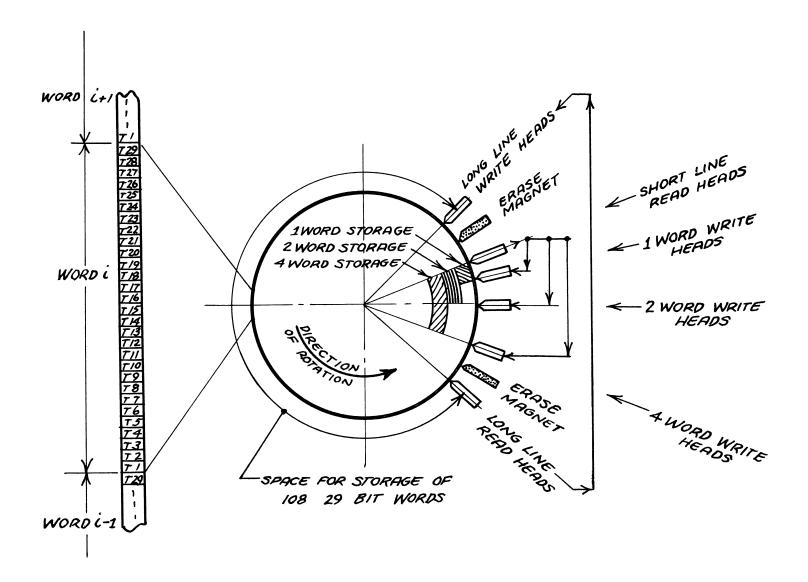

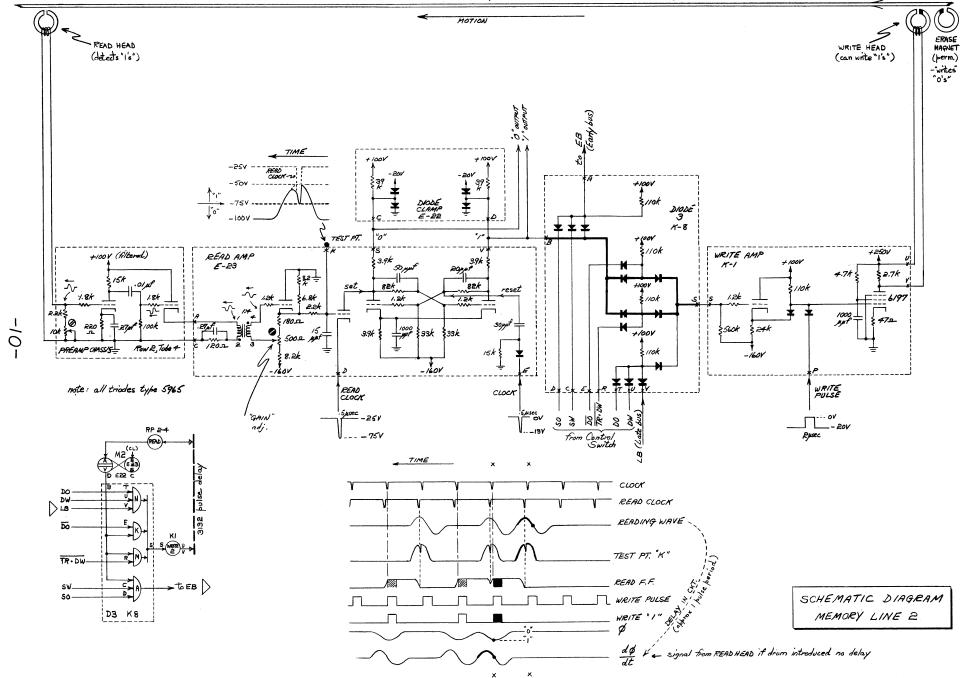

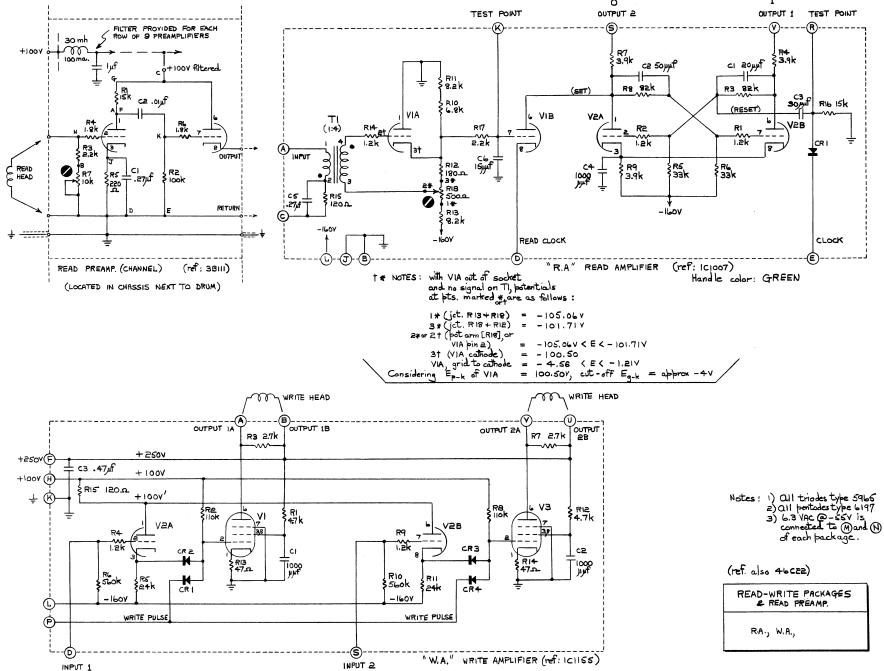

## MEMORY LINES (Ref. Drawing 9)

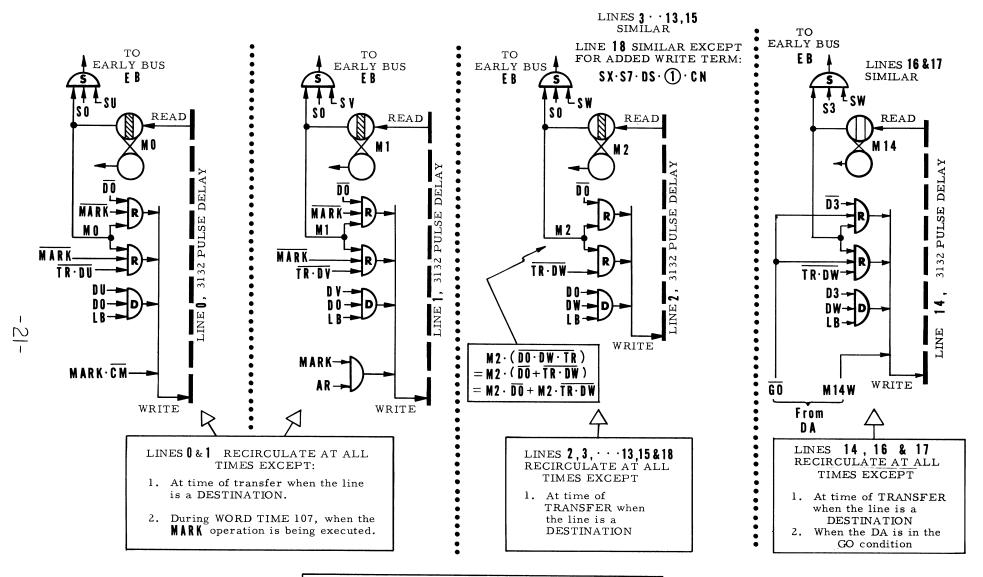

A-7a The recirculating memory line is the storage device used in the G-15D memory. It consists essentially of a writing station, a time delay, a reading station, and a means of regeneration of information (subject to external control).

A-7b Normal operation of a memory line is recirculation (i.e., information, once written in the line, will remain in the line unchanged and be revealed at the reading station periodically.) Drawing 9 is the schematic of Memory Line #2 which will be used as an example. The line is shown symbolically in the lower left-hand corner in the form it would be found on the "D-SIZED PRINTS."

- A-7c The object of this discussion is to trace the writing of one bit of information through a recirculation cycle.

- A-7d To begin, to write a ONE, a 2 microsecond WRITE PULSE is coupled to the writing pentode's control grid. This will cause flux in the write head (upper right) and will consequently influence the magnetic drum surface passing under its gap at the time. This magnetic surface approaching the write head is erased by a permanent magnet mounted on the drum shroud. The erasure represents ZERO; writing a ONE on the erased surface causes a distortion of the regular flux pattern of the surface. (Writing a ZERO involves no writing at all, hence no flux distortion.)

- A-7e The recorded element is carried by the drum surface past a reading head after a delay determined by the peripheral speed of the drum and the spacing between the writing and reading heads. When the flux irregularity (resulting from writing the ONE) passes under the gap of the reading head, the reading head flux, normally constant, reverses and then returns to normal. This flux change induces an EMF resembling a sine wave in the reading head coil.

- A-7f One end of the read head coil is grounded such that the floating end yields a sine wave, the trailing peak of which is positive. Resistance loading of the coil is accomplished in the PREAMPLIFIER CHASSIS and may be varied from 2.2k to 12.2k by a screwdriver adjustment. This is adjusted to minimize ring effect and to shunt the signal to obtain a normal level (500 mv. approx.). This is a factory adjustment and should not require attention unless the associated head is replaced.

- A-7g At this point, the signal requires amplification, a matter which is accomplished in a convential plate-loaded, RC-coupled amplifier employing low loading resistance for good high frequency response. The output is cathode-follower driven out of the PREAMPLIFIER CHASSIS into a READ AMPLIFIER package where monitoring of the signal takes place.

- A-7h The first step in the READ AMPLIFIER is to amplify, rectify, then amplify the incoming sine wave to produce a half sine wave of sizable swing for each detected ONE.

- A-7i The first operation in amplification is to terminate the cathode follower with a step up (1:4) transformer. (The .27 mfd and 120 ohm combination in the primary circuit is to prevent peak clipping without introducing degeneration and can be considered a biasing requirement.)

- A-7j The secondary of the step-up transformer constitutes the input to a "bootstrap" amplifier, which in this case is an over-biased cathode-loaded amplifier. The purpose of the amplifier is to amplify the positive portion of the input wave, without phase inversion. Response is controlled by returning the transformer secondary to a potentiometer in the cathode circuit. This adjustment controls: (1) the amount of degeneration, hence gain, and (2) the static bias on the stage, hence sampling level. It is normally adjusted to yield signals reaching the -50v level at test point K. This potentiometer may occasionally require adjustment to compensate for changing parameters elsewhere in the read-write circuit.

- A-7k At this point, the half sine waves are probed by READ CLOCK which is applied to the cathode of a flip-flop trigger tube. In the event of coincidence between READ CLOCK and a ONE waveform, the trigger triode will conduct, setting the READING FLIP-FLOP to ONE. When the trigger triode conducts, grid current is inevitable; this is limited by a 2.2k grid resistor. The 15 mmf. grid-to-ground capacitance counteracts the degenerative effect on the positive going grid signal by the negative going cathode and plate signals. READ CLOCK is obliged to supply grid and plate current to all trigger tubes. This accounts for relatively high peak power requirements of the READ CLOCK pulse driver (Ref. B-3g). Since this grid current load will only present itself when a line yields a ONE, the total load will be a function of the memory contents.

- A-71 Approximately 8.3 microseconds after the ONE bit has been stored in the READING FLIP-FLOP, CLOCK unconditionally resets it to ZERO. The flip-flop's ONE output is coupled via gates in the DIODE 3 (D3) package to the WRITE AMP package if the line is recirculating. (Heavy lines in the DIODE 3 package show recirculation path.)

- A-7m The first item in the WRITE AMP is a cathode-follower which permits the output of the OR gate in the DIODE 3 package to feed the AND gate feeding a power pentode (Ref. A-3, A-4).

- A-7n For the last two microseconds prior to resetting the READING FLIP-FLOP to ZERO, the AND gate in the WRITE AMPLIFIER was qualified by WRITE PULSE. This causes the writing pentode to conduct for two microseconds through the write head, rewriting the original ONE. Had the read head "detected" a ZERO (absence of a ONE), no writing would have taken place, effectively recirculating the ZERO.

- A-70 Needless to say, prior to the leading edge of the WRITE PULSE, the ONE output of the READING FLIP-FLOP should have risen to OV. This allows 6.3 microseconds for rise time. (This 6.3 microsecond rise time requirement factor applies to most signals in the computer and accounts for many CATHODE-FOLLOWERS and resistance-loading of certain circuits such as AND gates. Decay time is equally important but usually not as critical as rise time.)

- A-7p It can be seen that the READING FLIP-FLOP activity depends upon CLOCK for reset and READ CLOCK for set. These pulses synchronize all memory lines with a standard timing reference. WRITE PULSE synchronizes the writing. These pulses are shown on the top of Drawing 6 in approximate terms; their formation is described in Sec. B-3.

- A-7q The spacing between read and write heads is governed by the capacity of the particular memory line. In the case of a long memory line, the delay in the line is such that from the time a ONE is written until the time it is rewritten, 3132 (i.e., 108 x 29) pulse periods will elapse. This allows 3132 different bits to be read and rewritten within a recirculation cycle.

- A-7r The short lines have shorter delays as follows: 116 pulse periods, 58 pulse periods, and 29 pulse periods. The spacing from read head to write head is known as the TANGENTIAL adjustment. It is made at the factory and should not require any further adjustment. As long as READ CLOCK probes

the reading wave at its peak (test pt. K), the adjustment is satisfactory. Misadjustment would be revealed in misphasing of these two signals. CUSTOMER ENGINEERING should be consulted for adjustment details. It is unwise to attempt head adjustment without being well informed as to procedure. Accidental damage to a track could require replacement of the drum.

- A-7s Another adjustment of the heads is RADIAL adjustment. This should render head (gap) to drum surface spacing equal to 1 mil. (for both read and write heads.) Proper spacing is essential for good resolution and signal-to-noise ratio. This too is a factory adjustment. Only in the case of subnormal reading waves (not attributable to failing electronic components) should RADIAL adjustment be considered. As in the case of TANGENTIAL adjustment, CUSTOMER ENGINEERING should be consulted.

- A-7t Noise mentioned above is insignificant compared to the amplitude of a legitimate ONE being read since it is normally well below the sampling level in the READING FLIP-FLOP trigger stage. The worst noise element will result from crosstalk (magnetic coupling) between the write and read heads of a line. This interference is at its worst in the short (29 bit) memory lines.

- A-7u Another factor which may cause deviation from optimal memory line functioning is the result of head misadjustment due to thermal effects. Therefore, if the drum is cold, a line may operate with reduced safety margins. Only a line already in need of maintenance would fail due to this effect. If any memory line adjustments are to be made, it should be done when the drum has reached its normal operating temperature.

### MEMORY LINES: READ-OUT, READ-IN FUNCTIONS

A-7v READ-OUT: When information is to be read out of a line, the READ FLIP-FLOP output is coupled to an external circuit by an AND gate qualified by the desired terms. In the case of MEMORY LINE 2 (Drawing 9, lower left), M2 reaches EB if qualifying terms SW and SO are both high. Read-out does not disturb the contents of the source line.

- A-7w READ-IN: When information is to be read into a line from an external source, two operations are necessary: (1) allow the new information to reach the writing circuit, and (2) simultaneously block the recirculation path of the old information.

- A-7x Item (1) is handled by qualifying an AND gate to which the new information is applied. In LINE 2 (Drawing 9) terms DO and DW permit LB to be written. Item (2) is handled by blocking the gates which allow the READ FLIP-FLOP output to reach the writing station. If LINE 2 is selected as destination, both  $\overline{DO}$  and  $\overline{TR} \cdot \overline{DW}$  will be low at the appropriate time.

- A-7y Some special purpose memory lines may deviate from this pattern and will be discussed later. Needless to say, all READ-IN READ-OUT activities are appropriately synchronized by control circuits.

#### THE MEMORY

A-8a The DRUM MEMORY is composed of many recirculating memory lines such as the one just described. These lines can differ from one another

### as follows:

- 1) Capacity

- 2) Writing control

- a) Recirculation gating

- b) Method of writing new information

#### A-8b The MEMORY consists of:

```

21 long lines - 3132 bits (108 words) - Lines 00-19, and CN 5 short lines - 116 bits ( 4 words) - Lines 20-23, and MZ 3 short lines - 58 bits ( 2 words) - ID, MQ, PN 2 short lines - 29 bits ( 1 word) - AR, CM

```

A-8c Three of the above are not directly available to the programmer since they are for the benefit of internal computer functions. These are CN, MZ and CM. In addition to the recirculating lines mentioned above there are three permanently recorded (non-recirculating) lines known as CLOCK TRACK SPARE CLOCK TRACK, and TIMING TRACK (TM). These are for timing purposes and are discussed in Sections B-3a and B-5a.

A-8d Physically, the short memory lines are sandwiched in between the read heads and erase magnet of the long lines as illustrated on Drawing 8.

A-8e Memory line specifications:

pulse period = 9.3 microseconds

packing density = 90 bits/inch

read-record mode - RETURN TO ZERO

maximum access time = 28.5 milliseconds

## PHYSICAL LOCATION OF LOGICAL CIRCUITS

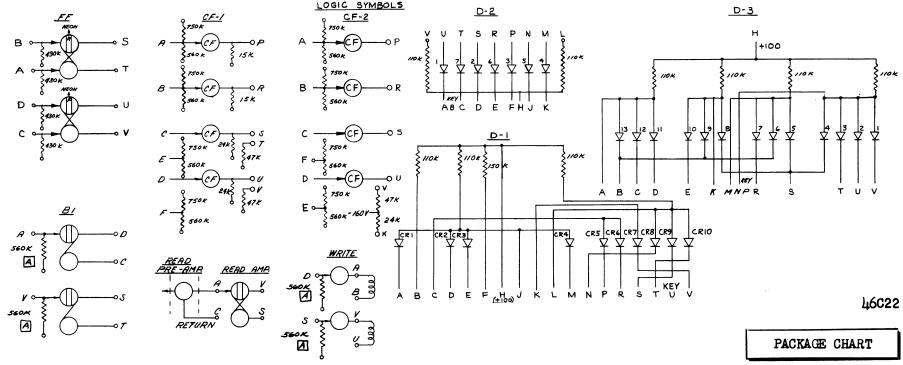

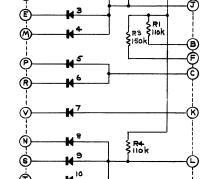

A-9a The fundamental circuits mentioned in the preceding sections (with the exception of READ PREAMPS) are physically located in standard packages distributed about the logic panels of the computer and are interconnected by appropriate inter-package wiring. The package schematics may be found on Drawings 11, 12 and 13. Drawing 10 provides an index of information pertaining to all packages.

A-9b The detailed logical block diagrams ("D-SIZED PRINTS") provide information relating to package locations and package jack pin-connections. Drawing 9 (MEMORY LINE 2) provides an example of a detailed logical block (lower left) and the schematic components and packages it represents. Package locations are designated by coordinates, a letter and a number, which are printed on the jack side of the logic panels themselves.

A-9c Common sense should render the notations self-explanatory with the exception perhaps of CLAMP PACKAGE locations. CLAMP PACKAGES are not shown on any block diagrams, but a notation external to the associated FLIP-FLOP or BUFFER-INVERTER supplies the location information. (On Drawing 9, lower left, below FLIP-FLOP 'M2", see notation 'D E22 C". This states that the CLAMP PACKAGE is located in package jack with coordinates E-22 and that pin connections D and C are used.)

A-9d A few self-imposed exercises requiring translation of information contained in the detailed block diagrams to schematic form should reveal the scheme to the reader.

A-9e Technical details of circuits not included in standard packages will be discussed as they arise.

#### A-10

#### MISCELLANEOUS

- a) PULL-DOWN resistors associated with OR gates are physically located in the package containing the load presented to the OR gate (e.g. Drawing 9 input to WRITE AMP).

- b) PULL-UP resistors associated with AND gates are located (1) within the package where the AND gate diodes are, or (2) another package, or (3) in more than one package (when paralleled). Reducing PULL-UP resistance by parallel combinations can be for the purpose of compensating for low PULL-DOWN resistance in a network of gates and/or to reduce rise time of a signal.

- c) The diodes associated with a single gate are not necessarily all located in the same package. Pre-wired combinations within Dl and D2 packages provide a variety of options minimizing wiring external to the package.

- d) The secondary of the 6.3V filament transformer which feeds all filaments is returned to -55V to minimize possibility of exceeding the heater-to-cathode voltage ratings of all tubes.

- e) Utilization of a right-to-left time axis is used as a convenience in analyzing most circuit activity (ref. G-10b).

## SECTION B

# BASIC TIMING

This section is devoted to the basic timing subdivisions and associated signals involved in the G-15D. The reader is urged to memorize the nature of the timing structure and signals before proceeding to sections to follow since Boolean algebra notations define times merely in terms of signals. It is not necessary to digest all of the details of the electronic circuits which give rise to the various timing signals before reading the sections to follow.

## G-15D IN GENERAL

B-la The G-15D is composed of a combination of logical "building blocks" discussed in Section A. The heart of the computer may be considered the magnetic drum which not only constitutes the MEMORY, but also the source of all timing signals.

B-1b All computer activities are synchronized with the basic timing signals mentioned above in a consistent orderly manner. Since such timing signals control logical activity, the time axis may be considered a standard reference in describing an event, for this reason timing warrants discussion prior to any other functions.

# TIMING SUBDIVISIONS

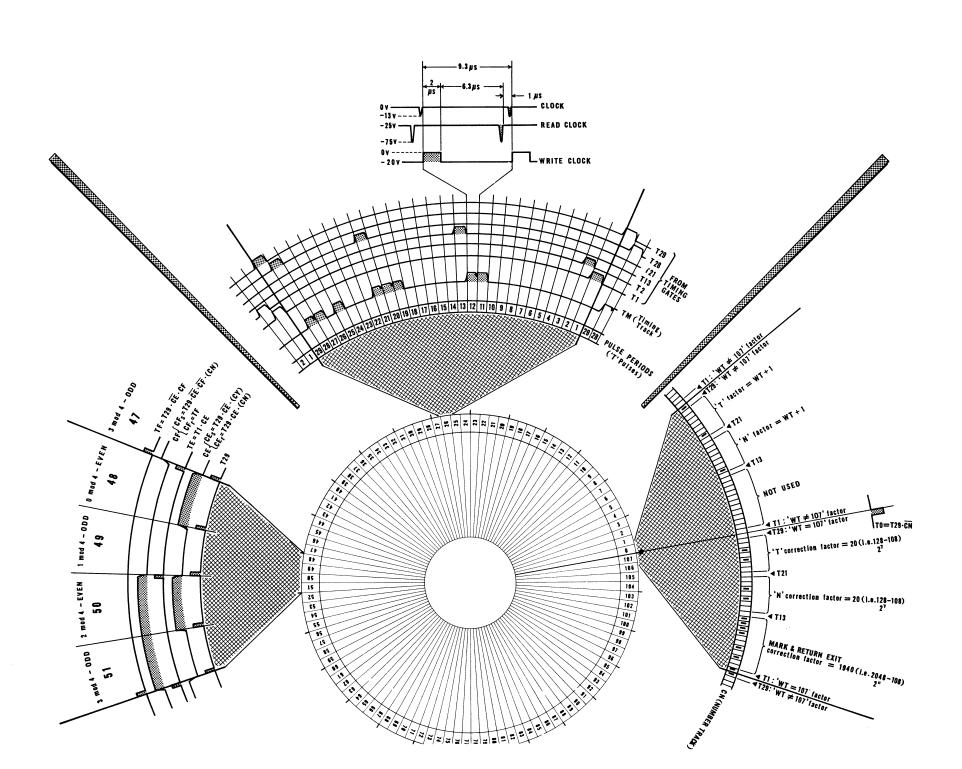

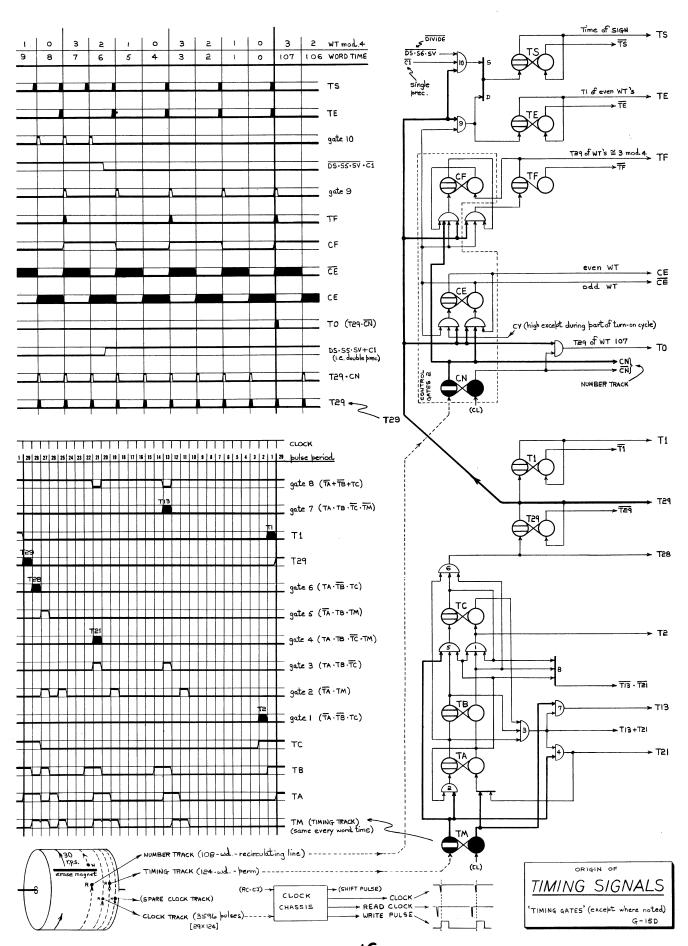

B-2a (Ref. Drawing 6) In general, time in the computer is cyclic as it is on a clock. The basic cycle is known as a DRUM CYCLE (sometimes called a LOGICAL DRUM REVOLUTION), during which the entire contents of the memory are revealed and can be subjected to alteration. A DRUM CYCLE is the recirculation time of a long (3132 bit) memory line and is arbitrarily divided into 108 WORD TIMES (WT) (as a day, which is a cycle, is divided into 24 hours.) These WORD TIMES are numbered 00 - 107.

B-2b Each WORD TIME is divided into 29 PULSE PERIODS (PP) designated T1 - T29.

B-2c Associated with each PULSE PERIOD is a trio of pulses, the most significant one of which is known as CLOCK. CLOCK pulses occur at the junction of two adjacent PULSE PERIODS. The leading edges of these CLOCK pulses cause the transitions in most flip-flops. A CLOCK pulse, the duration of which is logically insignificant (.3 - .5 microseconds), may be considered as designating either the beginning of one PULSE PERIOD or the end of the preceding one. The remaining two pulses of the trio are READ CLOCK and WRITE PULSE, and are necessary for the operation of memory lines. (Their use is restricted to internal functions of the memory lines only, hence they need not be considered as constituting significant general purpose logic pulses.)

B-2d Drawing 6 illustrates the sequence of the above mentioned elements of time. Below is a convenient analogy between the G-15D computer time reference and the familiar times of day:

1 DRUM CYCLE ----1 day

1 WORD TIME -----1 hour

1 PULSE PERIOD ------1 minute

B-2e Just as events that occur during any day may be described in terms of hours and minutes, a computer event may be designated by word time and pulse period (e.g., T29 of Word 107 is the last PULSE PERIOD of a DRUM CYCLE). Also, just as a duration of activity may be described as lasting for N hours, a computer activity may be said to last for N WORD TIMES.

B-2f Unless the computer is caused to alter its internally stored information, any subdivision of information will be available every DRUM CYCLE at the same time in terms of WORD TIME(s) and PULSE PERIOD(s).

- B-2g The basic element of information circulating in the computer is the BINARY DIGIT (abbrev: BIT). Timewise, a particular bit of information may be located by designating its PULSE PERIOD and WORD TIME.

- B-2h The basic information group consists of 29 bits and will "occupy" one WORD TIME (1 WT = 29 PP). Such a group is known as a WORD and may represent anything the programmer may designate (i. e., an instruction, a number and sign, part of a number, a control code, etc.). It is up to the programmer to determine the information content of the WORDS and their disposition. The computer itself will only do what it is instructed to do.

- B-2i In order to logically and electronically identify certain times, it is necessary to have available certain signals which will occur periodically at the designated times. For this purpose three tracks (plus a spare) are available on the drum. These tracks, in conjunction with circuits known as CLOCK CHASSIS, TIMING GATES and CONTROL GATES, yield the necessary signals. Drawing 15 indicates the system.

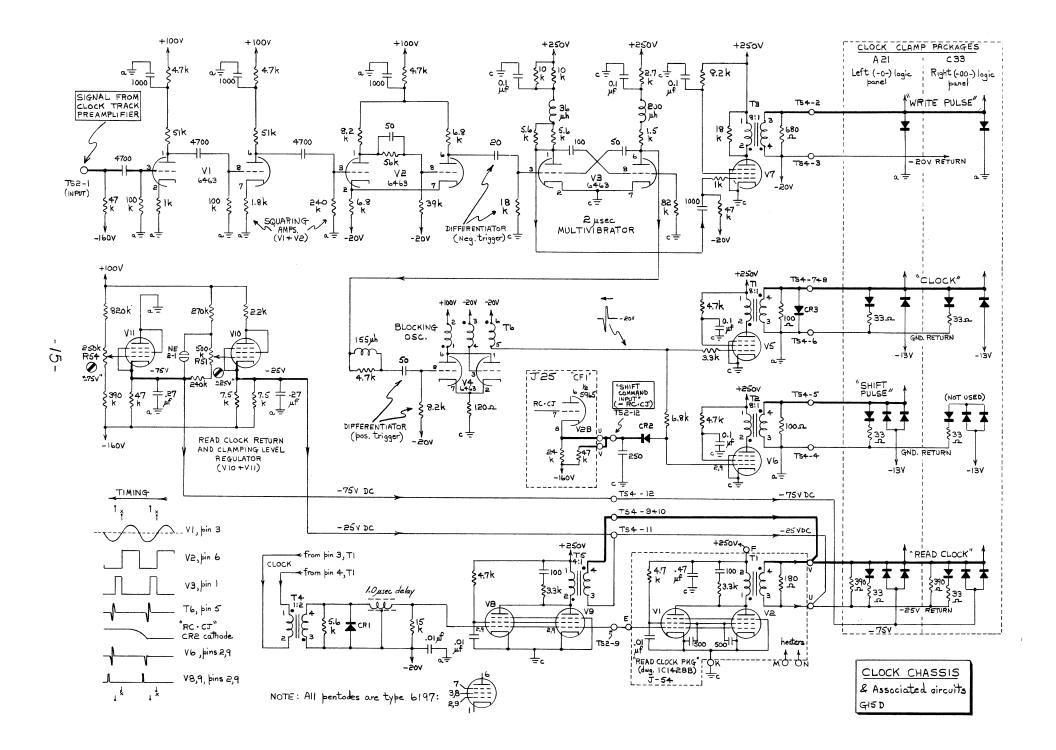

#### WRITE PULSE, CLOCK, READ CLOCK - UNCONDITIONAL

- B-3a <u>CLOCK TRACK</u>: This trio of signals occurs unconditionally every pulse period. Their origin is the CLOCK TRACK (see Drawing 15 lower left). This track is permanently recorded around the drum (i.e., it has only a reading head and hence does not recirculate). The reading wave from the head resembles a continuous sequence of sine waves. The manner in which this track is recorded is such that exactly 3596 (i.e., 124 x 29) pulses are recorded around the track in a closed circle. This recording procedure is performed at the factory and would constitute a difficult problem to re-record in the field should an accidental erasure occur. (A grid to plate short in the CLOCK TRACK preamplifier tube could cause track erasure by DC current in the read head.) For this reason a spare recorded CLOCK TRACK is provided. Should the active CLOCK TRACK become erased, the spare may be used until the normally active track is re-recorded. In the unlikely event that re-recording of an erased CLOCK TRACK is necessary, instructions for doing so in the field can be obtained from CUSTOMER ENGINEERING.

- B-3b <u>CLOCK CHASSIS</u>: The CLOCK TRACK reading head output is amplified by a pre-amplifier circuit identical to those used with other heads (Drawing 11). The preamplifier output is connected to the input of the CLOCK CHASSIS, which is located in the bottom of the computer (front center). The CLOCK CHASSIS (Drawings 14, 3D293) forms four different output pulses, three of which constitute the trio mentioned above.

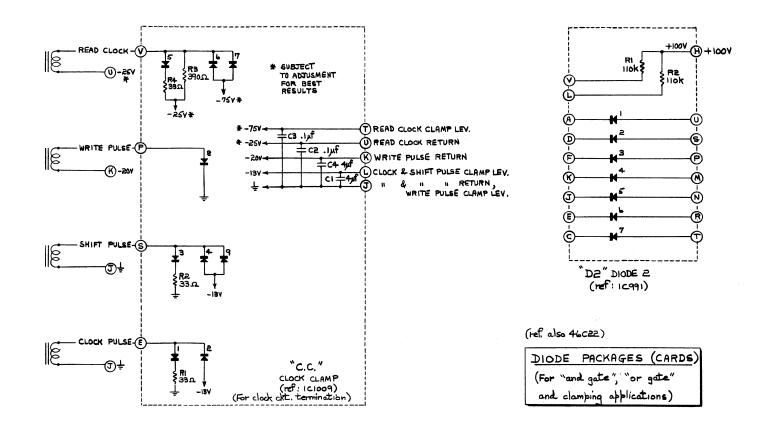

- B-3c WRITE PULSE: The preamplifier output (a series of sine waves) is "squared" by V1 and V2 in the CLOCK CHASSIS (Dwg. 14). The V2B output, differentiated, triggers multivibrator V3, which yields a 2 microsecond positive-going square wave at V3, pin 1. This 2 microsecond square wave causes power pentode V7 to conduct through its plate transformer T3. The negative end of T3's secondary (term. 4) is returned to -20V; the positive end (WRITE PULSE) is appropriately terminated to -20V and clamped at OV. Secondary termination is accomplished by (1) a 680 ohm resistor (R29) (2) the load, and (3) two CLOCK CLAMP PACKAGES one in each logic panel (see also dwg. 12). (Termination in the logic panels reduces transient problems.)

- B-3d <u>CLOCK</u>: The trailing edge of the V3 multivibrator output (pin 6) causes blocking oscillator V4 to cycle yielding a positive-going pulse of .3-.5 microsecond duration at T6, term. 5. This signal, which exists directly after the decline of the WRITE PULSE, causes power pentode V5 to conduct through plate transformer T1. The positive end of the secondary (term .3) is returned to ground; the negative end (CLOCK) is appropriately terminated to ground and clamped at -13V. Secondary termination, as in the case of WRITE PULSE is accomplished (1) in the CLOCK CHASSIS (a 100 ohm res-R28, and CR3), (2) by the load, and (3) in the CLAMP package.

- B-3e READ CLOCK: These pulses, used in the READ AMPLIFIER circuits to probe for the presence of ONES, are required to follow CLOCK pulses (unconditionally) by approximately 1 microsecond. They resemble CLOCK in shape, but have a base line of approximately -25V and reach a negative peak of -75V (clamping level). These two levels are both adjustable and may be varied for optimal results.

- B-3f To produce READ CLOCK, CLOCK is coupled to the grids of V8 and V9 (power pentodes) via T4 (for inversion and -20V return) and via a 1 microsecond delay line. The result is that the power pentodes conduct through the plate transformer T5 for .3-.5 microsecond at the appropriate time.

- B-3g Due to the nature of the load (ref. Section A-7k) and the amplitude of the READ CLOCK pulse itself, four pentode drivers are required to supply the necessary power output. V8 and V9, in the CLOCK CHASSIS itself, are supplemented by two more power pentodes in the READ CLOCK package (the only one of its kind in the computer location: J-54). The READ CLOCK package contains two power pentodes in parallel feeding one plate transformer. The pentode grids receive the same signal as those in the CLOCK CHASSIS (TS2-9); the transformer secondary is wired in parallel with the READ CLOCK output of the CLOCK CHASSIS (i.e., the T5 secondary).

- B-3h The transformers' secondary termination is accomplished in the same general manner as termination of the other signals; however, -25V and -75V are required for reference level and clamping level. V1O and V11 supply these voltages as follows:

- B-3i The cathode of V11 yields a potential which is primarily a function of the setting of potentiometer R54. This cathode potential is adjusted to approximately -75V (by R54) and should not vary significantly as a result of loading. V10's function is similar to that of V11 except that V10's cathode will be primarily a function of the setting of potentiometer R51. R51 is set to yield approximately -25V from V10's cathode.

- B-3j The reader will note that the -75V output is coupled to the V10 grid circuit and that an inter-action will exist. Furthermore, neon NE2-1 couples the entire amount of any V11 cathode voltage fluctuation to V10's grid, hence will tend to vary the -25V output level. This interaction tends to neutralize the effects of variations in clamping current required by READ CLOCK. (The amount of clamping current is a function of the total number of ONES in the memory.) In adjusting R51 and R54, a "rocking-in" procedure should be followed to allow for this inter-action. Although the two output potentials are called "-25V" and "-75", they are, in practice, adjusted to any levels in the vicinity which yield the most stable reading amplifier behavior.

B-3k A summary of these three pulses may be seen at the top of Drawing 6.

# SHIFT PULSE - CONDITIONAL

B-4 (This signal is not among the basic pulses appropriate to mention at this point; however, its formation may as well be discussed while CLOCK CHASSIS is being described.) T6, term.5, which yields CLOCK, also feeds the grid circuit of power pentode V6. However, if the SHIFT COMMAND INPUT (= RC·CJ), which is applied to CR2, is at -20V (one stable state), the grid will not be able to rise above -20V due to clamping by CR2 - hence no V6 output. If the CR2 cathode is at OV (rather than -20V) V6 will conduct and the T2 secondary will yield a signal of the same type as CLOCK. Clamping follows the same pattern as that for CLOCK except that termination only exists in one of the two logic panels since the entire load is located in that panel only. In general, SHIFT PULSE constitutes a burst of CLOCK pulses dependent upon an externally generated signal = RC·CJ· (Sec·C-5b.)

## TIMING PULSES - THE TIMING TRACK (TM)

- B-5a <u>T1, T2, T13, T21, T28 and T29</u>: These pulses are required to identify their respective pulse periods every word time. The TIMING TRACK (TM), a permanently recorded track, supplies the necessary information to signify these pulses. The TIMING TRACK, like the CLOCK TRACK, is recorded at the factory. It repeats the same digital configuration 124 times around the periphery of the drum in a closed loop. (It is not necessary for this track to recirculate to stay in step with a DRUM CYCLE since the digital configuration in <u>all</u> WORD TIMES is <u>identical</u> and the only requirement is that an integral number of word times be recorded around the drum.)

- B-5b The subdivision of each WORD TIME is illustrated on Drawing 6 (see TIMING TRACK.) The hardware is indicated on Drawing 15. The output of the TIMING TRACK READING FLIP-FLOP (TM) feeds an array of flip-flops and gates in the TIMING GATES. The key outputs from the circuit are high during T1, T2, T13, T21, T28 and T29. Generation of these signals from TM is illustrated on the timing chart on Drawing 15 lower left. The circuit is self-synchronizing.

- B-5c It is not necessary to have a spare TIMING TRACK as was the case with the CLOCK TRACK. A new TIMING TRACK may be recorded in the field if an accidental erasure occurs. If the case arises, the procedure can be obtained from CUSTOMER ENGINEERING.

## WORD TIME INFORMATION - THE NUMBER TRACK (CN)

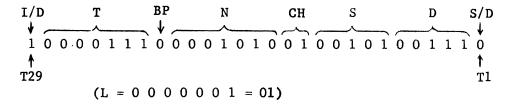

B-6a The NUMBER TRACK is the word time reference track and supplies the computer with several pieces of information. Drawing 6 (right) illustrates the contents of all words. The purpose of all bits of information will be discussed in this manual as the need for them arises. At this point only one bit need be mentioned: the bit stored at T29 time during each word time. This bit is a ONE during all word times other than WT 107, but during WT 107 itself the bit is a ZERO. The latter may be defined in Boolean algebra terminology as T29 °CN, where CN is the READING FLIP-FLOP of the NUMBER TRACK.

This particular signal comes high during the last PULSE PERIOD of a DRUM CYCLE and constitutes an index or ORIGIN PULSE. The signal is called TO (i.e., TO = T29·CN), and is used for many purposes. Associated hardware may be found on Drawing 15.

B-6b Needless to say, since an actual physical drum revolution and a DRUM CYCLE differ (by a factor = 124/108), it is necessary that the NUMBER TRACK be a recirculating memory line so its contents will "keep step" with DRUM CYCLES. Since power turn-off involves erasure of all recirculating memory lines, a scheme of renewing the NUMBER TRACK during the power turn-on cycle is provided. This is discussed in Section G.

B-6c Once TO is established, a circuit in the CONTROL GATES (Drawing 15) involving the CE and CF flip-flops yields more timing signals. The CE flip-flop (synchronized by the NUMBER TRACK) yields an output "CE" which is high during EVEN word times only. (Obviously "CE" will be high during ODD word times.) CF will, under control of CE, etc., be high during word times congruent to 2 and 3 modulo 4.

B-6d CE and CF, once synchronized, will allow the formation of certain other basic timing pulses in the TIMING GATES as follows:

TE = T1·CE (i.e., T1 of EVEN word times) TF = T29· $\overline{\text{CE}}$ ·CF (i.e., T29 of words congruent to 3 mod. 4)

B-6e The reader will note that the signal TE, which has been defined as Tl·CE is actually formed by T29·CE delayed one pulse period. Frequently the means of forming a signal is not the most straight-forward one. This can usually be attributed to conservation of hardware or preservation of waveshape. Ordinarily a signal is defined by Boolean algebra notation in terms of the conditions under which it occurs -- such notation usually follows the method whereby the signal is formed, but not necessarily.

B-6f Drawings 15 (upper left) and 6 (left) illustrate the signals just encountered. The reasons for them will become apparent later. At this point the reader should attempt to memorize the contents of Drawing 6 with the exception of details of the NUMBER TRACK not discussed in this section. These basic timing signals represent the time references for most computer functions to be discussed in sections to follow.

# SECTION C

# GENERAL COMPUTER ACTIVITY

This section is devoted to a variety of concepts and circuits. The circuits covered are controlled to some extent by the SPECIAL COMMANDS and other functions to be covered in sections to follow. The sequence of presentation in this particular section is less orderly than that to be found in others. This is necessary to present pre-requisite material first and to minimize forward references.

### COMPUTER SEQUENCE OF ACTIVITY

- C-la Unless the computer is idle, it is engaged in a computing cycle illustrated on Drawing 18. The productive portion of the cycle takes place during the time the computer is in the TRANSFER (TR) state. It is during this time (an integral number of WORD TIMES) that an operation is executed. The TRANSFER state is sometimes referred to as the EXECUTE state.

- C-1b Needless to say, the computer must know the nature of the operation to be executed; this is determined during the READ COMMAND (RC) state. During this state (lasting one WORD TIME), a command is "read" from a predetermined word location of a pre-determined line (ref. Sec. D-6b). The instant the final bit of the command (T29·RC) has been read, the command has been decoded and has set up all the necessary electronic paths for proper execution of the operation designated by the command.

- C-1c Once a command has been read (and decoded) it may be executed immediately provided the command itself calls for immediate execution. If the command is not an IMMEDIATE command it is DEFERRED. As Drawing 18 illustrates, if a command is IMMEDIATE, as soon as the command is read, the TRANSFER state is initiated. If DEFERRED, the computer will rest in the WAIT TO TRANSFER (WTR) state for an integral number of word times until information in the command itself calls for the TRANSFER state.

- C-ld How long the computer will remain in the TRANSFER state is also a function of the command.

- C-le Once the TRANSFER state is terminated, the computer will advance to the READ COMMAND state immediately or after an integral number of word times in the WAIT TO READ COMMAND (WRC) state. At this point the cycle repeats unless the computer is purposely caused to stop; in this case it will idle in the WAIT TO READ COMMAND state indefinitely.

## COMMANDS

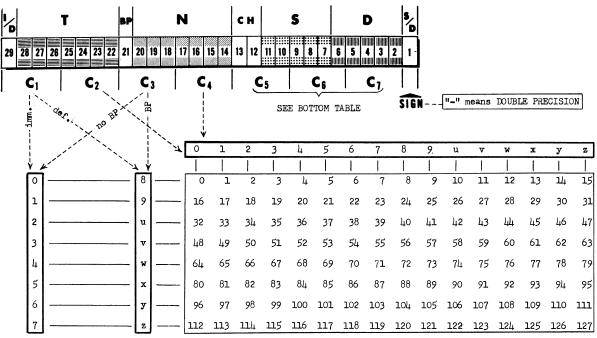

C-2a A command, as mentioned above, controls the computer in regard to timing (i.e., advancement from state to state), and in regard to the nature of the operation to be performed during the designated time of TRANSFER. A command is considered subdivided into two general portions: the STATIC PORTION and the DYNAMIC PORTION. (These names not only describe their purposes, but also their treatment within the computer.) Breakdown of a command is illustrated on Drawing 5 (top.)

# THE STATIC PORTION: 13 bits (T1 - T13)

C-2b SOURCE AND DESTINATION (S & D): This information is contained in 10 bits (T2 - T11) which can assume 1024 (i.e.  $2^{10}$ ) different configurations, hence there are 1024 different SOURCE - DESTINATION combinations possible. Individually the SOURCE and DESTINATION portions can express SOURCES and DESTINATIONS numbered 00 - 31 (i.e., 00000 - 11111 in binary). If the DESTINATION is specified 00 - 30, the command calls for a transfer of information from a SOURCE (00-31) to the designated destination. However, if DESTINATION is selected equal to 31, the SOURCE number (00 - 31) specifies a SPECIAL COMMAND, not necessarily involving transfer of information at all.

- C-2c CHARACTERISTIC (CH): This information is contained in 2 bits (T12 and T13) and can assume 4 (i.e.,  $2^2$ ) different configurations, designating four options in performing a command defined by S and D. The manner in which the CH code is interpreted (hence, its result), is a function of the particular S and D selected.

- C-2d SINGLE OR DOUBLE PRECISION (S/D) bit: This bit (T1) is the only remaining bit of the STATIC PORTION of a command. Its functions depend to some extent upon the remainder of the command (including the DYNAMIC PORTION). It is primarily concerned with setting up logical circuits to comply with timing requirements of SINGLE and DOUBLE precision operations; it does, however, serve other purposes.

# THE DYNAMIC PORTION: 16 bits (T14 - T29)

- C-2e IMMEDIATE or DEFERRED (I/D) bit: This bit (T29) controls whether the TRANSFER state will be initiated directly after the command is read or wait (in the WAIT TO TRANSFER state) until some other factor calls for it. A "O" specifies IMMEDIATE; a "1", DEFERRED.

- C-2f TIMING NUMBER (T): This information is contained in 7 bits (T22 T28) and can express a number from 00 127. This is a controlling factor in either initiating or terminating TRANSFER. The manner in which it is interpreted depends upon other factors in the command.

- C-2g NEXT COMMAND LOCATION (N): This information is contained in 7 bits (T14 T20) and is used to express a number from 00 107. These numbers refer to the WORD TIME during which the command to follow is to be read after the current command has been concluded.

- C-2h BREAK POINT (BP) bit: This bit (T21) provides a programmable method of interrupting operation of the computer after the command has been executed. The setting of the COMPUTE switch on the BP position will cause the computer to idle in the WAIT TO READ COMMAND state after the TRANSFER state has been terminated.

- C-2i (LOCATION of command) (L): This is not actually written as part of the command but is a piece of information associated with it. L is the word time (00 107) during which the command is read and usually is N of the previous command.

## COMMANDS-SUMMARY

C-2j Commands consist of several subdivisions, all of which contribute to define and control the operation to be performed. The programmer is required to account for all 29 bits of a command; the engineer should be able to determine exactly what will happen within the computer as the result of any command whether or not its composition is legitimate.

## NUMBERS

C-3a Ordinarily, the words to which commands make reference contain numbers or portions of numbers. Any word (in the memory) to which a program never makes reference can contain anything--usually all ZEROS.

Numbers are of two general types: SINGLE PRECISION and DOUBLE PRECISION.

- C-3b SINGLE PRECISION numbers are held entirely within a single word and consist of a total of 29 bits as follows: 28 (T2 T29) to express the number and 1 bit (T1) to hold the sign (SIGN BIT = "0" means +; "1" means -). A single precision number can, by virtue of 28 bits, accommodate  $2^{28}$  different binary configurations which amounts to precision up to one part in 268,435,455 (i.e. 1 part in  $2^{28}-1$ ).

- C-3c DOUBLE PRECISION numbers require two words and consist of an EVEN numbered word (time) for the lowest order portion and the following ODD numbered word for the highest order portion. Sign is held in the T1 position of the EVEN word (TE =  $T1 \cdot CE$ ), and the remaining 57 bits are devoted to expressing the number. The numerical portion can assume  $2^{57}$  different configurations amounting to precision of one part in 144,115,188,075,855.871 (i.e. 1 part in  $2^{57}$ -1).

- C-3d When an operation dealing with SINGLE PRECISION numbers is executed, T1 pulses constitute the TS or SIGN TIME pulse; DOUBLE PRECISION operations require TS to consist of TE (i.e., T1·CE). This is one function of the S/D precision bit of a command (ref. drawing 15-upper right).

- C-3e Whenever a number is transferred from a SOURCE to a DESTINATION, and is subject to modification in the INVERTING GATES, the modification is a function of the SIGN associated with each individual number being transferred. Obviously pulses interrogating the signs of numbers must occur at the appropriate time. Proper programming of the S/D precision bit of a command therefore is essential.

## COMPLEMENTATION OF NUMBERS

- C-3f Numbers are normally to be found (in memory) in terms of ABSOLUTE VALUE and SIGN. Furthermore, the BINARY POINT may be assumed to be to the left of the highest order bit of each number, rendering the highest order bit in the  $2^{-1}$  column. (A programmed scaling factor can render such a fractional number a multiplier for 2 raised to any power, hence, order of magnitude is unrestricted this is the programmer's concern.)

- C-3g Should a number be negative, it is desirable (in order to facilitate certain operations such as addition) to convert it to COMPLEMENT form, such that given a fractional number = .N, its COMPLEMENT is (1-.N). The COMPLEMENT represents a number, which if increased by a positive value =.N, will yield all ZEROS in its fractional part and an END CARRY into the imaginary 2° position. Such an END CARRY, if added to the imaginary "1" in the 2° position, would yield a sum bit of "0" and an end carry which will be killed.

- C-3h Evidence of the imaginary "1" in the 2° position is the content of the SIGN BIT. (i.e., a "1" in the sign bit represents a negative number; if the number is in complement form, the "1" (from "1-.N") is held in the SIGN BIT.) Ideally the SIGN BIT, which has a quasi-numerical significance, should appear in a bit location following the highest order numerical bit (2<sup>-1</sup>) since it represents a state of 2°. However, it is also vital that this sign bit precede the number (i.e., be at the lowest order end) to

facilitate the activity in the INVERTING GATES which must know the sign of a number prior to its transmission from EB to IB (ref. Sec. C-7a).

- C-3i The sign then, is applied to the lowest order end of a number for the sake of the INVERTING GATES, but may, when necessary, be influenced by an end carry from the 2<sup>-1</sup> position in arithmetic operations as will be seen later in Sections C-10m-o.

- C-3j To obtain the COMPLEMENT of a number the procedure is: Starting with the lowest order digit and proceeding up, pass all bits unchanged up to and including the first "l" bit; thereafter invert the bits to follow. Example:

.N .0110100 1-.N .1001100

An analysis of the operation is as follows:

$\begin{array}{cccc}

1-2^{-n} & .1111111 \\

-.N & -.0110100 \\

1-2^{-n}-.N & .1001011 \\

+2^{-n}corr. & +.0000001 \\

\hline

1-.N & .1001100

\end{array}$

This may appear to be a round-about method of obtaining 1-.N, but it does not necessitate a subtractor.

- C-3k The procedure of "PASS ALL BITS UNCHANGED UP TO AND INCLUDING THE FIRST "1" accommodates the subtraction of .N from all ONES and also the  $\pm 2^{-n}$  correction. "INVERSION FOLLOWING THE FIRST "1" handles the higher order portion of the subtraction from all ONES.

- C-31 This scheme is know as the "2's complement system". (The "1's Complement System" does not accommodate the +2<sup>-n</sup> correction). When we say take the "1's complement of a <u>number</u>", this implies a binary point location, hence the value of the highest order numerical bit.

- C-3m (The terms "'1's' complement system" and "1's complement of a number" do not necessarily mean the same thing. The G-15D obtains complements of numbers by employing the "2's complement system"; by placing the binary point to the left of the highest order bit a complement represents 1-.N hence is the "1's complement of a fractional number.") In an addition of two numbers of unlike sign, the positive number should be uncomplemented (i.e., NORMAL) and the negative number should be complemented. As a result of addition, the imaginary "1" in the 2° position will either remain, indicating a negative sum in COMPLEMENT form, or be changed to "0" indicating positive sum in NORMAL form. An end carry from the highest order numerical bit position (2-1) will decide the fate of the imaginary "1" in 20 (ref. dwg. 25).

- C-3n The end carry from  $2^{-1}$  (T29 position of a word) will be added to the sign bit " $2^{0}$ " (T1 position of a word) by virtue of the structure of the adders, which allow the sign position to be available for processing directly after the T29 position. Details of this will be explained under ADDERS (Sec. C-10m-o.)

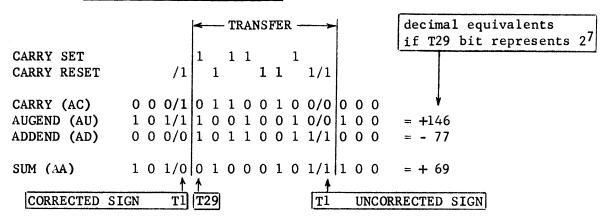

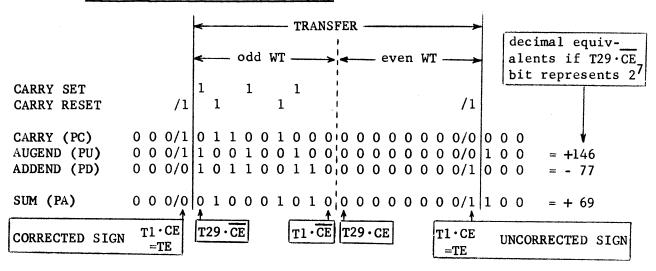

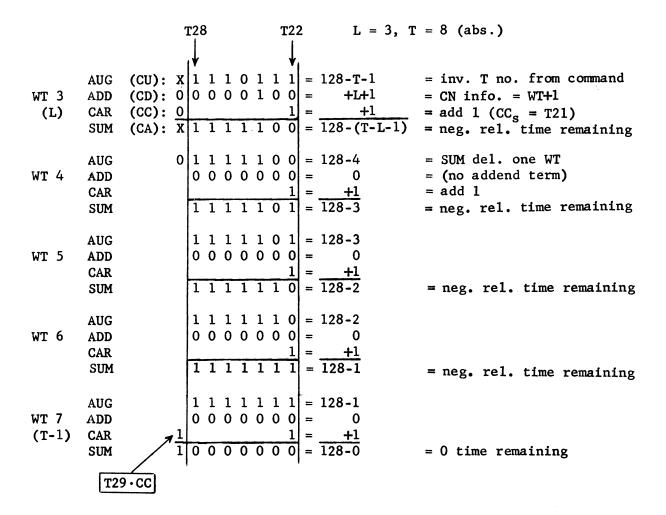

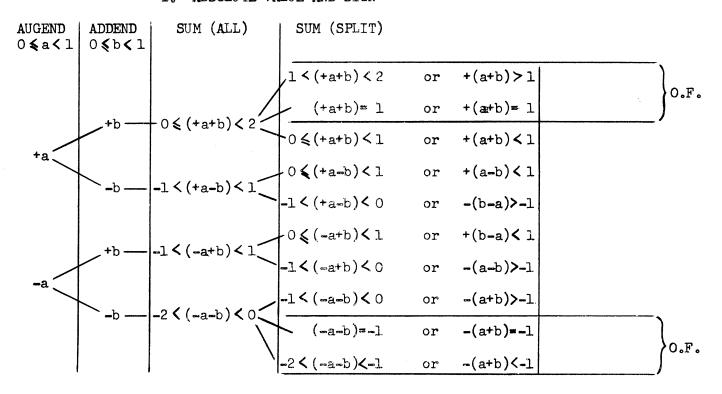

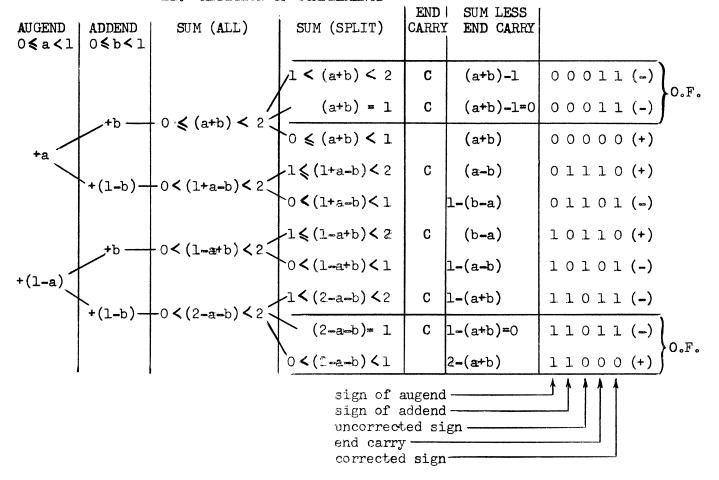

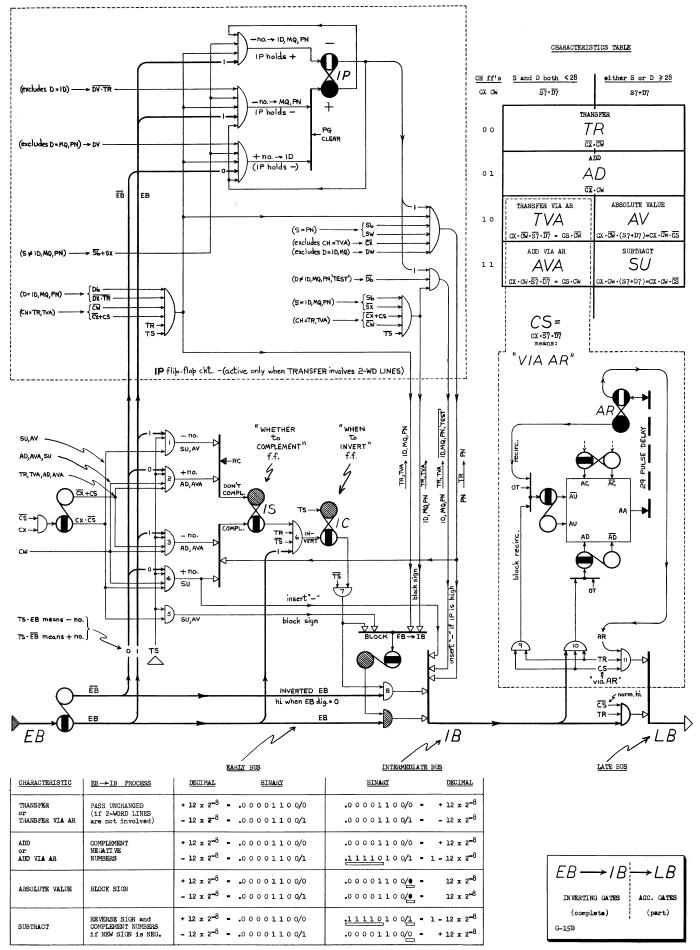

C-30 Drawing 24 indicates the results of additions of two fractional numbers, a and b. Using the complementation scheme to deal with negative numbers, the chart reveals that all sums (unless they exceed a fractional value and constitute overflows) will be either in NORMAL or COMPLEMENT form and will contain the desired sign bit as CORRECTED SIGN. The results are a function of the signs and relative magnitudes of the AUGEND and ADDEND. Drawing 25 illustrates actual binary examples of the complementation and addition procedure (note that in MEMORY numbers are in terms of SIGN and ABSOLUTE VALUE: in the ADDER itself, NORMALS and COMPLEMENTS appear when appropriate).

# SOURCES AND DESTINATIONS IN GENERAL

- C-4a The simplest commands are those involving a transfer of information from a SOURCE (usually one memory line) to a DESTINATION (also usually one memory line). A list of SOURCES and DESTINATIONS is provided on Drawing 2. Unless DESTINATION = 31 is selected, the information content of the selected SOURCE will be copied into the DESTINATION subject to control of intervening circuits, which are under the control of the command. Except when DESTINATIONS AR+ and PN+ are selected, the original contents of the DESTINATION line are replaced by the incoming information (ref. Secs. A-7 and C-10h).

- C-4b For example: if SOURCE 08, DESTINATION 16, and CHARACTERISTIC O are selected, this means that during the time of TRANSFER, the READING FLIP-FLOP of MEMORY LINE 08 will be coupled indirectly to the writing circuit of MEMORY LINE 16, while recirculation of MEMORY LINE 16 is blocked.

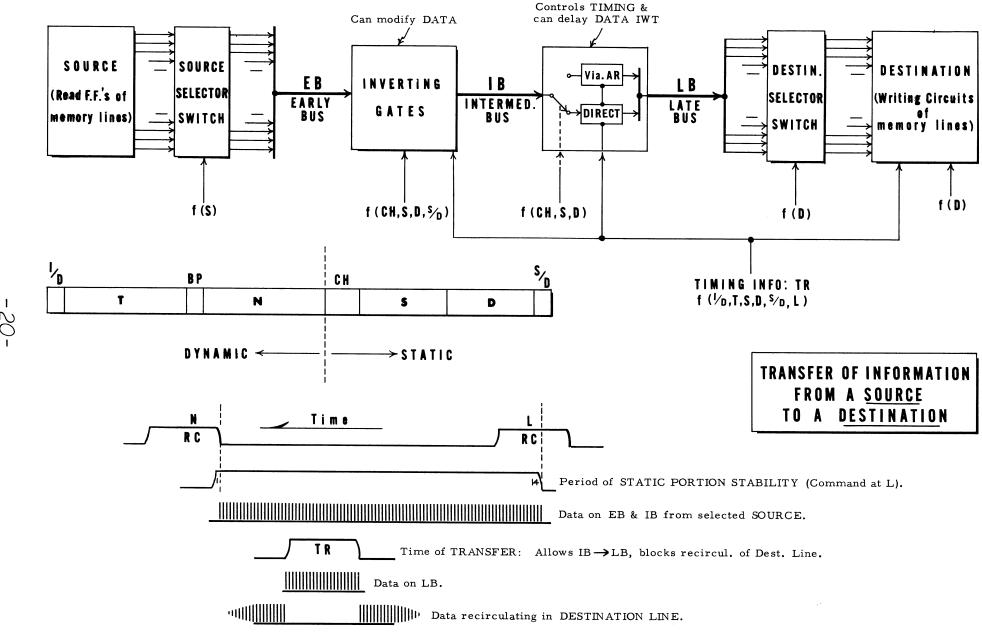

- C-4c Drawing 20 illustrates the information flow from the READING FLIP-FLOP of the SOURCE line to the writing circuit of the DESTINATION line. The blocks called SOURCE SELECTOR SWITCH and DESTINATION SELECTOR SWITCH are merely portions of the individual memory lines treated collectively. As the notations suggest, activities of the blocks are a function of one or more factors contained in the command being processed.

- C-4d Whenever a SOURCE is selected, from the time the STATIC PORTION of a command is read until it is replaced by that of another command, the designated SOURCE will send its information to the EB (EARLY BUS), which is nothing more than a multi-term OR gate. In case SOURCE 27, 30 or 31 is selected, more than one SOURCE line is coupled to the EB; the Boolean algebra notations on Drawing 2 indicate the logical combinations. These combinations are sometimes referred to as the LOGICAL SOURCES; commands employing them are known as EXTRACT COMMANDS. SOURCE 29 will serve to supply nothing but ZEROS to the EARLY BUS unless an extra attachment INPUT-OUTPUT REGISTER is plugged into the G-15D.

- C-4e EB (EARLY BUS) information appears on the IB (INTERMEDIATE BUS) subject to modification by the INVERTING GATES. The INVERTING GATES are controlled by command information (ref. Sec. C-7b).

- C-4f IB (INTERMEDIATE BUS) information can appear on the LB (LATE BUS) during the time of TRANSFER only. This time-gating by TRANSFER prevents the selected DESTINATION from being influenced at times other than the time of TRANSFER.

# SPECIAL DESTINATION 31

C-4g When DESTINATION 31 is selected, the SOURCE code no longer represents a SOURCE to feed a DESTINATION (although the corresponding SOURCE line harmlessly feeds the EB). The SOURCE code designates an operation (or a choice of operations from which one may be selected by the CHARACTERISTIC code). Drawing 3 lists the operations available. (These will be described later in Sec. D.)

# THE CONTROL SWITCH

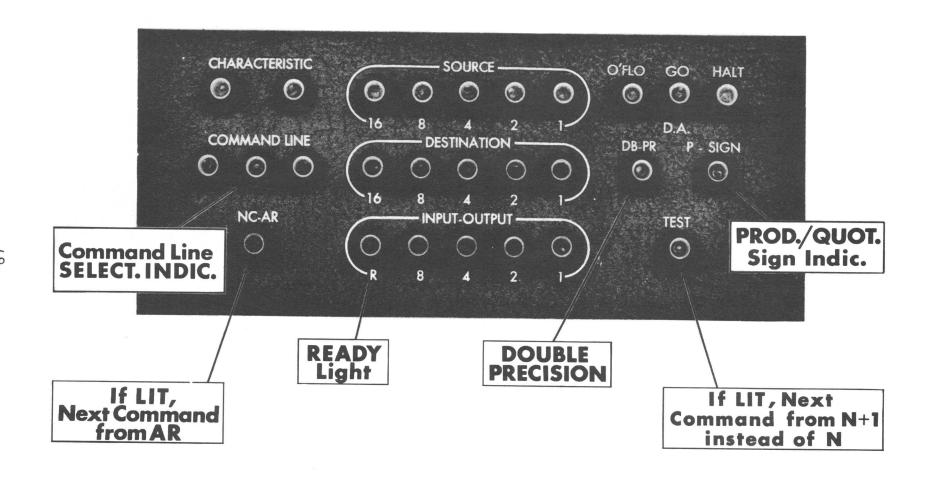

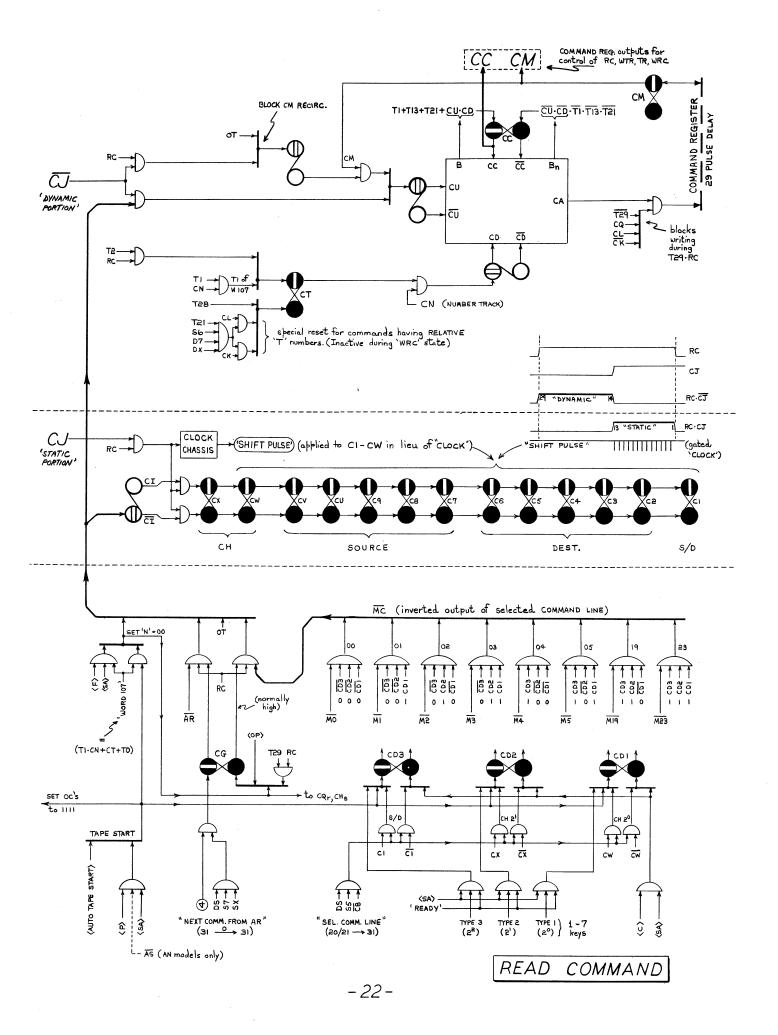

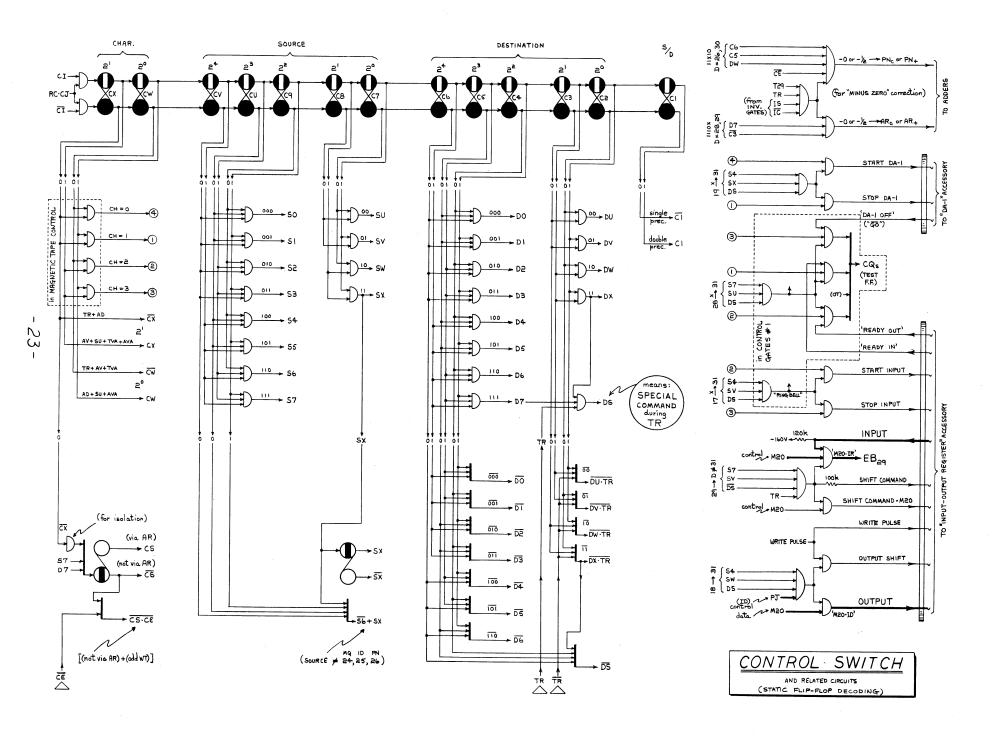

- C-5a When a command is read, the STATIC PORTION (T1-T13), which is concerned primarily with the routing of information, is registered in a static register consisting of 13 flip-flops. These are located in the CONTROL SWITCH (Drawing 23), and the entire contents are exhibited on the neon panel (Drawing 17).

- C-5b Alteration of information in these flip-flops is possible only during the first 13 pulse periods of the READ COMMAND state defined by RC·CJ. The CX flip-flop can only be triggered when RC·CJ qualifies the AND gates controlling it; the remaining 12 flip-flops can only change state when gated CLOCK pulses are applied to them. These CLOCK pulses are the SHIFT PULSES mentioned in Section B-4. The term permitting generation of these SHIFT PULSES is actually RC·CJ. In conclusion, when a command is read these 13 STATIC FLIP-FLOPS will register T1-T13 (the STATIC PORTION) of the command and will continue to hold the information until equivalent information from the next command replaces it.

- C-5c The method of feeding this information into the 13 flip-flops is shown on Drawing 22. Once any information resides in the flip-flops, an array of gates decodes the contents, delivering a variety of signals to control the activities throughout the computer. The decoding scheme is shown on Drawing 23. The output signals are stabilized after T13 of RC, and will remain stable until the end of T1 of the next RC. (During the RC.CJ period, when the flip-flops experience transition, the output signals are not interrogated.)

- C-5d A combination of two output signals (Drawing 23) will precisely define a SOURCE or DESTINATION number. For instance DO·DW defines DESTINATION 02 since it is equivalent to  $\overline{C6 \cdot C5} \cdot \overline{C4} \cdot C3 \cdot \overline{C2}$  (i.e.,  $00010_2$  or  $02_{10}$  in the DESTINATION flip-flops of the CONTROL SWITCH). Such a signal combination (DO·DW) is used to allow the LATE BUS (LB) to write on LINE 02. (Note on Drawing 9 lower left that DO·DW·LB is the writing term of LINE 02 when selected as DESTINATION.)

- C-5e Similarly, SO.SW SOURCE codes representing configuration 00010 in the SOURCE flip-flops, are suitable for controlling LINE 02 as a SOURCE. (Note on Drawing 9 that SO.SW.M2 feeds the EARLY BUS when LINE 02 is selected as SOURCE.)

- C-5f By forming in this central location (CONTROL SWITCH) key signals to feed the extremities of the computer, economy in wiring and components at the extremities is achieved.

The signal DS (Drawing 23) is an example of central formation of a signal for use in many locations. DS=D7·DX·TR (i.e., a signal high during TRANSFER if DESTINATION 31 is selected). This signal "operates" the SPECIAL COMMANDS listed on Drawing 3. For instance, to perform the special command "HALT", SOURCE 16 and DESTINATION 31 must be specified (symbol: 16 — 31). When this configuration enters the 13 flip-flops and when the TRANSFER state arises the signals S4·SU·DS will be present. (S4·SU·DS = S4·SU·D7·DX·TR = CV·CU·C9·C8·C7·C6·C5·C4·C3·C2·TR). The 3-term signal S4·SU·DS (derived from a multitude of terms) is all that is required to initiate the "HALT" command (note dwg. 30 - upper left). The same ingredients, S4, SU, & DS can be used to perform other functions. In case any one signal (such as DS) feeds many loads, it may be "boosted" by simple devices such as cathode-followers; detailed prints supply this type of information.

## TRANSFER TIMING

- C-6a The DYNAMIC PORTION of a command is concerned with establishing the timing control of the TRANSFER state (TR); however, how the DYNAMIC PORTION is interpreted depends to some extent upon the STATIC PORTION (which resides in the CONTROL SWITCH after T13·RC).

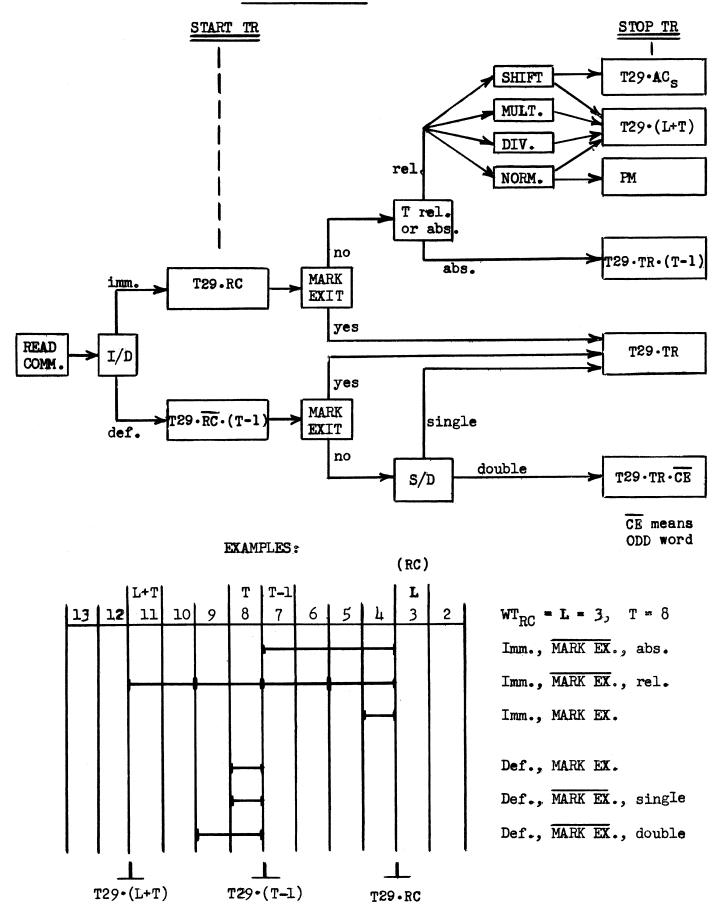

- C-6b Drawing 19 illustrates by flow-diagram and examples the various TR timing control options. The DYNAMIC PORTION of a command holds I/D (T29) and T (T28 T22) information. Furthermore, the factor L (WTRC) has some control on timing. (The N and BP factors, also in the DYNAMIC PORTION, have no bearing on TR timing).

- C-6c As the flow diagram shows, I/D and L or T control the initiation of TR regardless of the STATIC PORTION of the command. Termination of TR is a function of the configuration in the STATIC PORTION (i.e., MARK EXIT? SHIFT? MULT? DIV? NORM? S/D?). The CONTROL SWITCH supplies the necessary terms to determine mode of termination; once determined, the termination is performed by the signals occurring at the times shown on Drawing 19.

- C-6d In the majority of cases, the "Imm., MARK EX., abs.", "Def., MARK EX., single", or "Def., MARK EX., double" timing will hold true. Note that in the case of SINGLE PRECISION DEFERRED commands, TR lasts one word time only (during WT = T) and in the case of DOUBLE PRECISION, DEFERRED commands, TR lasts 2 word times (T and T+1), provided T is an EVEN number. This is compatible with processing numbers of corresponding precisions.

- C-6e IMMEDIATE commands can give rise to TR lasting many word times, hence are capable of processing blocks of numbers (hence, the term BLOCK TRANSFER used in programming language). It can be seen that the S/D bit has no bearing on TR timing in the IMMEDIATE cases; nevertheless, its control over the TS (TIME OF SIGN) signal remains unaffected.

- C-6f The signals causing transition (at the bottom of the timing diagram) are generated in the COMMAND REGISTER and associated circuits under the control of the STATIC and DYNAMIC portions of the command. Formation of these signals will be discussed in Section C-17.

## THE INVERTING GATES (EB $\rightarrow$ IB)

C-7a As was mentioned in Sec. C-4e, information may be modified in transit from the EARLY BUS (EB) to the INTERMEDIATE BUS (IB). The modification is under the control of (1) the STATIC PORTION of a command (hence the CONTROL SWITCH), and (2) the SIGNS of the NUMBERS themselves which are being transferred. Since the SIGN bit precedes the number, it is capable of controlling the circuits which process the number to follow.

C-7b The CH (CHARACTERISTIC) bits of the command, in conjunction with the S (SOURCE) and D (DESTINATION) codes control the nature of the modification in accordance with the CHARACTERISTICS TABLE on Drawing 26 upper right. By means of Boolean algebra notation, referring to CONTROL SWITCH output terms, the following transfer characteristics may be obtained:

| Case I   | $ \frac{\overrightarrow{CX} \cdot \overrightarrow{CW}}{\overrightarrow{CX} \cdot \overrightarrow{CW} \cdot \overrightarrow{S7} \cdot \overrightarrow{D7}} $ | TRANSFER<br>TRANSFER VIA AR | ABBREV.<br>TR<br>TVA |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|

| Case II  | CX · CW<br>CX · CW · S7 · D7                                                                                                                                | ADD<br>ADD VIA AR           | AD<br>AVA            |