| "C" | s/D | СН | Meaning                                                                                                                                                                                                                              |

|-----|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     |    | mented, if that was called for originally, to the second word of the double-precision receiving address.                                                                                                                             |

| 7   | 1   | 11 | If 28 or 29 is specified as receiving address, change sign of first word of double-precision operand and transfer it via the inverting gates to AR. Then transfer the second word, all 29 bits, via the inverting gates also, to AR. |

\* Note: If this table is being used for reference, see page 82.

Notice here that the operations listed so far do not constitute the complete list of operations available in the computer; to name two very important ones which were not included, <u>multiply</u> and <u>divide</u>. We will see later how these operations, and many others, are called for, but first we must complete the description of the basic parts of a command.

So far all we have discussed are operations. Another part of each command is the address of the operand: the computer must be told on which number in its memory the operation is to be performed. Remember that it has been pointed out that an exact address in memory consists of a line number plus a word number, called a word-time. The line in which the operand is located is called the "source", and, in the layout of a command on page 61, this number is referred to as "S". If the line containing the operand is called a source, the obvious name for the line which will receive the transferred word is "destination". This is referred to in the layout of a command as "D". S and D can each range from 00 through 31, although the meaning of 31 has not yet been explained. In binary (all words in memory are in binary), 5 bits are required to represent the decimal number 31.

$$^{31}(10) = ^{11111}(2)$$

Notice that five bits have been allotted to both S and D. Since no address is complete without a word-time, there must be an allocation for this in a command. There is; it is "T". There are 108 word-times per long-line. No other line in memory requires more; in fact, no other line in memory requires nearly as many, so the range 00 - 107 (u7) will be sufficient.

$$107_{(10)} = 6v_{(16)} = 1101011_{(2)}$$

so seven bits will be sufficient for T; notice that seven have been allowed. Now, is T combined with S to form an address, or with D? The answer is: with both! So we see that, if the straight transfer

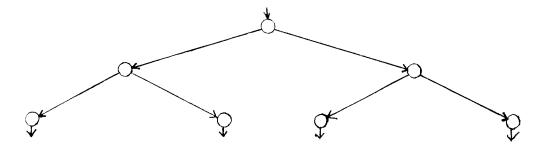

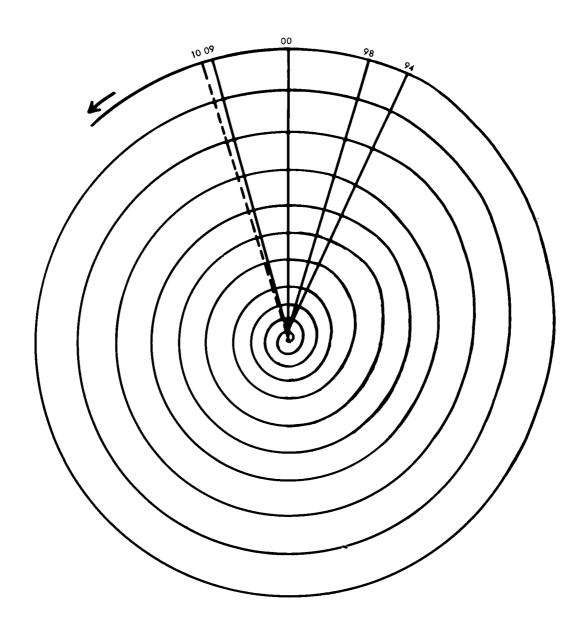

of a single word from one long line to another is called for, the word being transferred will, upon execution of the command, occupy the same word-time in the new line as it does in the old. The drawing below will clarify this.

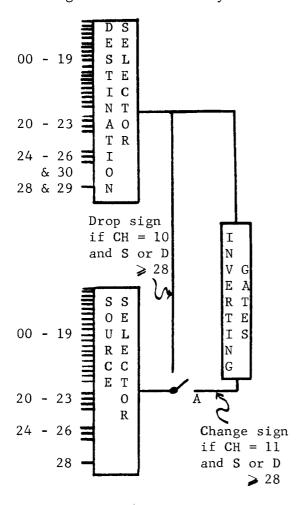

As long as no command is being executed, the read-heads for each line in memory (there are 28 of them plus the number track) are connected to the corresponding write-heads, and bits, words, and whole lines are recirculating merrily along. This is all going on behind the drawing to the left. But then, when a command is exeuted, things begin to happen. no commands were ever executed, it would be an easy matter to understand what's going on in the computer, but computers, as a rule, don't do much of anything useful if no commands are being executed. When a command is executed, it has a source (S), a destination (D), a word-time (T) during which it is to be executed, and an operation (CH and S/D), and other things we won't mention here. During wordtime T a word is entering the source selector from each line in memory, as shown in the drawing. Notice that only one line number for PN is shown (26, not 30); this is because PN can be a source of data in only one capacity (as a storage location).

In the case of AR, 29 is an illegal line number for AR as a source. AR must be referred to as line 28 when being treated as a source. The source selector now has a word from each line, and it must pick out the correct one and ignore the rest. Of course it can do this, because the command has informed it of the line specified by S. The word from memory whose address is S.T leaves the selector, on its way to be processed.

Processing actually consists of being transferred back to memory again, over the proper circuit, which, in some cases, will perform an addition of bits. It also may consist of complementing a negative number. Part of the processing will be called for by the CH in the command. Depending on the value of CH, switch A in the drawing may be in one position or the other, causing the word being transferred to pass around or through the inverting gates. The word then arrives at the destination selector. The destination selector will usually disconnect the readhead for the line chosen as D from the corresponding write-head, pre-

venting recirculation of word T in that line. It will allow all other read-write connections to remain intact, so that word T in all other lines is being recirculated. It will then take the word it has received from the source selector and feed it to the proper line. Thus, what was originally in the destination line at word-time T is lost and replaced with word T from the source line. The source line has recirculated and still contains word T. If the destination is either 29 or 30, the original contents of the destination line at word time T is not lost, but is added to word T arriving from the destination selector.

In order to hold down the size of this book to a single volume, we will leave it to the reader to trace through this procedure for each operation code listed in the preceding table.

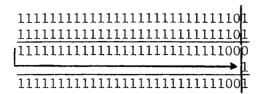

### IMMEDIATE vs. DEFERRED COMMANDS

A series of commands could be written to perform any of these operations on a sequance of words; S, D, and the operation could be the same in each of the series of commands, with T being increased by 1, in the case of single-precision operation, or by 2, in the case of doubleprecision operation, in each succeeding command. As an example, a straight single-precision transfer of 04.10 to 05.10 would be coded with a "C" code of 0, a source of 04, a destination of 05, and T = 10. This could be followed by another command with the same "C" code, the same source, the same destination, but with T = 11. Then T could be increased by 1 again, and so on. Up to a whole long line could be transferred, one word at a time, in this way. By this method, it would require 108 commands to transfer 108 words. There is a way of accomplishing this with one command: it is to code the command in such a way that its execution will cover any desired number of contiguous word-times. In the layout of a command, as shown on page 61, bit 29 of the command is a one-bit indicator called "I/D". The "I" stands for "immediate". An immediate command is one which will be executed immediately after it is read and interpreted. Its execution will continue until the computer is told to stop the execution. The T number in such a command serves as a "flag", telling the computer when to stop the execution of the command. The execution will be stopped before T, but after the immediately preceding word-time. To indicate immediate execution of a command, bit 29 of the command is set with 0. In the above example, if it was desired to transfer words 10 - 15 from line 04 to line 05, a command with a "C" code of 0, S = 4, D = 5, T = 16, and I/D = 0, could be located at word 09 of some line out of which it would be read. Which line of memory the command would be in is as yet an open question. The command would be read at word-time 09 and executed immediately, meaning that its execution would start in the very next word-time, 10. It would continue operating through 10, 11, 12, 13, 14, and 15. The T number of 16 would serve as a flag, stopping the operation after word-time 15 and before word-time 16.

An important point to note in the discussion of immediate commands is that an immediate command must execute for at least one word-time before the flag can be effective. If, in the previous example, the immediate command located at word 09 had a T of 10, the flag could not

stop the operation until a complete drum cycle had elapsed, and word 10 was coming up for the second time. This, then, would be the way in which one command could cause the transfer of one whole long line to another: let T of the command be 1 greater than the location of the command itself, and let the command be an immediate command calling for the straight transfer of words.

Any of the previously discussed commands, either single- or double-precision, can be made immediate by setting bit 29 of the command equal to 0.

If an immediate command is not desired, or, to put it another way, it is desired that operation be deferred until some particular word-time, and then be performed for that word-time only, bit 29 of the command must be set to 1, indicating deferred (D) operation. Of course a deferred double-precision command will still obey the rules for double-precision operations: namely, the operation will continue until the next sign-time, which will be two word-times later. In other words, making a double-precision command deferred does not alter the fact that two contiguous words will be operated upon; it merely pinpoints the two words. An immediate double-precision command will operate on contiguous two-word numbers until stopped by a flag.

The immediate commands which can be made from each of the operation codes discussed so far are often referred to as "block" operations, since they operate on blocks of numbers.

### SEQUENCING OF COMMANDS

As shown in the layout of a G-15 command on page 61, each command contains in itself the address of the next command (N) to be obeyed, and the word-time portion of this address is in bits 20 - 14. Notice that seven bits are allotted and are sufficient to express any word-time in memory. Commands, like data, may occupy any word. An address consists of more than a specified word-time, however; a line number must also be included. In the case of N, in a command, the line-number is implied to be the same as the number of the line in which the current command is located. In other words, the G-15 will continue looking for commands in the same line, once it has started with a command in that line. Since this is the case, it is only necessary to specify the word-time at which the next command is located in the same line.

### COMMAND LINES

Not all lines in memory are connected to the special circuits which interpret commands. Any line which is so connected is called a "command line", and commands located in it can be read and executed. The command lines are 00, 01, 02, 03, 04, 05, 19, and 23. A command can also be executed out of AR, but this special action by the computer must, in turn, be called for by a special command, which will be discussed later. In order to preserve numerical continuity in all references to command lines, line 19 is referred to as command line 06, and line 23 is referred to as command line 07. AR, because of its special nature

in this regard, is not referred to as a command line. Once a command line has been chosen, the computer will continue to obey commands in that line, but how does a command line get chosen originally? What happens when a program must occupy more than one line? These are logical questions, and we will look into their answers just as soon as we complete the discussion of commands, themselves.

The only bit in a command word which remains unmentioned at this point is bit 21. You may now consider it mentioned, although this would be the wrong time in the discussion to describe its function. For our purposes at present, always assume it contains 0.

So far, although many computer operations have been discussed, they do not include all of the operations we will need for the solution for the quadratic equation. Multiplication and division are just two of the operations not supplied through the normal operation codes. It has been pointed out that, although there is no line 31 in the memory of the G-15, this number may be placed in a command as either the source (line) or the destination (line). If 31 is specified as either S or D in a command, the computer will know that no ordinary transfer is being called for.

#### SPECIAL COMMANDS

Upon discovery of D=31 in a command, the computer will treat this command as a "special" command, and interpret it in a special way. The S number will be treated as a special operation code, and the three bits which normally specify the operation will usually be interpreted in the light of the special operation called for.

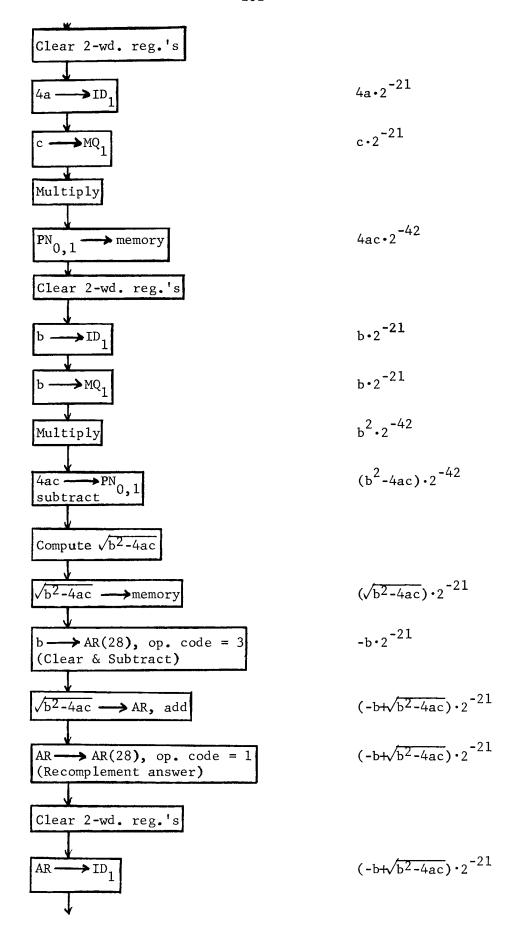

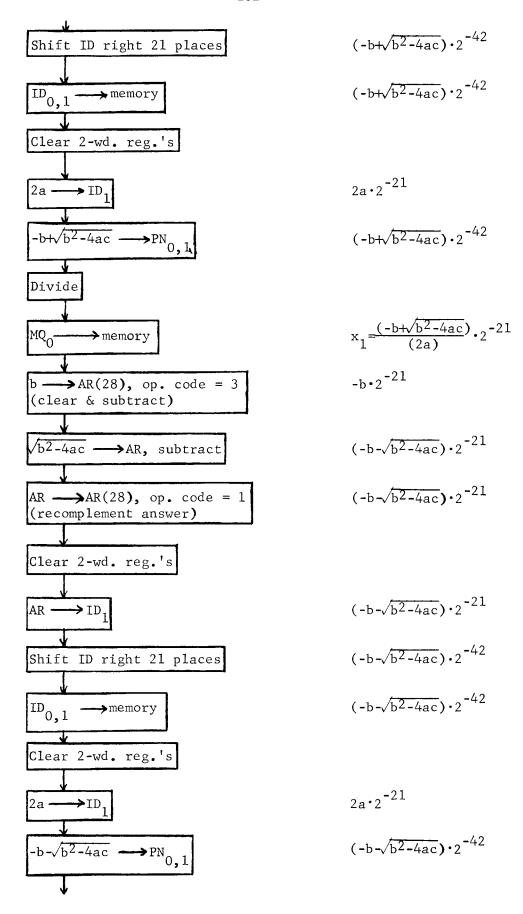

In the example of the quadratic equation, all additions and subtractions can be performed by using normal operations, but the other operations necessary, of which multiplication and division are two, will require special commands.

## MULTIPLICATION AND THE TWO-WORD REGISTERS

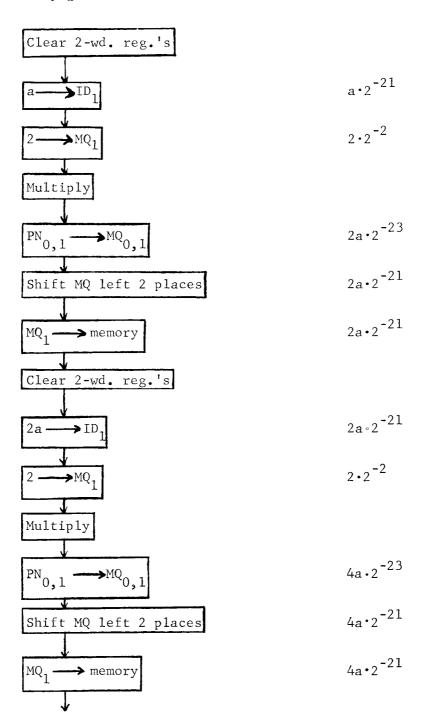

The multiply command contains: D=31, S=24, and "C" code = 0. Before this command is executed, however, the proper numbers to be multiplied together must be in the two-word registers ID and MQ, as mentioned before. Therefore, the multiply command must be preceded by two other commands in the program, which load these two registers. The product, after multiplication, will appear in PN. The programming method for performing a multiplication can be derived from a further study of the two-word registers and how they operate.

Any two-word register can be loaded with either a single-precision number (via a single-precision transfer) or a double-precision number (via a double-precision transfer), but the two-word registers will always word in double-precision when a multiplication is called for. Two 57-bit magnitudes will be multiplied together. If a single-precision multiplication is really desired, it can be achieved by only loading the most significant bits of ID and MQ, making sure that the remaining, least-significant bits are cleared to 0. A 56-bit product (to be expected

when two 28-bit numbers are multiplied together) will appear in PN in double-precision form. If a single-precision product is desired, it will be in the most significant word of PN. So, in the case of a single-precision multiplication, the two-word registers must be cleared to 0 before they are loaded with the multiplier and multiplicand. Of course the product will be the same, regardless of which of the two numbers is treated as the multiplier and which as the multiplicand.

The G-15 is internally wired in such a way that each bit (of the 58 bits) in PN may be cleared as the corresponding bit in ID is set.\* Therefore, if all 58 bits of ID are set, regardless of how they're set, prior to a multiplication, all 58 bits of PN will automatically be cleared, and PN will be ready to receive the product. The setting of MQ will affect no other register, nor will it be affected by the setting of any other register.

In a multiplication, although the magnitudes of the two numbers are to be multiplied, we know that the signs must be added, if the laws of signs are to be obeyed. A product is usually worthless if it contains the wrong sign. The G-15 knows this, too. Therefore, when the two-word registers are being loaded, via a normal operation (transfer),

|   | + | - |   | 0 | 1 |

|---|---|---|---|---|---|

| + | + | - | 0 | 0 | 1 |

| - | - | + | 1 | 1 | 0 |

if the "C" code is even, (0, 2, 4, 6), the sign of the number is divorced from the magnitude and sent to a special "flip-flop" associated with the two-word registers, called IP. A flip-flop is a twostate device, one state equalling 0, the other equalling 1, and it can remember which state it is in. It can also be read, or "sensed", to determine which state it is currently in. The bit in the two-word register which would normally receive the sign will not; it will be set to 0. When ID is loaded, IP will be set with the sign of the number going into ID. When MQ or PN is loaded, the sign of the number being transferred will be added to the present value of IP, and the result will remain in IP. Similarly, when a number is transferred, via a normal operation, out of a two-word register, and the "C" code is even, the magnitude will come from the register specified as S, but the sign will come from IP. This function of IP is automatic. The only special precaution the programmer must take in order to insure its operation is to transfer numbers to and from the two-word registers with even "C" codes. So, in the setting of ID and MQ prior to a multiplication, the program will have to set ID first, then set MQ, thus insuring the correct sign of the product in IP. Then the multiply command may be given.

<sup>\*</sup> Note: this feature is automatic if ID is set with any even C code (0, 2, 4, 6).

When the computer is commanded to multiply, the following will be the state of affairs in the two-word registers:

ID - Multiplicand

MQ - Multiplier

PN - cleared to 0 and ready for product

IP - correct sign (0 or 1) of product

It has been stated that the two-word registers will multiply in double-precision fashion, regardless of whether or not double-precision operation is really desired. Remember that, in double-precision numbers the most significant bits are in the odd-numbered word (in the case of the two-word registers, we refer to these as  $ID_1$ ,  $MQ_1$ , and  $PN_1$ ). All 29 bits are magnitude bits. 28 of the bits in the even-numbered word ( $ID_0$ ,  $MQ_0$ , and  $PN_0$ ) are the least significant bits of the magnitude, and the sign-bit of this word is the sign of the number, or 0, if the sign went to IP.

In the case of double-precision multiplication, then, we would want the initial conditions to be as follows, where x's represent significant bits of magnitude.

|     | Word 1                                  | Word O                                  |

|-----|-----------------------------------------|-----------------------------------------|

| ID: | xxxxxxxxxxxxxxxxxxxxxxx                 | xxxxxxxxxxxxxxxxxxxxxxxxxxxx            |

| MQ: | xxxxxxxxxxxxxxxxxxxxxxxx                | xxxxxxxxxxxxxxxxxxxxxxxxxxxxx           |

| PN: | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

| IP: | 0 or 1, whichever is the corre          | ct sign of the product.                 |

To transfer the double-precision multiplicand from its resting place in memory to  $ID_{0,1}$ , we would use a straight double-precision transfer (C = 4), with D in the command equal to 25 (ID). Because the C code is even, the sign will be disengaged from the magnitude, and sent to IP. Because ID is the destination, IP will be loaded with this sign. Then, to load MQ0.1, we would transfer the double-precision multiplier, also with a C = 4, with D in the command equal to 24 (MQ). Because the C code is even, the sign will be disengaged and sent to IP. Because MQ is the destination, IP will add this sign to its present contents, and the result, which will appear in IP, will be the correct sign of the product. When the signs are disengaged, the bits in the two-word registers which would normally have received them are cleared to 0, as shown above. When ID is loaded (each of the 58 bits is set with some value, replacing what was originally there), each corresponding bit (and therefore, all 58 bits) of PN is cleared to 0. Thus the desired initial conditions will be achieved through the execution of two commands, the first of which loads ID, the second, MQ.

In the case of single-precision multiplication, we would want the initial conditions to be as follows, where x's represent significant bits of magnitude.

Word 1 Word 0

IP: 0 or 1, whichever is the correct sign of the product.

To transfer the single-precision multiplicand from its resting place in memory to ID1 (the most significant half of the two-word register), we would use a straight single-precision transfer (C = 0), with D in the command equal to 25 (ID). Because the C code is even, the sign will be disengaged from the magnitude, and sent to IP. Because ID is the destination, IP will be loaded with this sign. Then, to load MQ1, (again, the most significant half of the two-word register), we would transfer the single-precision multiplier, also with a C = 0, with D in the command equal to 24 (MQ). Because the C code is even, the sign will be disengaged and sent to IP. Because MQ is the destination, IP will add this sign to its present contents, and the result, which will appear in IP, will be the correct sign of the product. When the signs are disengaged, the bits in the two-word registers which would normally have received them are cleared to 0, as shown above. These are bit 1 in both ID1 and MQ1 (remember, this is a single-precision transfer from an odd-numbered location in memory, thus congruent to 1 mod 2, to word Ol in ID and MQ). When ID is loaded (the first 29 bits are set with some value replacing what was originally there), each corresponding bit (and therefore, the 29 bits of PN<sub>1</sub>) of PN is cleared to 0. desired initial conditions will not be totally achieved unless something further is done to clear the remaining bits of ID, MQ, and PN. do no good to follow the two commands which load ID1 and MQ1 with two more which load IDO and MQO, because this will cause the resetting of IP, and destroy the sign of the product. But the two-word registers could be cleared first, and then ID1 and MQ1 set with the desired num-This is the procedure to be followed, and there is a special command which clears all bits in the two-word registers and also clears IP to 0. Since it is a special command, it has D = 31. Since it is going to operate on two-word registers, it must operate for two wordtimes. Its source (S) = 23. The C code = 0. Since the C code = 0, it will operate for only one word-time, unless it is made immediate by setting the I/D bit in the command = 0. The T number in this command, as in any other immediate command, then becomes a flag, telling the computer when to stop execution of the command. Remember that an immediate command will be executed starting in the word-time after that in which the command was read, and it will continue to be executed during each succeding word-time up through the one immediately preceding the flag. It will not be executed during the word-time whose number equals the flag. If we refer to the location of a command as L, then, in the case of the

command which clears the two-word registers, T = L + 3. In order to simplify the writing of flags for T numbers, we drop the plus sign, and use the desired number to be added to L as a subscript for L. In the case of the command we are presently considering, then, T =  $L_3$ .

Three commands, then, are necessary to establish the desired initial conditions for what we might call a single-precision multiply, although that really is a misnomer. The first will clear the two-word registers and IP, the second will load  $ID_1$ , and the third will load  $MQ_1$ .

The special circuitry associated with the two-word registers does essentially two things. We have already seen that it enables PN to act as an accumulator. The other feature accomplished through this special circuitry is a "shifting" process. A shift is the movement of bits toward the high-order or the low-order position within a register. In the G-15 it is accomplished one bit-position at a time. ID shifts toward the low-order (T1) position (this is usually referred to as shifting to the right). MQ shifts toward the high-order (T29) position (this is usually referred to as shifting to the left).

Multiplication involves both the shifting and the additive features of the two-word registers, in the following way. The contents of ID are shifted right by one bit-position, moving all 57 magnitude bits to the right one place. The right-most bit (T2 of ID0) is lost. The left-most bit-position (T29 of ID1) is filled-in with a 0. Simultaneously MQ is shifted left by one bit-position, moving all bits to the left one place. The left-most bit enters an inspection station, where it is inspected for 1 (it will, of course, be either 1 or 0). The right-most bit-position is filled-in with a 0. After such a simultaneous shift, during a single-precision multiplication, ID and MQ would contain:

| Word 1 | Word O |

|--------|--------|

|        |        |

Compare these with the initial conditions shown on page 73.

If the bit from MQ which is inspected is a 1, the new contents of ID are added to PN; if it is a 0, the addition is not performed. The first addition in PN will, of course, be to 0, since PN was initially cleared. This process requires two word-times; because it is essentially a double-precision process, it must begin with an even word-time. It can be repeated as often as desired (28 times for a full single-precision multiplication). The multiply command must be immediate, and it will perform the process over and over again, for the indicated number of word-times. T in the command is a "relative timing number". It will be set equal to the desired number of word-times of execution of the command; this should be an even number, and the execution should begin at an even word-time, requiring the immediate multiply command to be located at an odd word-time. If the

process is allowed to continue for 28 times (T = 56), two full single-precision words can be multiplied together, and their product, a series of sums, will appear in PN. Notice that at least one shift is performed prior to the first addition, and the product will actually occupy the 56 most significant bit-positions in PN. In any number system, if two 28-digit numbers are multiplied together, a 56-digit product, counting any leading 0's, will result. If the initial shift in the computer were not performed, it would be possible, in the case of large numbers, to generate an overflow and an erroneous result.

After a single-precision multiplication, the most significant bits of the answer will appear in  $PN_1,$  bits 29 - 2. Bit 1 of  $PN_1$  and bits 29 - 3 of  $PN_0$  will contain the least significant bits of the product. Assuming that a single-precision product is all that is required, the least significant bits are merely excess accuracy, and can usually be ignored.

In ordinary pencil-and-paper multiplication, if you were to multiply two 28-bit numbers, you would inspect the multiplier from right to

left, one bit at a time. If you found a l, you would add the multiplicand to what you already had in the way of a partial sum. If you found a 0, you would not add the multiplicand. You would then shift the multiplicand to the left one place, and inspect the next bit in the multiplier. You would do this 28 times, once for each bit in the multiplier, and you would generate, as a result, a sum, which represents a product of the two original numbers. The computer does the same thing, in reverse. It starts with the high-order end of the multiplier and inspects toward the low-order end. The shifts are exactly the reverse, therefore; you shifted to the left, but the computer shifts to the right. A double-precision multiply command causes exactly the same sequence of events, but the relative timing number (T) in the command is set to allow the process to continue for 57 times (T = 114). Notice that the multiply command may be allowed to operate for any number of times, merely by setting T = 2k, where k = the number of times desired. The resultant product will always be predictable.

# DIVISION AND THE TWO-WORD REGISTERS

Division is somewhat similar to multiplication, in that it also utilizes the shifting and additive features of the two-word registers in order to reach a result.

The divide command contains: D=31, S=25, and C=1 or 5 (these are interchangeable: the setting of the S/D in the command has no bearing on the operation). As in the case of multiplication, the numbers to be divided must be set up in the two-word registers. The rules governing the initial set-up of the two-word registers apply here as well as in the case of multiply, except that the denominator will be loaded into ID, the numerator into PN, and the quotient will appear in MQ. Because PN is cleared as ID is set, the denominator must be loaded first, then the numerator. In order to clear MQ, preparatory to receiving the quotient, the clear command will have to be given. The proper sign of the quotient will be generated in the same manner as it is for a product.

When the computer is commanded to divide, the following will be the state of affairs in the two-word registers:

ID - Denominator

PN - Numerator

MQ - cleared to 0 and ready for quotient

IP - correct sign (0 or 1) of quotient

In division, as in multiplication, the two-word registers will operate in double-precision fashion. The most significant word is the odd-numbered word (ID1, PN1, and MQ1). If single-precision division is required, the single-precision denominator usually will be in ID1,\* bits 29 - 2 (remember its sign will be in IP), followed by insignificant 0's in bit 1 of ID1 and all 29 bits of ID0. Wherever the denominator is in ID\*, the single-precision numerator should be similarly positioned in PN.

In the case of single-precision division, usually we want the initial conditions to be as follows \*, where x's represent significant bits of magnitude.

|     | Word 1                                  | Word 0                                  |

|-----|-----------------------------------------|-----------------------------------------|

| ID: | xxxxxxxxxxxxxxxxxxxxxxxxxxxxx           | 000000000000000000000000000000000000000 |

| PN: | xxxxxxxxxxxxxxxxxxxxxxxxxxxx            | 000000000000000000000000000000000000000 |

| MQ: | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

| TP: | 0 or 1. whichever is the corre          | ct sign of the quotient.                |

\* The reason for making this indefinite statement will follow a description of the machine's divide process.

In order to get MQ cleared, the first command in the set-up for a division would be the clear command. This would be followed by two straight single-precision transfers from memory to  ${\rm ID}_1$  and  ${\rm PN}_1$ , in that order. The signs of these two numbers will be disengaged and sent to IP, where the proper resultant sign will be generated. O's will occur in the bits in ID (bit 1 of  ${\rm ID}_1$ ) and PN (bit 1 of  ${\rm PN}_1$ ) which would normally have received the signs.

When the desired initial conditions have been established, the divide command may be given. In order to understand the computer's division process, we must first inspect the pencil-and-paper method, to determine what process is involved there; we're so used to doing it, that we usually don't consciously analyze the process as we do it, but there is an underlying, reasonable pattern to the process of "long division". Consider the following long division in binary arithmetic.

| 0101000             |

|---------------------|

| 101000/011001000000 |

| 000000              |

| 0110010             |

| _101000             |

| 0010100             |

| _000000             |

| 101000              |

| 101000              |

| 0000000             |

| _000000             |

| 0000000             |

| _000000             |

| 0000000             |

| 000000              |

| 000000              |

In division we are attempting to find the ratio of one number to another. We call one of these numbers the denominator, and the other, the numerator. The resultant ratio, which we call a quotient, is the ratio of the

numerator to the denominator: N/D. The first step is to subtract the denominator, in its present form  $(D \cdot 2^{O})$ , from the numerator. We find that this yields a negative result. (In the decimal system we would inspect each possible multiple of D, starting with 9·D, but, in the binary system, the only possible multiples of D are  $1 \cdot D$  and  $0 \cdot D$ ). We therefore discard the coefficient of 1, and

say that N contains 0·D plus a remainder, R1. We now shift D to the right one place (in the binary system, this yields D·2<sup>-1</sup>), and attempt to subtract it from this remainder. This remainder, of course, equals N, since N - 0 = R1. In effect, what we are doing, knowing that N does not contain D, is attempting to discover whether or not N contains D/2.

It does, and we know that because we get a positive result after the subtraction.  $R_1$  contains  $1 \cdot D \cdot 2^{-1}$  plus a remainder,  $R_2$ . We continue this shifting and subtracting process until we arrive at a remainder of 0 or until we achieve the desired accuracy in the resultant quotient.

$$N = 0 \cdot D \cdot 2^{0} + R_{1}$$

$$N = 0 \cdot D \cdot 2^{0} + 1 \cdot D \cdot 2^{-1} + R_{2}$$

$$N = 0 \cdot D \cdot 2^{0} + 1 \cdot D \cdot 2^{-1} + 0 \cdot D \cdot 2^{-2} + R_{3}$$

$$N = 0 \cdot D \cdot 2^{0} + 1 \cdot D \cdot 2^{-1} + 0 \cdot D \cdot 2^{-2} + 1 \cdot D \cdot 2^{-3}$$

The reason we have taken a close look at the way you divide is that, contrary to popular belief, the designers of digital computers are "just plain folks"; they think the way you do, and when they were faced with the problem of designing a division operation for the Bendix G-15, they followed the same reasoning we have followed here. They noted one important exception to it, however, from the standpoint of the computer: the computer cannot "inspect" prior to a subtraction; it must subtract, and then inspect the result. the numerator is in PN, and since the subtraction will also be performed in PN, it is obvious that, after the subtraction, the original numerator will be lost in any event, and either a positive or a negative remainder will be in PN. The computer will have to be able to determine its future course on the basis of the sign of the remainder in PN. The bit that goes in the quotient is easily determined: if the sign of the remainder is negative, a 0 goes in the quotient; if the sign of the remainder is positive, a 1 goes in the quotient. If the remainder is positive, there is no problem: the denominator must be shifted right one more place and a new trial subtraction performed. But, in the case of a negative remainder, the problem is a bit more difficult. We know that the division yielded a 0 at this point, and the remainder actually indicates the quantity by which the denominator exceeded the numerator (or previous remainder, if this is not the first subtraction). If we shift the denominator right one more time, obtaining 1/2 its previous value, and add this to the negative remainder, we will know whether or not an original subtraction of D/2, rather than D, from N would have yielded a positive result. (N - D + D/2 = N - D/2). In short, we can devise the following rule: subtract D from N; if the result ( $R_1$ ) is positive, place a 1 in the quotient, and subtract D/2 from  $R_1$ , continuing the process. If the result is negative, place a 0 in the quotient, and add  $\mathrm{D}/2$  to R1, continuing the process.

The designers worried about one other point: the necessity for carrying many insignificant trailing 0's along with N, in order to perform the long division process. They realized that, after subtracting D from N, and arriving at a remainder  $R_1$ , the ratio of  $R_1$  to D/2 is the same as the ratio of  $2 \cdot R_1$  to  $D/2 \cdot R_1 \cdot D/2 \cdot R_1 \cdot D/2 \cdot R_1 \cdot D/2 \cdot R_1 \cdot D/2$ . Therefore, rather than shift D right to obtain D/2, they decided to shift  $R_1$  left to obtain  $2 \cdot R_1$ , and do this successively, with each remainder, always adding (in the case of a negative R) or subtracting D (in the case of a positive R) from the new value. Although it seems that overflow

might be caused by shifting a remainder to the left (if the remainder has a l in the most significant bit position prior to the shift), this will not cause overflow, because of the manner in which the numbers are treated by the circuitry employed during a divide operation. Any temporary overflow condition will right itself in the next step of the continuing process. Such a temporary overflow will not set the overflow indicator. The algorithm upon which this division process is based is that N will never equal or be greater than 2·D. The long division in binary, as shown on page 77, will look like the following, as it is performed by the computer.

0101000  $101000 \sqrt{011001}$  N sub 101000 D 0) - 001111 R<sub>1</sub> - 011110 2·R1 add 101000 D 001010 R<sub>2</sub> 010100 2 · R<sub>2</sub> sub 101000 D 0) - 010100 R<sub>3</sub> - 101000 2·R3 add 101000 D 000000 R4 000000 2 · R4 sub <u>101000</u> D 0) - 101000 R5 -1010000 2·R5 add 101000 D 0) - 101000 R6 -1010000 2 · R6

Notice that the overflow caused by  $2 \cdot R_5$  is corrected by the next addition. This is a temporary overflow.

At the beginning of the division process, MQ is shifted left one bit-position, while D is subtracted from N. MQ, then, if it were not cleared prior to the division, would look like this, where Y's represent the original contents of MQ.

Word 1 Word 0

####

In the case of division, although MQ shifts left, ID does not shift right, so  $D \cdot 2^0$  remains in ID.  $R_1$  is inspected: if it is positive, a 1 is placed in T2 of MQ0; if it is negative, a 0 is placed in the same bit. PN, containing  $R_1$ , is shifted left one bit-position, so that it now contains  $2 \cdot R_1$ . The sign of  $R_1$  is used to control the inverting gates during the next transfer of D to PN for addition or subtraction. (Notice that D will pass through the inverting gates because the C code of the divide command contains a 1.) If the sign of  $R_1$  is positive, it will be reversed and combined with D from ID on the next pass, so that, as D passes through the inverting gates on its way to PN, the effect will

be to subtract D from  $2 \cdot R_1$ . If the sign of  $R_1$  is negative, it will be reversed, combined with D from ID, and cause the addition of D to  $2 \cdot R_1$ . A complete step such as the one described above will require two wordtimes, since division is essentially a double-precision operation, even though single-precision numbers may actually be involved. The next step in the process will begin with the shifting of MQ left by one bit-position again, so that the first bit in the quotient will occupy T3 of MQ0, and T2 will be ready to receive the next bit. During the second step,  $2 \cdot R_1$  will be in PN, and D will be added to, or subtracted from it. This process will continue for as many word-times of execution as are allowed by the divide command. The command will be immediate, and the relative timing number in T will be set to allow 57 word-times of execution (T = 57) for a single-precision divide.

After 56 word-times of execution, at 2 per step in the division process, 28 bits of quotient will be generated in MQ0, and MQ will look like this, where Y's represent original bits, and x's represent quotient bits.

| Word 1 | Word 0 |

|--------|--------|

|        |        |

#

If only 56 word-times of execution are allotted, the first x in the drawing above (in T29 of MQ<sub>0</sub>) will represent  $x \cdot D \cdot 2^0$ , while the remaining bits in MQ<sub>0</sub> will represent a fractional quotient. If a 57th word-time of execution is called for, during that word-time MQ<sub>0</sub> will be shifted left one bit-position, and a new bit will be placed in T2 of MQ<sub>0</sub>, so that MQ will look like this.

| Word 1 | Word O |

|--------|--------|

|        |        |

#

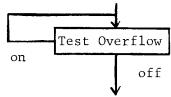

Notice that MQ<sub>1</sub> did not move, while MQ<sub>0</sub> did. The first bit in MQ<sub>0</sub>  $(x \cdot D \cdot 2^0)$  is shifted into a flip-flop which detects overflow. The bit now in T29 of MQ<sub>0</sub> represents  $x \cdot D \cdot 2^{-1}$ , and the whole word is a fractional quotient. This is the normal form for a ratio, and it is the form most desirable when programming the G-15. Overflow will be indicated if the quotient actually equals or exceeds 1, since, in that case, a 1 will reach the overflow flip-flop during this last shift. If T = 56 in the divide command, the overflow indicator may be erroneously set, and should never be depended upon.

The rule, then, for a single-precision division is:

- 1. Never divide an N which is greater than, or equal to D.

- 2. Use a T = 57 in the divide command.

- 3. As in the case of multiply, the divide command must be located at an odd word-time.

You can see that there are exceptions to this rule, but that a thorough knowledge of computer logic and much experience are required. In no case will division work if N is greater than or equal to 2.D.

Double-precision division involves exactly the same operations as does its single-precision counterpart. Of course, the execution time of the command must be greater. With 57 bits of quotient to be generated, 114 word-times would be necessary. If this is the time allotted, the first bit of the quotient (T29 of MQ1) will represent  $x \cdot D \cdot 2^0$ . In the case of double-precision, two more word-times are necessary to shift the entire quotient one bit-position to the left. If T = 116, all 57 bits of the quotient will be fractional, T29 of MQ1 representing  $x \cdot D \cdot 2^{-1}$ , and T2 of MQ0 representing  $x \cdot D \cdot 2^{-57}$ . In this case, the overflow flip-flop will be set with  $x \cdot D \cdot 2^0$ . If the quotient equals or exceeds 1, x will equal 1, and overflow will be indicated. If T = 114, erroneous overflow may be indicated.

The rule, then, for double-precision division is:

- 1. Never divide an N which is greater than, or equal to D.

- 2. Use a T = 116 (v6) in the divide command.

Again, exceptions are possible, but thorough knowledge of computer logic and much experience are required. In no case will division work if N is greater than or equal to  $2 \cdot D$ .

Remember that a quotient is nothing more than a ratio of one number to another. It stands to reason that, if 2/17 = 4/34, etc.,

bу

###

So long as the denominator and the numerator occupy corresponding bit-positions in ID and PN, respectively, which bit-positions they occupy will have no effect on the quotient. For each denominator and numerator, regardless of their positions in these two registers, provided the above requirement is met, there will be one correct quotient appear in  $MQ_0$  for single-precision division, and one correct double-precision quotient, if that is called for, in all of MQ.

It would be desirable to round off a quotient to the nearest figure in the last digit carried, but this is not possible, because there is no way of examining the remainder in the G-15. Truncating the quotient, i.e., ignoring the value of digits beyond the one carried, will result in the quotient reported being somewhere between correct and one unit low, and averaging a half unit low. This would give a systematic error which could seriously affect accuracy after a large number of operations. One way of avoiding this is to add an average of one half to all quotients. This is simply done by making the last bit always 1, i.e., adding one unit to half of the uotients: those originally ending in zero. This is called the "Princeton Round-off". A truncated quotient is between zero and one unit low, while a Princeton-rounded quotient is between one unit low and one unit high.

There is no way to program the elimination of the Princeton round-off; it will always occur. If you desire a single-precision quotient without this round-off, you can carry the division out as a double-precision operation, making T=116 (v6) in the divide command, in which case the single-precision quotient will be in bits 29-2 of MQ1, and the rest of the bits in MQ will contain the remainder. The Princeton round-off will occur at T2 of MQ0.

Notice that, in either single-precision multiplication or single-precision division, four commands are necessary to set up for, and perform, the operation. One command clears the two-word registers, two others load each of the two-word registers containing the numbers to be operated on, and the fourth command actually calls for the desired operation. The clear command can sometimes be eliminated by utilizing special circuitry connecting AR and the two-word registers.

In the table of normal operations (pages 64 - 66), it was pointed out that, if both S and D are less than 28, codes 2 and 6 call for exchanges of AR with memory. So do codes 3 and 7, under similar circumstances, except that, in these two cases, complementation of negative numbers is involved. If any one of these four commands is used to load ID (25), MQ (24), or PN (26) from some other location in memory (S less than 28), during all even word-times AR cannot load any of these three registers.

In other words, the contents of AR will be blocked off from IDo, MQo, and PNO. In the place of the contents of AR, the even half (word 00) of the specified two-word register will receive 29 0's. If the C code = 6, during the following odd word-time, the contents of AR will be transferred to the odd half of the specified two-word register. Because the C code is even, the sign of the double-precision number will go to IP, according to the rules discussed earlier. Notice that during the even word-time of execution, the original contents of AR attempt to reach the even half of the specified two-word register, but are blocked off, and 0's are transferred instead. During the same word-time, the even-numbered word from memory goes to AR. During the following odd-numbered word-time, the contents of AR (originally an even-numbered word from memory) goes to the odd half of the specified two-word register. The fact that this word was delayed one word-time because of its transfer via AR does not alter the fact that it is the first word of a double-precision number. Therefore, even though it reaches the two-word register at an odd word-time, its sign will be divorced, and sent to IP, in accordance with the rules already mentioned.

Consider, then, a single-precision multiplication: A·B, where A is stored in an even-numbered word. If a transfer of A to ID via the AR register is called for (C = 6), during the first word-time (an even numbered word-time), the original contents of AR attempts to reach IDO, but is blocked off, and all 29 bits of IDo are cleared to 0. During the same time, A is transferred to AR. During the next word-time (an odd word-time), A is transferred from AR to ID1, but, since A is the first half of what the computer believes to be a legitimate doubleprecision number, its sign, being treated as the sign of the number, is disengaged from the magnitude bits, and it is transferred to IP. Tl of  ${\rm ID}_1$ , which normally would have received this sign, is cleared to 0. Since every bit in ID has been set during this operation, every bit of PN has been cleared. The only initial condition remaining to be satisfied is the placing of the multiplier, B, in MQ1. If B is in an odd word in memory, a straight single-precision transfer to MQ1 will accomplish this. Since the C code for this is 0 (therefore, it is even), the sign will be disengaged from the magnitude portion of B, and it will be sent to IP, to be combined with IP's present contents. Notice that the initial conditions in this case will be:

|     | Word 1                                  | Word 0                                  |

|-----|-----------------------------------------|-----------------------------------------|

| ID: | ************                            | 000000000000000000000000000000000000000 |

| MQ: | *************************************** | YYYYYYYYYYYYYYYYYYYYYYYYY               |

| PN: | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |

| IP: | 0 or 1, whichever is the corre          | ct sign of the product.                 |

In the above layout of the two-word registers, the Y's in MQ $_0$  represent the original contents of that word, remaining after MQ $_1$  has been set. Since, during a multiplication, MQ is shifted to the left one bit-position

at a time, each succeeding bit being inspected to determine whether or not the contents of ID should be added to the contents of PN, and since, if a single-precision multiplication has been called for, only 28 bits from MQ will be inspected, the remaining "garbage" in MQ will have no effect on the multiplication. There is no need to clear MQ0 prior to a single-precision multiplication. However, if the multiplier were in an even-numbered word in memory, it would be perfectly permissable to use a transfer via AR (C = 6) to get it into the odd half of MQ. In this case, of course, MQ0 would be cleared.

In the case of a single-precision division (N/D), if D is stored in an even word in memory, and transferred into ID1 via AR, this will succeed in properly preparing ID for the division and setting up IP for the addition of signs. But setting ID clears PN, and not MQ. PN could be set with the proper value (N), either by a straight single-precision transfer, or by a transfer via the accumulator, and, in either case, it would also be set up properly. If PN1 were set by a straight single-precision transfer (C = 0), PN0 would still have been cleared because each bit in ID0 was set (to 0). MQ will remain unaffected, containing its original contents.

|     | Word 1                        | Word 0                                  |

|-----|-------------------------------|-----------------------------------------|

| ID: | xxxxxxxxxxxxxxxxxxxxxxxxxxxx  | 000000000000000000000000000000000000000 |

| PN: | xxxxxxxxxxxxxxxxxxxxxxxxxxxxx | 000000000000000000000000000000000000000 |

| MQ: | YYYYYYYYYYYYYYYYYYYYYYYYYYY   | YYYYYYYYYYYYYYYYYYYYYYYYY               |

|     |                               |                                         |

IP: 0 or 1, whichever is the proper sign of the quotient.

The Y's in the above layout of MQ represent its original contents, remaining after both ID and PN have been set. This is perfectly all right, however, since MQ is shifted to the left one bit-position at a time, as each bit of the quotient is placed in T2 of MQ0. Tl of MQ0 is cleared by the initial shift, preparatory to the placement of the first quotient bit in MQ0. If a full 28-bit quotient is generated, all the Y's shown above in MQ0 will be shifted out to the left, and all 28 magnitude bits of that word will contain quotient bits.

#### REVIEW

At this point, we pause to review what has been covered. We first pointed out that, in order to effectively use the computer, the programmer must analyse the problem:

- determine the formula(s) by which a solution can be reached, or in some way define exactly what is called for;

- 2. discover the form, magnitude, and ranges in values, of the data which will be available as input for the program;

- 3. choose an appropriate method of solution;

- 4. outline, very briefly, the logical path to be followed in this method, such an outline being called a flow diagram.

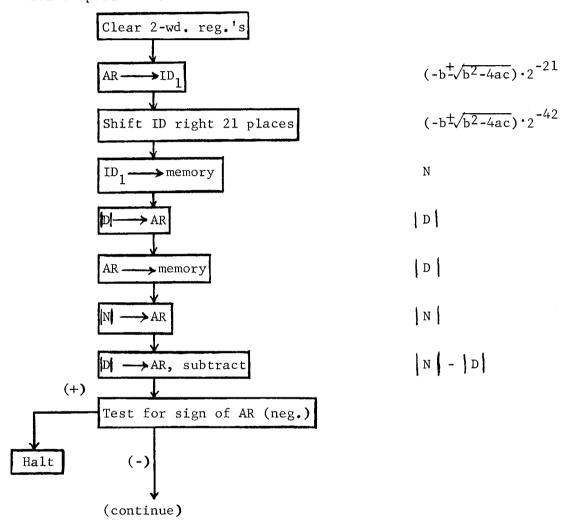

We then analysed a sample problem, that of solving for the roots of a quadratic equation of the form,  $a \cdot x^2 + b \cdot x + c$ . After we developed a flow diagram for its solution, we saw that we needed more thorough knowledge of available computer operations, especially the arithmetic operations.

This lead us to a discussion of commands as they appear, in binary, in the computer. The first part of a command we studied was the C code, consisting of a two-bit characteristic and a one-bit indicator for either single- or double-precision operation. We saw that the various possible C codes in three bits run the gamut of 0 - 7, where 4, 5, 6, and 7 are essentially the double-precision counterparts of the single-precision codes 0, 1, 2, and 3, respectively.

Each of these operations is a transfer of some type, and it may call for the use of special circuitry during the transfer, such as inverting gates, or circuitry which can change a sign, drop a sign, or add. The various types of transfers that were seen to be available were:

- 1. straight single- or double-precision transfer from one place in memory, including either the single- or double-precision accumulator, to another, also including the accumulators; C = 0, 4;

- 2. single- or double-precision transfer via the inverting gates (to accomplish complementation of negative numbers, preparatory for addition) from one place in memory, including either of the accumulators, to another, also including either of the accumulators; C = 1, 5;

- 3. exchange of memory with AR, both single-precision words, and the transfer in each direction, a straight single-precision transfer; C = 2;

- 4. transfer of a double-precision number via AR, in which, during the even word-time, the even word of the double-precision operand goes to AR while the original contents of AR go to the even word of the double-precision destination; during the odd word-time, the new contents of AR go to the odd word of the destination, while the odd word of the operand goes to AR; C = 6;

- 5. transfer either a single- or a double-precision magnitude to or from the appropriate accumulator, the sign being dropped during the transfer; C = 2, 6;

- 6. exchange memory with AR, both single-precision words, the transfer from AR to memory being a straight single-precision

transfer, but the transfer from memory to AR being via the inverting gates; C = 3;

- 7. transfer of a double-precision number via AR, as in (4), above, except that each word of the double-precision operand as it enters AR, enters via the inverting gates; C = 7;

- 8. transfer either a single- or a double-precision number to or from the appropriate accumulator, but with a change of sign, and subsequent passage through the inverting gates, for complementation, if necessary, preparatory to addition (changing the sign of a number and adding it accomplishes the same end result as subtracting it); C = 3, 7.

After discussing the normal operations (each one actually a different type of transfer of words available in the G-15), we examined the various addresses contained in a command.

One of these is the address of the operand, the word(s) to be transferred. All addresses in the memory of the computer are composed of a line number and a word number, or word-time, within that line. An address is denoted in the following manner, where LL stands for line number, and TT, for word-time: LL.TT. The line containing the number to be transferred is called the Source, and the address of the operand is SS.TT, usually written S.T. The address of the word(s) receiving the number to be transferred is also composed of a line number and a word-time, and is written D.T, where D stands for Destination. In a command, the word-time (T) involved in both these addresses is the same, and is given only once. Therefore, a transfer of a word(s) from one line to another will place the number being transferred in the Destination at the same word-time it occupies in the Source, or (in the case of transfers between lines of different lengths) in a word-time congruent to the word-time it occupies in the Source.

The functions of S and D were described. They control selectors which, in turn, modify the normal recirculation of memory at the proper word-time in the proper line.

We then discovered that a series of individual commands, each with the same S, D, and C, but with successively increasing T's, can be replaced by one immediate command, in which the T number is a flag, telling the computer when to stop the operation. In such a case, the operation commences in the very next word-time after the command has been read, so the location of an immediate command helps to determine how many, and which words will be transferred. We called these immediate commands "block" commands, since they work on blocks of congruent words in given lines.

If it is not desired that a command be immediate, it can be made deferred, in which case it will operate only on the word (or two words, in the case of double-precision) indicated by the T number. A bit indicating whether the command is immediate or deferred is included in the command, itself. It is the I/D bit, (T29).

It was pointed out that, when we say a G-15 command contains within itself the address of the next command to be obeyed, and thus the program sequence is determined by the programmer when he makes up the individual commands in his program, we are only partly correct. Each command contains the word-time at which the next command is to be read, but the line number in which that next command is located is not contained within the current command. The reason it is not, is that, once a sequence of commands is started in any "command" line, the line will remain the same, and thus, need not be specified from command to command. Only word-times need be specified. It was also pointed out that not all lines in the memory of the G-15 are "command" lines. Commands can only be read out of lines 00, 01, 02, 03, 04, 05, 19, and 23. These are called "command" lines 0, 1, 2, 3, 4, 5, 6, and 7, respectively.

Two points remained open, although they were discussed:

- 1. how a command line is initially chosen, and how a program can switch from one line to another, should that be necessary; and

- 2. the meaning of the BP bit in a G-15 command, this being the only bit not defined.

After the discussion of the various parts of a command, the concept of special commands was introduced. It was pointed out that not all of the operations necessary for the solution of the quadratic equation were, as yet, described. The two most apparent of these omitted operations were multiply and divide.

If D is set equal to 31 in a command, since there is no line referred to by that number, the G-15 treats this command as a special command. In this case, the S number in the command will become a special operation code, and the C code will usually be treated in the light of the special operation called for. Having thus defined special commands, we proceeded to discuss two of them, multiplication and division.

We saw that the command calling for a multiplication contains D=31, S=24, C=0, and T=a relative timing number, which indicates for how many word-times the execution of the command is to be carried out, where two word-times are necessary for each bit in the product. The duration of operation of this command can be of any length, provided T is a multiple of 2, and, in any case, the results will be predictable. This command must be an immediate command, and, because its operation is always double-precision in nature, it must be located at an odd word-time, so that the first word-time of execution will be an even word-time.

We also saw that it is necessary to place the multiplicand and the multiplier in the two-word registers, ID and MQ, respectively, prior to giving the multiply command. Certain clearing of the two-word registers is also necessary. The rules for setting up these registers, and how they operate during the multiplication were discussed, but suffice it to say here that the product will appear in PN: if a full single-

precision multiplication is called for (T = 56), the product will be in  $PN_1$ ; if a full double-precision multiplication is called for (T = 114), the product will be in  $PN_0$ ,1. In any case, the correct sign of the product will be generated in IP. In this regard, we saw that, if a number, either single- or double-precision, is transferred to any two-word register with an even C code (0 is treated as even), the sign will be divorced from the magnitude, the sign going to IP, and the magnitude going to the magnitude bits of the appropriate word(s) in the appropriate two-word register. Similarly, when a number is transferred out of any two-word register, if the C code is even, the magnitude bits of the number will be picked up from the register itself, while the accompanying sign will be picked up from IP. Although this makes ordinary use of the two-word registers for storage slightly confusing, it is necessary for proper operation during multiplication and division.

After multiplication, we discussed division, and saw that it, too, utilizes the two-word registers and IP. The divide command contains D=31, S=25, C=1 or 5 (the operation will be exactly the same, regardless of which is used), and T=a relative timing number. For a single-precision divide, T must equal 57; for a double-precision divide, T must equal 116. Exceptions to this rule are possible but require thorough knowledge of the internal logic involved and extreme care in treatment of the quotient. This command must be immediate, and, because its operation is always double-precision in nature, it must be located at an odd word-time, so that the first word-time of execution will be an even word-time.

The denominator and the numerator are placed in ID and PN, respectively, prior to giving the divide command. Certain clearing of the two-word registers is also necessary. The quotient will appear in MQ; a single-precision quotient will appear in MQ0; a double-precision quotient will appear in MQ0,1. The correct sign of the quotient will be generated in IP. The least significant bit in a quotient will always be 1; this is called the Princeton round-off.

A quotient represents the ratio of one number to another. In the G-15, this ratio should be in the form of a proper fraction, less than 1. If a quotient less than 1 is to be obtained, care must be taken to insure that, prior to the division, the numerator, as it appears in the machine, is less than the denominator, as it appears in the machine. Since a ratio is desired in a division, the location of the numbers to be divided, in ID and PN, is immaterial, provided they occupy corresponding bit-positions in those two registers.

Because of a unique circuit connecting AR and the two-word registers, use of a C code equal to 6 in the transfer of a single-precision number from an even location in memory (S less than 28), via AR, and into the odd half of ID ( $\mathrm{ID}_1$ ), will accomplish all the clearing necessary for a single-precision multiplication or division, eliminating the necessity for a clear command. This same circuit will cause the same clearing to occur whenever S is less than 28, D equals 24, 25, or 26, and the C code equals 2, 3, 6, or 7.

## MACHINE FORM OF A NUMBER AND SCALING

Several times reference has been made to the machine form of a number, and, in the Introduction to the G-15, it was implied that the following numbers in machine form are equal to the decimal numbers shown below:

| Binary number in machine                | Decimal equivalent |

|-----------------------------------------|--------------------|

| 000000000000000000000000000000000000000 | 1.                 |

| 000000000000000000000000000000000000000 | 2.                 |

| 00000000000000000000000000110           | 3.                 |

| 000000000000000000000000011             | -3.                |

This implies that the binary point in a machine number is usually between the least significant magnitude bit and the sign bit.

$$000000000000000000000000001.+(2) = +1.(10)$$

This would mean that usually a machine number is entirely integral, and has no fractional bits. But if this were the case, the result of a multiplication or of a division is most disconcerting, for a multiplication will result in a product smaller than either the multiplicand or the multiplier, and a division will result in a quotient larger than the numerator, and, in some cases, also larger than the denominator. These statements are verified by the fact that multiplication of even the very largest possible numbers cannot cause overflow, and division of a number by another can cause overflow.

In short, it would seem, from inspection of these results, that numbers in the computer are actually fractional rather than integral. If two fractions are multiplied together, the resultant product will be smaller than either of the original numbers, and if a fraction is divided by another fraction, the result will in all cases exceed the value of the numerator, and may exceed the value of the denominator.

Actually, the computer treats every binary number in its memory as a 28-bit fraction with a sign. The binary point in the machine, sometimes referred to as the machine-point, precedes the most significant bit of a number. If this is the case, then:

We can interpret any 28-bit binary value in the machine in any way we want; that is to say, we can understand the true binary point for our purposes to follow T2 if the machine holds  $1/2^{28}$ th of what we intended. The maximum value we can express in 28 bits is:

which equals

$$1 \cdot 2^{0} + 1 \cdot 2^{1} + 1 \cdot 2^{2} + \dots + 1 \cdot 2^{26} + 1 \cdot 2^{27}$$

,

and this is 1 less than  $1.2^{28}$ . Therefore, the machine will always be able to make a fraction out of whatever we give it, not by changing any bits, but merely by assuming the binary point to always precede T29 of the word.

Of course addition and subtraction will yield the same, familiar results, as we interpret them, since these operations will be performed on fractions all of which have the same denominator.

If

$$a + b = c$$

, then  $\frac{a}{228} + \frac{b}{228} = \frac{c}{228}$ .

Regardless of the fact that we might be considering a and b as integers, and the computer is considering them as fractions, the fraction which results in the computer must represent the integer c, as we interpret it. We will be able to convert the bits of the result as a binary integer and arrive at the decimal integer equivalent.

If a = 1, b = 2, c will equal 3. We can so place a in a word in memory that it will be of the form shown above. We interpret this as  $a \cdot 2^{-28}$ . We can similarly place b in another word, knowing that it will be similarly interpreted. We can then transfer a to AR (D = 28), and b to AR (D = 29), and they will be added in AR. The sum in AR will appear as shown above. We know it is really  $c \cdot 2^{0} \cdot 2^{-28}$ , and we interpret it as  $c \cdot 2^0$ , or 3.

Suppose, in the example above, we wanted to add numbers containing fractional as well as integral bits. Let a = 1.5 and b = 2.75. sum of these, c, must equal 4.25. We must first determine how many bits will be required to express the longest fraction in the binary equivalents of these numbers. .5(10) = .1(2), which is 1/2. .75(10) = .11(2), which is 1/2 + 1/4 = 3/4. .25(10) = .01(2), which is 1/4. The most bits required by any fraction involved are two. Therefore, if two fractional bits are reserved, each number involved can be fully expressed. Note that not all decimal fractions will convert evenly to binary fractions. Sometimes a programmer must decide what accuracy is needed, and let this determine the number of fractional bits needed.

When we speak of fractional bits, as in the paragraph above, we are referring to bits which we will interpret as fractional, as opposed to those which we will interpret as integral. When we say that the computer holds  $a \cdot 2^{-28}$ , we are saying that we know that a, as it appears in the machine, is in the form,  $a \cdot 2^0 \cdot 2^{-28}$ , meaning that the true binary point, for us, is 28 bits to the right of the machine binary point.

This means there are no bits left to express any fractional value for a. If we were to place a in a word in memory in such a way that two fractional bits followed the true binary point, and do the same for b and c, then the conditions of the problem in the above paragraph would be met. This means that a, as it appears in the machine, must be in the form,  $a \cdot 2^2 \cdot 2^{-28}$ . For a = 1, the value in the machine would appear as

where the true binary point would be known to be at the point shown by the arrow. In such a case, we say that the machine holds  $a \cdot 2^{-26}$  (note that this equals  $a \cdot 2^2 \cdot 2^{-28}$ ), or, that the true binary point is 26 places to the right of the machine binary point.

Now, using the same process for placing b, and for interpreting c, let's add, using our new values, and check the result.

If we let  $A^*$  be the machine representation of any binary number A, then

$$A* = 2^n \cdot A,$$

where n may range from 0 through -28, depending on the fractional accuracy being carried with A.

The entire subject we have just discussed is called "scaling". In the above expression,  $2^n$  is called the "scale factor" of A. Every number is "scaled" somehow when it is placed in the computer. A is said to be scaled  $2^n$  in the machine. From now on, we won't have to make long, cumbersome references to the true binary point in a number as it appears in the machine; we can simply say the number is scaled in a certain manner, and you will immediately know where the true binary point is.

As you can see, the concept of scaling is really quite simple and straightforward; scaling is a short-hand method of interpreting the numbers that appear in a digital computer.

In ordinary decimal arithmetic, you know that you cannot add

100.962 6.75401, because the decimal points are not lined up correctly. Rather, you can add them, but you shouldn't; the result will be meaningless. Similarly, in ordinary binary arithmetic, you cannot, or at least you sould not, add

# 110.111 1.00011,

because the binary points are not lined up correctly. In the computer, you should not add two numbers which are scaled differently, for the same reason. You can, and occasionally programmers have, but the result is meaningless, as they have found out, much to their chagrin.

Suppose we are to add a + b, where a is scaled  $2^{-15}$ , and b is scaled  $2^{-13}$ . It's obvious that one or the other of these numbers will have to be moved, in order to line up the true binary points prior to the addition. You already know how numbers are moved back and forth within a word in the computer: they're shifted in one direction or the other. In the case of pencil-and-paper arithmetic, the job of lining up the base points of two numbers, in order to add them, is simple: we rewrite the numbers. In the previous binary addition, we would rewrite the numbers as

# 110.111 \_\_\_\_1.00011,

and proceed to add them. Unfortunately, as we shift numbers in a computer, we must lose bits. 29 bits are allotted to each single-precision number; after it is shifted, there will still be only 29 bits allotted to any single-precision number. Thus, if the number is shifted to the left, bits will be lost from the most significant end; if the number is shifted to the right, bits will be lost from the least significant end. In the case under consideration, a can be shifted left two places, increasing it by a factor of  $2^2$ , and thus rescaling it from  $2^{-15}$  to  $2^{-13}$ , and making it compatible with b. Or b can be shifted to the right two places, decreasing it by a factor of  $2^{-2}$ , and thus rescaling it from  $2^{-13}$ , making it compatible with a.

Which would be the better scheme can be determined from consideration of a number of factors:

- the desired scaling of the answer, if any particular scaling is desired;

- 2. the number of integral bits that must be allowed to insure that overflow will not occur when the numbers are added (this can be determined by considering the largest possible sum of a and b, and in all events, this number of bits must be allowed, regardless of what shifting is necessary to insure it; otherwise, the answer will be erroneous);

- 3. the fractional accuracy desired in the sum.

From these considerations and perhaps others, unique to a given problem, you will determine the shifting that is required prior to the addition. It may be that both numbers will have to be shifted. In any event, once you have decided that shifting is necessary prior to an addition in your program, you will, of course, need a command which will direct the computer to do it.

The shift command is another special command, with D=31, S=26, C=1 (or any other non-zero number), and T=a relative timing number (similar in function to T for a multiply or divide command). The command will be immediate, and, like multiplication and division, it is double-precision in nature. Two word-times are required for each shift of one bit-position. Therefore, two times the number of bit-positions desired in the shift =T. If you wished to shift a number 10 bit-positions in either direction, T of the shift command would equal 20. Because this operation is immediate and double-precision in nature, it must be located at an odd word-time.

You have already seen that shifting can take place in the two-word registers, and this is where the shifting caused by this command will occur. When this command is executed, ID will shift to the right the indicated number of bit-positions, and, simultaneously, MQ will shift to the left the same number of bit-positions. If you have one number you want to shift, prior to giving the shift command you must place that number in the appropriate two-word register. Either half of the register will do for a single-precision number. You might have a number in each of these registers, one moving to the right, the other to the left.

Notice, if you have a single-precision number you wish to shift to the right, and you load that number in  $ID_1$ , then execute the shift command, the number will move to the right, and the vacated bits will be filled in with 0's, which, of course, would be fine. But, under the same conditions, if you loaded that number in  $ID_0$ , the vacated bit-positions in  $ID_0$  would be filled in with bits from  $ID_1$ , and unless ID had been previously cleared, the single-precision word containing your number would receive "garbage", which could very well contain 1's. Of course this would change your number, making it erroneous. A similar situation, but in reverse, holds true for the shifting of a single-precision number to the left in MQ.

You are probably wondering why any non-zero C is permissible in the command discussed above, and why a C of zero is not permissible. The only function of a C in this command is to distinguish it from a similar command, with D = 31, S = 26, and C = 0. The latter is also a shift command, calling for the exact operation described above, but if C = 0, a tally of the shifts performed will be kept in AR. For each complete shift of the registers by one place,  $1 \cdot 2^{-28}$  will be added to the present contents of AR.

Of course the operation called for by this second shift command will cease at the end of the indicated number of word-times, just like any other command. But it will also cease if an end-around-carry is generated in AR, regardless of whether or not the indicated number of word-times have been consumed. In other words, this shift is performed under control of AR.

An example of the usefulness of such a command might be the following: rescale the binary number x, in the computer, by a factor of 2(a-b), where a and b will also be available in the computer. Assume all numbers are single-precision. When you originally write your program, you won't know how many shifts to call for to be performed on x. As a matter of fact you won't even know in which direction x is to be shifted. All this depends on the current values of a and b.

You could subtract b from a in AR, and, depending on the sign (+ or -) of the answer, you could load x into the proper half of the proper two-word register:  $ID_1$  if x is to be shifted to the right, because the sign of (a - b) is negative;  $MQ_0$  if x is to be shifted to the left, because the sign of (a - b) is positive. There is an implication here that some provision is available to programmers to cause their programs to automatically determine which of two alternate logical paths to follow, based on inspection of a given condition in the computer. This is correct, and the method available for doing this will be discussed shortly, in pages 105 - 109. For the moment, you may assume that such a decision has been made, and x is in the proper two-word register.

The problem now is to use the number in AR to control the shifting process. We know that the shift command we want has D = 31, S = 26, C = 0. It's operation will cease either when an end-around-carry has been generated in AR or when the number of word-times called for by T has been consumed, whichever occurs earlier. We will set T with some maximum number, so that, unless (a - b) is useless (due to the fact that it calls for so many shifts that all of x will be lost), (a - b) will effectively control the process. Assuming that we want only a single-precision answer,  $x \cdot 2(a-b)$ , from either ID1 or MQ0, the maximum number of shifts that can be performed in either direction, without losing all significance, will be twenty-seven. On the twenty-eighth shift in either direction, all twenty-eight magnitude bits of the original x will be lost. We will therefore set T = 54 (= 2·27). And thus we have the shift command that will be included in our program.

The problem now is to so set AR that, after (a - b) shifts have been performed, and  $(a - b) \cdot 1 \cdot 2^{-28}$  has been added to AR, an end-around-carry will be generated. Any positive number plus its negative complement will yield +0 in the computer. Therefore, if we start with the negative complement of (a - b) in AR, and if we add  $1 \cdot 2^{-28}$  to it (a - b) times, we will have generated, in AR, the quantity,

$$-|(a-b)| \cdot 2^{-28} + |(a-b)| \cdot 2^{-28}$$

and this must be  $\pm 0$ . Because we cannot know that (a - b) will always be positive, we use its absolute value, which of course will be positive. After the last shift, there will be an end-around-carry, and the sign will be changed to  $\pm 1$ . The end-around-carry will halt the shifting process.

Of course the same scaling rules that apply to addition of single-precision numbers apply as well to the subtraction of single-precision numbers.