Control Data® 3400 Computer System Preliminary Reference Manual

This manual provides information for the machine-language use of the 3400 computer. Its intention is to describe the capabilities of the hardware. Options and constraints for programming are noted. Some programming examples are given to illustrate how instructions perform.

Other than using COMPASS mnemonics to abbreviate titles of instructions, no softwear systems are used in describing instructions.

The information is preliminary and subject to change.

December, 1963

Publication No. 282b

(Pub. No. 282b obsoletes Pub. No. 282a and includes all corrections and additions.)

© 1963, Control Data Corporation

Printed in United States of America

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 501 Park Avenue Minneapolis 15, Minnesota

|           |                    | RECORD          | OF CHA                                           | ANGE NOTICES |

|-----------|--------------------|-----------------|--------------------------------------------------|--------------|

| C. N. NO. | DATE<br>ORIGINATED | DATE<br>ENTERED | INITIALS                                         | REMARKS      |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 |                                                  |              |

|           |                    |                 | <del>                                     </del> |              |

|           |                    |                 | <del> </del>                                     |              |

|           |                    |                 |                                                  |              |

|           |                    |                 | <u> </u>                                         |              |

|           |                    |                 |                                                  |              |

# **CONTENTS**

| Chapter I — Basic System Description        |       | Jumps and Stops                         |              |  |

|---------------------------------------------|-------|-----------------------------------------|--------------|--|

| 3400 System Characteristics                 | 1 - 1 | Normal Jump                             | 3 - 15       |  |

| Basic 3400 System                           | 1-2   | Return Jump                             | 3-16         |  |

| Options                                     | 1 - 2 | Character Handling                      | 3 - 17       |  |

| Chapter II — Storage Section                |       | Internal Function                       | 3-18         |  |

| Storage Word                                | 2-1   | Internal Sense                          | 3-21         |  |

| Storage Addressing                          | 2-1   | Augment                                 | 3-21         |  |

| Chapter III — Computation Section           |       | Enter Upper Bound; Enter Lower Bound    | 3 - 22       |  |

| Logical Description                         | 3-1   | Chapter IV — Interrupt System           |              |  |

| Arithmetic Section                          | 3-1   | Logical Description of Interrupt System | 4-1          |  |

| Control Section                             | 3-2   | Interrupt Register                      | 4-1          |  |

| Description of Instructions                 | 3-2   | Interrupt Mask Register                 | 4-1          |  |

| Class I                                     | 3-3   | Product Register                        | 4-1          |  |

| Class II                                    | 3-3   | Categories of Interrupts                | 4-1          |  |

| Class III                                   | 3-3   | Category I                              | 4-1          |  |

| Class IV Miscellaneous                      | 3-3   | Category II                             | 4-2          |  |

| Description of Designators                  | 3-4   | Category III                            | 4-3          |  |

| Address Modification                        | 3-4   | Programming Cautions                    | 4-3          |  |

| Address Modification Modes                  | 3-5   | Chapter V — Input/Output                |              |  |

| Execution of Instructions                   | 3-5   | Input/Output Instructions               | 5-2          |  |

| Symbols                                     | 3-6   | Connect                                 | 5-2          |  |

| Order of Instructions in Basic Computer     | 3-6   | Function                                | 5-3          |  |

| Instructions Added by Floating Point Option | 3-9   | Read                                    | 5-4          |  |

| Inter-register Transmission                 | 3-10  | Write                                   | 5-4          |  |

| Full-Word Transmission                      | 3-10  | Copy Status                             | 5 - 5        |  |

| Address Transmission                        | 3-10  | Copy Product Register                   | 5 - 5        |  |

| Fixed Point Arithmetic                      | 3-11  | Clear Channel                           | 5-6          |  |

| Single Precision Floating Point Arithmetic  | 3-11  | Change Control Word                     | 5-6          |  |

| Address Arithmetic                          | 3-12  | Control Word                            | 5-6          |  |

| Logical                                     | 3-12  | Auto-Load                               | 5-7          |  |

| Shifting                                    | 3-13  | Chapter VI — Parity                     |              |  |

| Scale                                       | 3-13  | Parity Generation                       | 6-1          |  |

| Replace                                     | 3-14  | Data Parity Generation                  | 6-1          |  |

| Storage Test                                | 3-14  | Parity Generation for 1/0 Channel       | <b>5</b> - ( |  |

| Storage Search                              | 3-15  | Transmissions                           | 6-1          |  |

| Parity Checking                              | 6-1    | Indicators                                | 8-1          |

|----------------------------------------------|--------|-------------------------------------------|--------------|

| Parity Checking on Storage or                | 6-1    | Codes                                     | 8 - 2        |

| Transmission of Data                         | 0-1    | Connect                                   | 8 - 2        |

| Parity Checking on I/O Channel Transmissions | 6-2    | Function                                  | 8 - 2        |

| Parity Errors                                | 6-2    | Status                                    | 8 - 4        |

| Operand Parity Error                         | 6-2    | Programming                               | 8 - 4        |

| Instruction Parity Error                     | 6-2    | Printer Preparation                       | 8 - 4        |

| I/O Channel Transmission Parity Error        | 6 - 2  | Clear                                     | 8 - 4        |

| Interrupt Selection on I/O Parity Error      | 6-3    | Connect                                   | 8 - 5        |

| External Equipment Parity Error              | 6-3    | Check Status                              | 8 - 5        |

| · · · · · · · · · · · · · · · · · · ·        |        | Function                                  | 8 - 5        |

| Chapter VII — 3401 Console                   |        | Write                                     | 8 - 5        |

| Switches                                     | 7 - 1  | Format Tape Preparation                   | 8 - 6        |

| Indicators                                   | 7 - 2  | Chapter IX — 3691 Paper Tape I            | Reader/Punch |

| Typewriter                                   | 7 - 5  | Introduction                              | 9-i          |

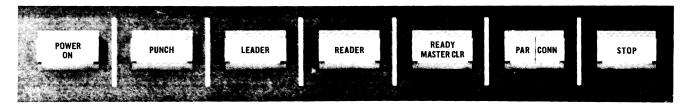

| Connect                                      | 7 - 5  | Switches and Indicators                   | 9-1          |

| Function                                     | 7 - 5  | Codes                                     | 9-3          |

| Set Interrupt on Abnormal Operation          | 7 - 5  | Connect                                   | 9-3          |

| Clear Interrupt on Abnormal Operation        | 7 - 5  | Function                                  | 9-3          |

| Clear Interrupt                              | 7 - 5  | Status                                    | 9 - 4        |

| Status                                       | 7 - 5  | Programming Notes                         | 9 - 4        |

| Ready                                        | 7 - 5  | Reader                                    | 9 - 4        |

| Busy                                         | 7 - 5  | Punch                                     | 9 - 4        |

| Upper/Lower Case                             | 7 - 7  |                                           |              |

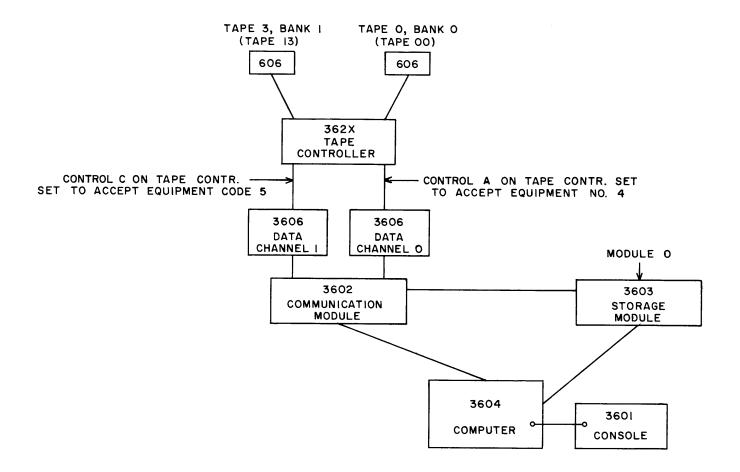

| End of Line                                  | 7 - 7  | Chapter X — 362X Magnetic Ta <sub>l</sub> |              |

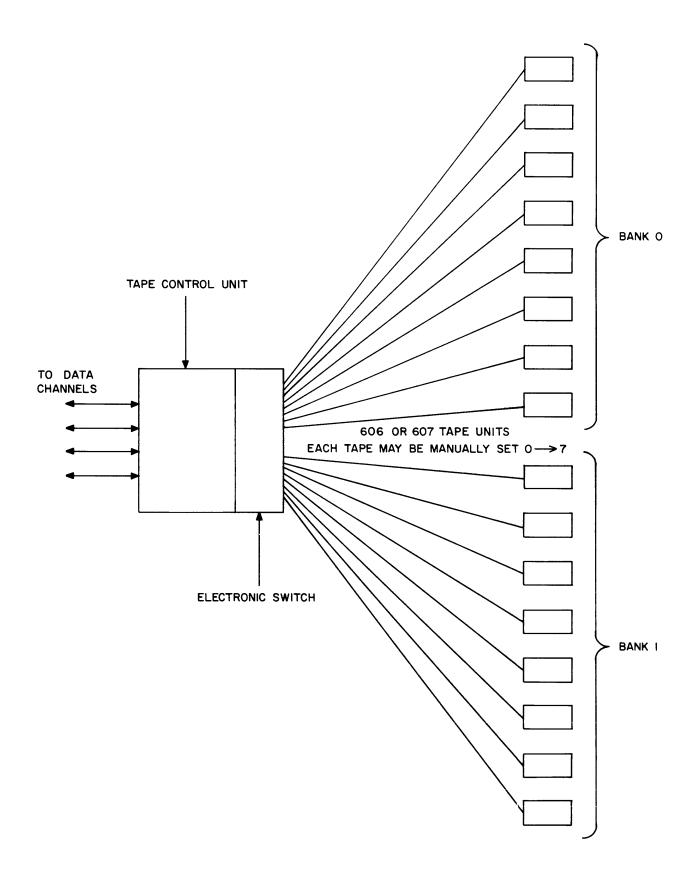

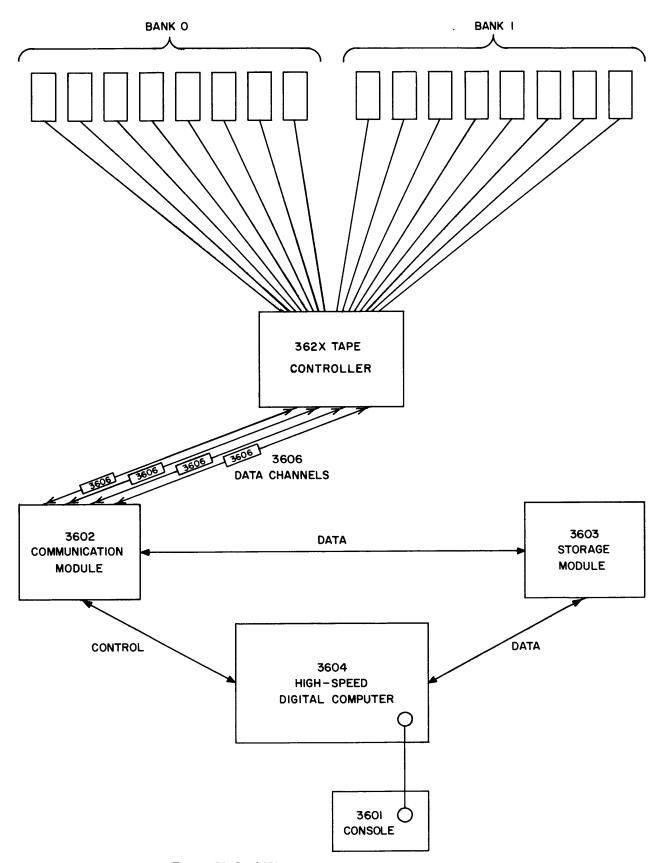

| Type Parity Error                            | 7 - 7  | Introduction                              | 10 - i       |

| Programming                                  | 7 - 7  | Unit Selection                            | 10 - 4       |

| Set Tabs, Margins, and Spacing               | 7-7    | Data Transmission                         | 10 - 5       |

| Clear                                        | 7 - 7  | Codes                                     | 10 - 7       |

| Connect                                      | 7 - 8  | Clear                                     | 10 - 7       |

| Check Status                                 | 7 - 8  | Connect                                   | 10 - 7       |

| Function                                     | 7 - 8  | Status                                    | 10 - 7       |

| Write                                        | 7 - 8  | Status Definitions                        | 10 - 8       |

| Read                                         | 7 - 8  | Function and Format                       | 10-9         |

|                                              |        | Function                                  | 10 - 9       |

| Chapter VIII — 3655 High-Speed Line P        | rinter | Format                                    | 10-10        |

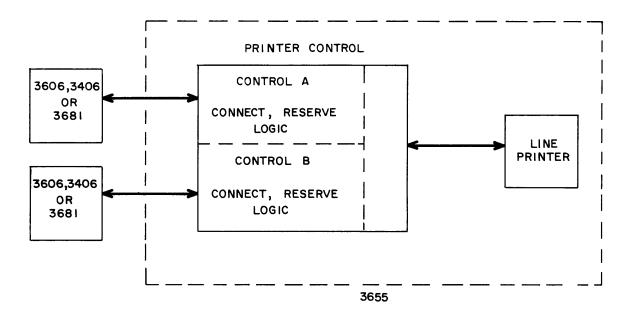

| Typical Printer Configuration                | 8-1    | Interrupt                                 | 10-11        |

| Switches                                     | 8 - 1  | Codes                                     | 10-11        |

| Write                            | 10-12     | 0-12 Chapter XIII — 3644 Card Punch Controller |               |  |

|----------------------------------|-----------|------------------------------------------------|---------------|--|

| Read                             | 10-12     | Introduction                                   | 13-i          |  |

| Reverse Read                     | 10-12     | Hollerith Conversion                           | 13-1          |  |

| Programming Example              | 10-13     | Hole Count Comparison                          | 13-1          |  |

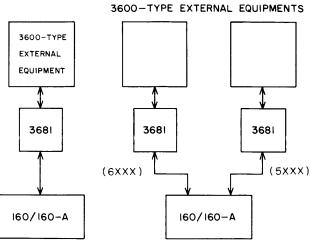

| Chapter XI — 3681 Data Channel ( | Converter | Timing                                         | 13-1          |  |

| Introduction                     | 11-i      | Indicators and Switches                        | 13-3          |  |

| Switches                         | 11-1      | Codes                                          | 13 - 4        |  |

| Non-Satellite/Satellite Systems  | 11-1      | Connect                                        | 13-4          |  |

| Non-Satellite                    | 11-1      | Function                                       | 13 - 4        |  |

| Satellite                        | 11-1      | Status                                         | 13 - 5        |  |

| Programming                      | 11-3      | Programming                                    | 13 - 5        |  |

| Connection                       | 11-3      | CL . VIV 2/40 C LD L                           | <b>6</b> . II |  |

| Status                           | 11-3      | Chapter XIV — 3649 Card Reade                  |               |  |

| Function                         | 11 - 3    | Introduction                                   | 14-i          |  |

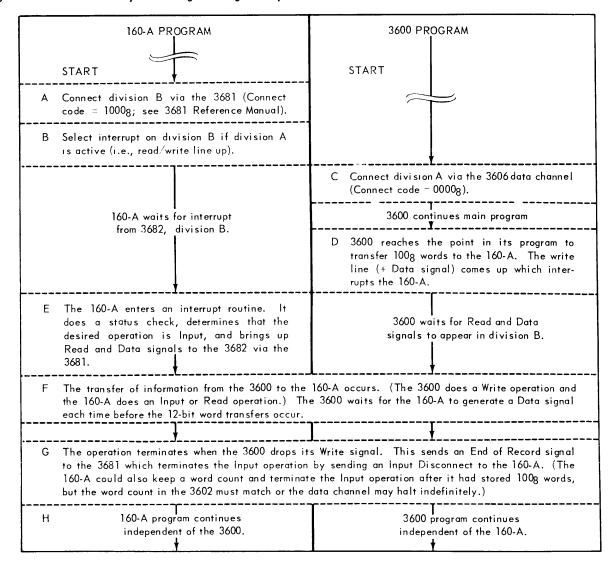

| Programming Example              | 11-4      | Operation and Programming                      | 14-1          |  |

| Program Explanation              | 11-5      | Switches<br>Indicators                         | 14-1<br>14-2  |  |

| Chapter XII — 3682 Satellite Co  | oupler    | Card Reader Preparation                        | 14-2          |  |

| Introduction                     | 12-i      | Reader Conditions                              | 14-2          |  |

| Switches                         | 12 - 2    | Codes                                          | 14-3          |  |

| Indicators                       | 12 - 2    | Connect                                        | 14-3          |  |

| Function Codes                   | 12-3      | Function                                       | 14-3          |  |

| Status Lines                     | 12-3      | Status                                         | 14-4          |  |

| Programming                      | 12-3      | Program Timing                                 | 14-5          |  |

| Clear                            | 12 - 3    | Reader Codes                                   | 14-5          |  |

| Connect                          | 12 - 4    |                                                |               |  |

| Status                           | 12 - 4    | Appendices                                     |               |  |

| Function                         | 12 - 4    | A. Interruptable Conditions and F              | aults         |  |

| Read/Write                       | 12 - 5    | B. Index to Instructions (Octal Co             | odes)         |  |

| Expanded 3600 Satellite          | 12-5      | C. Index to Instructions (Mnemon               | ic Codes)     |  |

| Programming Example              | 12 - 5    | D. Control Data 3400 Computer in               | structions    |  |

# FIGURES

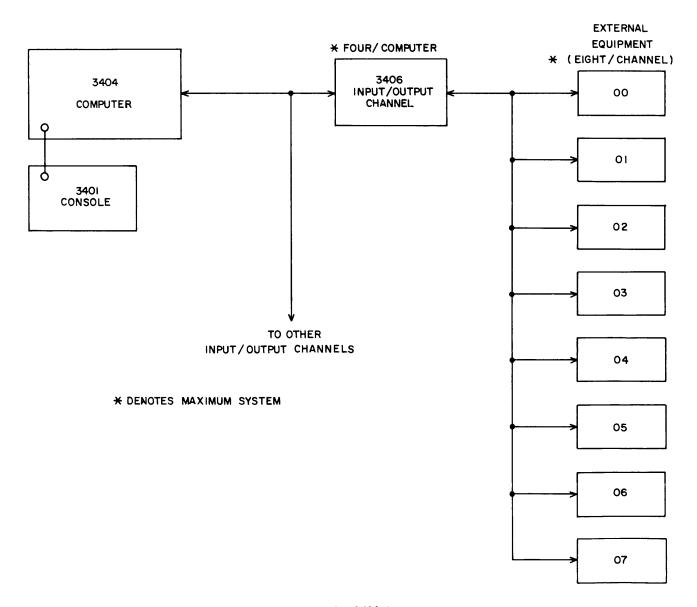

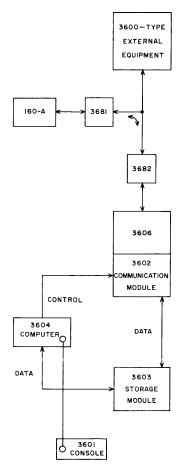

| 1-1    | 3400 Computer System            | 1 - 2  |        | TABLES                              |         |

|--------|---------------------------------|--------|--------|-------------------------------------|---------|

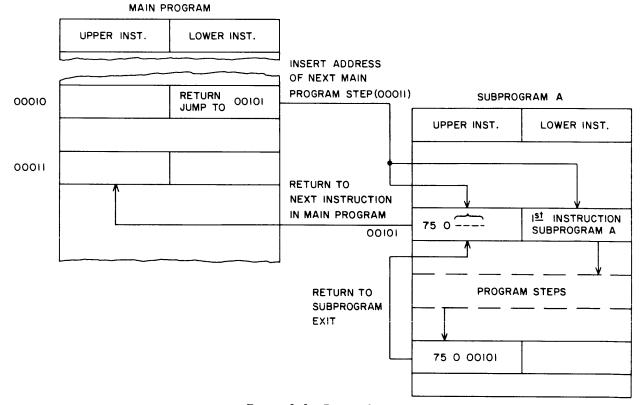

| 3-1    | Return Jump                     | 3-16   | 3-1    | Arithmetic Properties of Registers  | 3-1     |

| 5-1    | 3400 System                     | 5-1    | 4-1    | Assignment of Bits                  | 4-2     |

| 7-1    | System Status Display Panel     | 7 - 2  | 7-1    | Console Switches                    | 7-1     |

| 8-1    | Typical Printer Configuration   | 8-1    | 7-2    | Display Panel Indicators            | 7 - 3   |

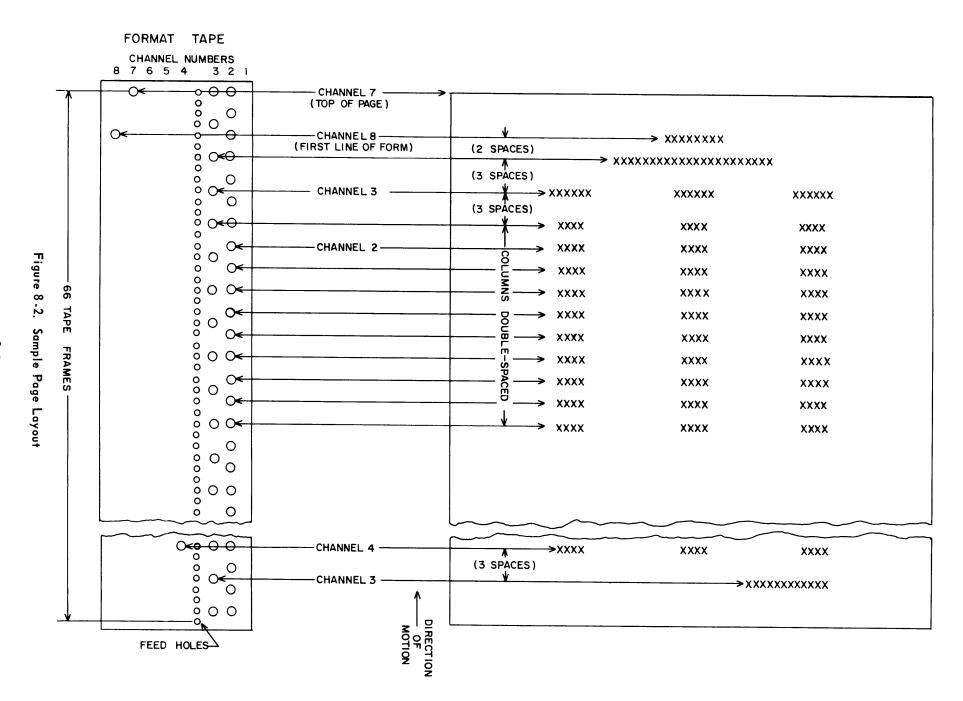

| 8 - 2  | Sample Page Layout              | 8 - 7  | 7-3    | 731 Typewriter Codes                | 7 - 6   |

| 9-1    | 3691 Controls                   | 9-1    | 7 - 4  | Connect, Function, and Status Codes | 7 - 7   |

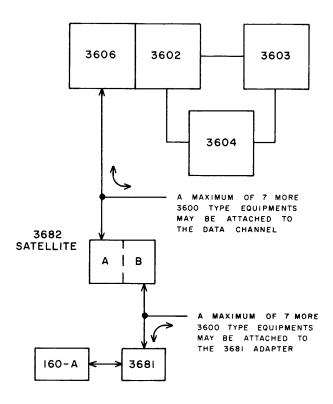

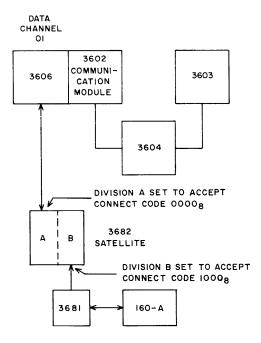

| 11-1   | Non-Satellite System            | 11-1   | 8-1    | Connect, Function, and Status Codes | 8 - 2   |

| 11 - 2 | Satellite System                | 11-1   | 8-2    | 1612 Line Printer Codes             | 8 - 3   |

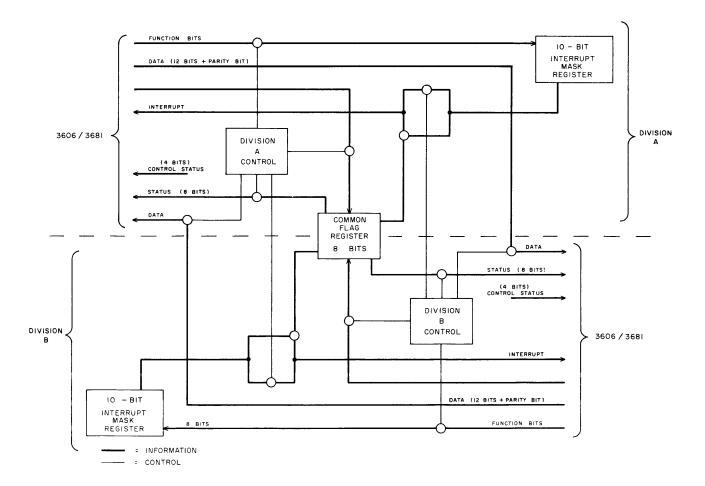

| 12 - 1 | 3682 Block Diagram              | 12-1   | 9-1    | Operating Codes and Status Response | s 9 - 2 |

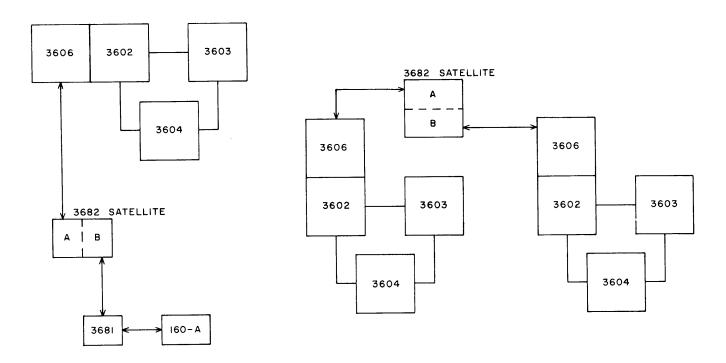

| 12 - 2 | Typical 3682 Configurations     | 12 - 2 | 11-1   | Select and Status Codes             | 11-2    |

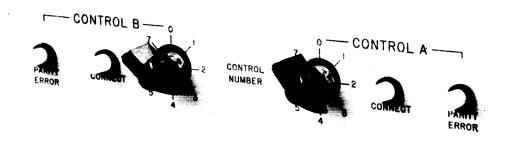

| 12 - 3 | 3682 Switch and Indicator Panel | 12 - 2 | 13-1   | BCD/Hollerith/Card Codes            | 13-2    |

| 12 - 4 | Expanded Satellite System       | 12-5   | 13-2   | 3644 Codes                          | 13-4    |

| 12 - 5 | Satellite System Programming    |        | 14 - 1 | Connect, Function, and Status Codes | 14 - 3  |

|        | Example                         | 12 - 6 | 14 - 2 | BCD/Hollerith/Card Codes            | 14 - 6  |

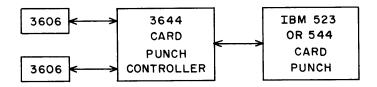

| 13 - 1 | Typical 3644 Configuration      | 13-1   |        |                                     |         |

| 14-1   | 3649 Control Panel              | 14-1   |        |                                     |         |

| 14-2   | Card Timing Chart               | 14-5   |        |                                     |         |

# CONTROL DATA® 3400 COMPUTER SYSTEM PRELIMINARY REFERENCE MANUAL

# CHAPTER I BASIC SYSTEM DESCRIPTION

The CONTROL DATA\* 3400 is a solid-state, stored-program, general-purpose digital computing system, with large storage capacity and fast data transmission and computation speeds.

The 3400 system incorporates features of the CONTROL DATA 3600 Computer to provide program compatibility with this machine. With the several available options, a variety of configurations is possible.

#### 3400 SYSTEM CHARACTERISTICS

Stored-program, general-purpose computer

Parallel mode of operation

Single address logic

51-bit storage word (48 bits of data, 3 parity bits)

Six 15-bit index registers

Indirect addressing

Magnetic core storage

32,768 51-bit words (Standard) 16,384 51-bit words (Optional)

Input/Output

Transmission of 48-bit words (12-bit bytes)

Up to four separate bidirectional input/output channels

System interrupt

Flexible repertoire of instructions

Fixed point arithmetic (integer)

Single-precision, floating-point arithmetic (optional)

Logical and masking operations

Character handling instructions

Indexing

Storage searching

Binary arithmetic

Modulus  $2^{48}$  - 1 (one's complement) for single

precision operations

Completely solid-state

Diode logic

Transister amplifiers

Ready access to circuits

Console includes:

1/O Typewriter and display panel

Inter-computer communication

3400 <del>--- 3600</del> 3400 <del>--- 3400</del>

Via 3682 Satellite

Coupler

3400 -- 160/160 -A

Via 3682 Satellite and 3681 Data Channel Converter

<sup>\*</sup> Registered trademark of Control Data Corporation.

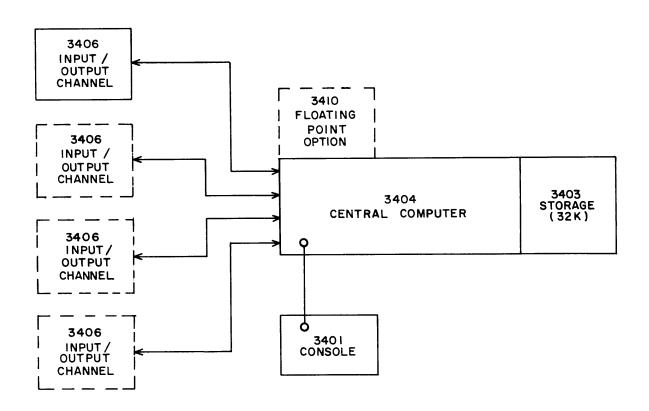

#### **BASIC 3400 SYSTEM**

The basic 3400 system consists of a central computer, an input/output section, magnetic core storage, and a console. Over-all system operation depends on the integral operation of these elements. (See figure 1-1.)

Included in the basic computing system are operator and maintenance consoles. The consoles contain all the controls and indicators necessary to operate the system.

#### **OPTIONS**

For greater systems capability, the 3400 computing

system may be expanded with several available options. These options are:

#### 1) Floating point option (3410)

This adds four single-precision, floating-point instructions.

#### 2) 16,384 word storage

The standard 3400 system includes 32,768 words of core storage. An optional system is available with only 16,384 words of core storage.

#### 3) Additional Input/Output channels (3406)

The basic system may be expanded to a maximum of four bidirectional I/O channels.

Figure 1-1. 3400 Computer System (Dotted Lines Indicate Optional Additions)

# **CHAPTER II**STORAGE SECTION

The magnetic core storage section provides high-speed, random-access storage for 32,768 words. The storage section consists of the storage elements themselves, and the circuitry for addressing the storage elements.

#### STORAGE WORD

A storage word may be two 24-bit instructions, a single 48-bit instruction, or a 48-bit data word.

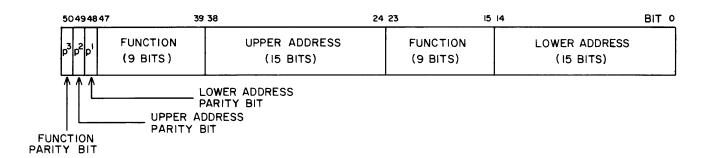

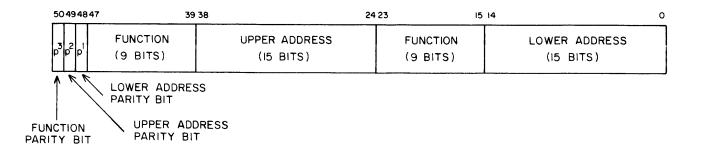

Three parity bits are appended to each 48-bit word; thus a storage word is 51 bits in length. The format of a typical storage word is diagrammed below.

The storage word is divided into three portions:

- 1) a 15-bit lower address,

- 2) a 15-bit upper address, and

- 3) an 18-bit function portion, distributed in the storage word as diagrammed. A parity bit accompanies each of these portions when the word is stored. The parity bit (P1) associated with the lower address portion is placed in bit 48 of the storage word, parity bit P2 (upper address) is placed in bit 49, and parity bit P3 (function) is placed in bit 50.

When part of the word or the entire 51 bits is read from storage, the appropriate parity bit(s) accompanies the word and the computer checks the word for parity.

#### STORAGE ADDRESSING

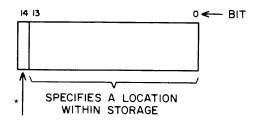

The location of each word in storage is identified by an assigned number (address). An address consists of 15 bits interpreted as shown below:

The following storage locations are used with return jump instructions for interrupt processing (unless the

<sup>\*1)</sup> In a 3400 system with 32,768 words of core storage: If this bit is a "0", it specifies the lower section of storage which contains addresses 00000g--37777g; if this bit is a "1", it specifies the upper section of storage which contains addresses 40000g--77777g.

<sup>2)</sup> In a 3400 system with 16,384 words of core storage, this bit is always "0". It specifies the one storage section which contains addresses 000008--377778.

interrupt category is removed by adding an option):

00007 } Category | Interrupt 00030 00031 | Category | Interrupt 00032 00033 |

00020 Category III Interrupt

See Chapter 4 for additional information on the uses of these storage locations.

Address 000008 is reserved for use with a return jump instruction when the Restart switch is depressed. (See chapter 7.)

# CHAPTER III COMPUTATION SECTION

The computation section performs calculations and processes data in a parallel binary mode through the step-by-step execution of individual instructions. The instructions and data are stored in the storage section(s).

#### LOGICAL DESCRIPTION

Functionally, computation section may be divided into an arithmetic section and a control section.

#### **Arithmetic Section**

The arithmetic section performs the arithmetic and logical operations necessary for executing instructions. It consists primarily of several operational registers. The operational registers are described below. Table 3-1 lists the arithmetic properties of the registers.

#### A Register

Nearly all arithmetic and logical operations use the 48-bit A register (Arithmetic register). The contents of this register may be shifted to the right or to the left, separately or in conjunction with the Q register. In certain conditional instructions, the A register is used to hold control quantities which govern operations.

#### **Q** Register

The 48-bit Q register (Auxiliary Arithmetic register) assists the A register in performing arithmetic and logical operations. The contents of the Q register may be shifted right or left, separately or in conjunction with the A register. Q may also be used with the A register to form a double length register, AQ or QA. In addition to assisting the A register, certain instructions reference the Q register directly.

#### P Register

The 15-bit P register functions as a program address counter. The P register holds the address of each program step. After executing the instruction (or instructions) contained in the program step, the quantity in P is advanced by one to the address of the next instruction.

When a jump condition is met, the P register is set to the quantity specified by the execution address of

| Table 3- | 1. 7 | Arith | ımetic | Pro | perties | of | Registers |  |

|----------|------|-------|--------|-----|---------|----|-----------|--|

|----------|------|-------|--------|-----|---------|----|-----------|--|

| Register        | No. of<br>Stages | Modulus            | Complement<br>Notation | Arithmetic  | Result   |

|-----------------|------------------|--------------------|------------------------|-------------|----------|

| A Register      | 48               | 2 <sup>48</sup> -1 | one's                  | subtractive | signed*  |

| Q Register      | 48               | 2 <sup>48</sup> -1 | one's                  |             | signed   |

| P Register      | 15               | 2 <sup>15</sup>    | two's                  | additive    | unsigned |

| Index Registers | 15               | 2 <sup>15</sup> -1 | one's**                |             |          |

<sup>\*</sup> The result of an arithmetic operation in A satisfies A ≤ 2<sup>47</sup>-1 since A is always treated as a signed quantity. When the result in A is zero, it is always represented as 000...000 except when 111...111 is added to 111...111. In this case, the result is 111...111 (negative zero).

<sup>\*\*</sup>Though the index registers have no arithmetic capabilities themselves, address modification using the index registers is performed modulus 2<sup>15</sup>-1 (one's complement).

the jump instruction. If the instruction is a return jump, the contents of P are stored before executing the jump, permitting a return to the program sequence after the jump is made.

Since the P register is a two's complement additive register, it can generate storage addresses in sequence from 00000 to 777778. When a count of 777778 is reached, the next count in P reduces its value to 00000. (Note that in generating storage addresses by adding the contents of an index register to a base quantity, address 777778 cannot be reached. Refer to the section on Address Modification Modes, (p. 3-5).

#### **U** Register

The 48-bit Program Control register (U) holds the program step while it is being executed. All operations necessary to execute an instruction are governed by the contents of this register.

#### B<sup>1</sup> - B<sup>6</sup> (Index Registers)

Six 15-bit index registers may be used to:

- 1) Hold quantities used as address modifiers.

- 2) Hold control quantities for certain instructions.

The index registers may also be explicitly referenced by certain instructions (refer to Repertoire of Instructions section).

#### Interrupt Register

Each interruptible condition in the system is connected to a particular bit position of the Interrupt register. The lower bit positions detect internal interrupt conditions such as overflow, divide fault, and exponent fault. The upper bit positions are interrupt lines coming from each of the four possible communication channels.

#### Interrupt Mask Register

This register enables testing of external interrupt lines and internal conditions. The bit positions of this register match the Interrupt register. Interrupt occurs on a condition if the bit of the Mask register is set to "1". The Internal Function instruction may be used to set or clear bits in this register.

#### **Product Register**

The product register contains the bit-by-bit logical product of the Interrupt register and the Interrupt Mask register (refer to the Interrupt section).

#### Bounds Registers (Upper and Lower)

Two bounds registers serve as a memory and jump lock-out. The Lower bounds register holds an 8-bit Lower bound address. The Upper bounds register holds an 8-bit upper bound address. The upper 8 bits of the 15-bit storage address S are compared with the contents of the bounds registers when bounds checking is in effect.

#### **Control Section**

The control section of the computer directs the operations required to execute instructions and establishes the timing relationships needed to perform these operations in the proper sequence. It also sends the preliminary commands necessary to begin the processing of input/output data.

The control section acquires an instruction from storage, interprets it, and sends the necessary commands to other sections. A program step may be a single 48-bit instruction or a pair of 24-bit instructions which together occupy a single storage location as a 48-bit word.

The program address counter, P, is a two's complement additive register. It provides program continuity by generating in sequence the storage addresses which contain the individual program steps. Usually, at the completion of each program step, the count in P is advanced by one to specify the address of the next program step.

The Program Control register, U, holds a program step while it is being executed. If the program step is a pair of 24-bit instructions, the upper instruction is executed first, followed by the lower instruction.

#### DESCRIPTION OF INSTRUCTIONS

A computer word consists of 48 bits and may be interpreted as one 48-bit data word, a 48-bit instruction, or two 24-bit instructions.

Most instructions designated by three-letter mnemonic codes are 24-bit instructions common to the 1604 and 3604 computers. These instructions are arranged in a 48-bit word; the higher order 24 bits are called the upper instruction and the lower order 24 bits are called the lower instruction.

Instructions which are not common to the 1604 computer and designated by mnemonic codes of three or four letters, differ in format and in word length (some are 24 bits; others are 48 bits).

Instruction formats are arranged in four major classes, according to differences in word length and the

position of the function code within the format. A typical format from each class is outlined below. Designators used within these formats are explained at the end of this section. For a comprehensive description of instructions, refer to the Repertoire of Instructions section.

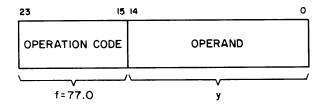

#### Class I

Class I instruction formats are 24 bits in length and have 6-bit function codes, 'f'. All instructions common to the 1604 and 3604 computers and designated by three-letter mnemonic codes are included in this category.

| 23 | 18 | 17 15        | 14        | BIT 0 |

|----|----|--------------|-----------|-------|

|    | f  | b<br>or<br>j | m, y or k |       |

INSTRUCTIONS DESIGNATED BY THREE-LETTER MNEMONICS

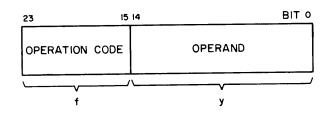

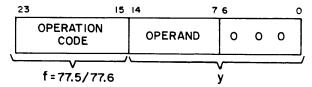

#### Class II

Class II instruction formats are 24 bits in length and have 9-bit function codes. All instructions in this category are designated by mnemonic codes of three letters.

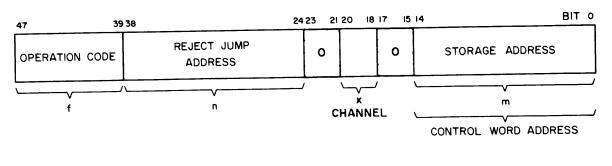

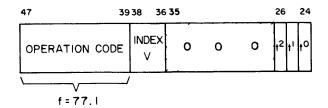

#### Class III

Class III instruction formats are 48 bits in length and have 9-bit function codes. All instructions in this category are designated by mnemonic codes of four letters.

#### Class IV Miscellaneous

See pages 3-17, 3-18, 3-21, and 3-22.

#### DESCRIPTION OF DESIGNATORS

Designators used throughout the Description of Instructions section and in instruction formats are

explained below. For specific interpretations of designators, refer to the individual instructions.

| Designator |                              | Use                                                                                                   |

|------------|------------------------------|-------------------------------------------------------------------------------------------------------|

| Ь          | Index                        | Specifies index register (B) used, or whose contents are used in the operation.                       |

| С          | Connect and Function         | Specifies codes used in Connect and Function instructions.                                            |

| f          | Function Code                | A 6 or 9-bit code (depending on the operation) which specifies the operation to be performed.         |

| i          | Condition                    | Conditions operations in jumps and stops.                                                             |

| k          | Unmodified Shift Count       | Number of shifts to be executed.                                                                      |

| К          | Modified Shift Count         | $[K = k + (B^b)]$                                                                                     |

| m          | Unmodified Execution Address | Address of operand.                                                                                   |

| М          | Modified Execution Address   | $[M = m + (B^b)]$                                                                                     |

| <b>v</b>   | Second Index                 | Specifies second index register (V) used, or whose contents are used in the operation.                |

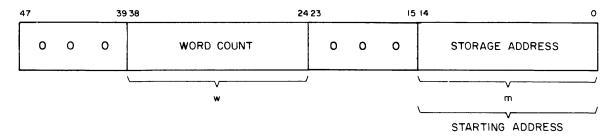

| w          | Word Count                   | A 15-bit quantity which specifies the number of words to be processed in a transfer operation.        |

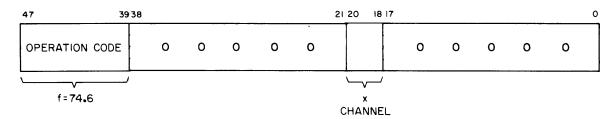

| ×          | Channel Number               | Specifies $1/0$ channel; also used to specify channel whose status will be read or sensed.            |

| у          | Unmodified Operand           | Used in execution address portion of instruction; specifies this address will be used as the operand. |

| Υ          | Modified Operand             | $[Y = y + (B^b)]$                                                                                     |

#### ADDRESS MODIFICATION

The portion of the instruction word designated by 'm', 'y', or 'k', is often termed the base execution address. The base execution address may be used as (1) a shift count, 'k', (2) an operand, 'y', (3) an address of an operand, 'm', in storage. The execution address may be modified or left unmodified depending on the index designator. The execution address is modified by adding the contents of the designated index register to the execution address. If left unmodified, the lower-case symbols 'k', 'y', or 'm', are used. If the address is modified, the symbols are capitalized.

The modified shift count is represented by:

1)

$$K = k + (B^b)$$

where:

= modified shift count

= unmodified shift count (execution address)

(B<sup>b</sup>) = contents of index register b

If the index designator = 0, then K = k.

The modified operand is represented by:

2)

$$Y = y + (B^b)$$

where:

= modified operand

y = unmodified operand (execution address) (B<sup>b</sup>) = contents of index register b

If the index designator = 0, then Y = y.

The modified operand address is represented by:

3)  $M = m + (B^b)$  where:

M = modified address of operandm = unmodified address of operand

(execution address)

$(B^b)$  = contents of index register b If the index designator = 0, then M = m.

#### ADDRESS MODIFICATION MODES

Three possible modes of address modification, as determined by the index designator, are:

- 1) b = 0 No address modification. The execution address is directly interpreted.

- b = 1-6 Relative address modification. The execution address is modified as outlined previously. One's complement arithmetic is used in determining the modified execution address.

#### NOTE

Since one's complement arithmetic is used in determining the relative address, address 777768 is the highest address which can be generated. Address 777778 cannot be reached by indexing. For example, modifying execution address 77776 by adding, in one's complement arithmetic, an index value of 1, results in 00000. During address modification, the modified address will equal 777778 only if: (1) the unmodified execution address equals 777778 and b=0, or (2) the unmodified execution address equals 777778.

3) b = 7 Indirect addressing. A storage reference is made to the location specified by the execution address. The lower order 18 bits of the word at this storage location are interpreted as the index

designator 'b' (3 bits) and execution address (15 bits) of the present instruction. The new index designator may refer to any one of the three modes.

#### **EXECUTION OF INSTRUCTIONS**

A program example and a step-by-step explanation of its execution is outlined below. Instructions from Class I are used in the example to help explain the use of various designators.

The storage reference is initiated at address 00300 (the address held in the P register). The 48-bit word is read from address 00300 and entered into U. Computer operation is now dependent upon the interpretation of the 24-bit instruction in the upper half of U.

The operation code, LDA, and the index designator, 0, are translated. The function of the LDA instruction is to load the A register with the contents of the designated storage location. Because the index designator is 0, the execution address is not modified. The translation of the operation code initiates the sequence of commands which executes the instruction, and the operand in address 00200 is loaded into A.

The lower instruction in U is translated. The ADD instruction causes the quantity in storage location M to be added to the contents of the A register. Since the index designator is not 0 or 7, the contents of the index register are added to the execution address to form M (M = m + (B $^{\rm b}$ ) = 00210 $_{\rm 8}$  + 00100 $_{\rm 8}$  = 00310 $_{\rm 8}$ ). The contents of storage address 00310 are added to the contents of the A register, completing the instruction. The contents of the P register are increased by one and the next program step at address 00301 is read from storage, entered into U, and translated.

Example:

Storage Address

f

b

m

f

b

m

00300

LDA

0

00200

ADD

1

00210

.  $(B^1) = 00100_8$

#### **SYMBOLS**

The following symbols are used in the Order of Instructions section.

| Α              | The A register                                                                                            |

|----------------|-----------------------------------------------------------------------------------------------------------|

| A <sub>n</sub> | The binary digit in position 'n' of the A register                                                        |

| Вр             | Designated index register                                                                                 |

| LA             | Lower address; execution address portion of lower instruction of a program step                           |

| Q              | Auxiliary Arithmetic register                                                                             |

| UA             | Upper address                                                                                             |

| ()             | Contents of a register or storage location                                                                |

| ( )'           | One's complement contents of a register or storage location                                               |

| ( )f           | Final contents of a register or storage location                                                          |

| ( )i           | Initial contents of a register or storage location                                                        |

| #              | A flag to denote the instruction must be located in the upper instruction position of an instruction word |

| v              | The logical inclusive OR function                                                                         |

| <del>*</del>   | The logical exclusive OR function                                                                         |

| ^              | The logical AND function                                                                                  |

# ORDER OF INSTRUCTIONS IN BASIC COMPUTER

| Octal<br>Code | Mnemonic<br>Code | Name                              | Indirect<br>Addressing | Storage *<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------|-----------------------------------|------------------------|-------------------------|-------------------------|----------------------------------|

|               | Inter-Regis      | ster Transmission                 |                        |                         |                         |                                  |

|               | IAQ              | Interchange A and Q<br>(00700554) | No                     | 0                       | No                      | 24                               |

|               | Full-Word        | Transmission                      |                        |                         |                         |                                  |

| 12            | LDA              | Load A                            | Yes                    | 1                       | Yes                     | 24                               |

| 16            | LDQ              | Load Q                            | Yes                    | 1                       | Yes                     | 24                               |

| 20            | STA              | Store A                           | Yes                    | 1                       | Yes                     | 24                               |

| 21            | STQ              | Store Q                           | Yes                    | 1                       | Yes                     | 24                               |

| 13            | LAC              | Load A, Complement                | Yes                    | 1                       | Yes                     | 24                               |

| 17            | LQC              | Load Q, Complement                | Yes                    | 1                       | Yes                     | 24                               |

<sup>\*</sup> If indirect addressing is designated, at least one additional storage reference is required.

## ORDER OF INSTRUCTIONS (Cont'd)

| Octal<br>Code | Mnemonic<br>Code | Name                              | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------|-----------------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Address T        | ransmission                       | _ ,,                   |                       |                         |                                  |

| 61            | SAL              | Substitute Address<br>(lower)     | Yes                    | 1                     | Yes                     | 24                               |

| 60            | SAU              | Substitute Address<br>(upper)     | Yes                    | 1                     | Yes                     | 24                               |

| 04            | ENQ              | Enter Q                           | Yes                    | 0                     | Yes                     | 24                               |

| 10            | ENA              | Enter A                           | Yes                    | 0                     | Yes                     | 24                               |

| 53            | LIL              | Load Index (lower)                | Yes                    | 1                     | No                      | 24                               |

| 52            | LIU              | Load Index (upper)                | Yes                    | 1                     | No                      | 24                               |

| 57            | SIL              | Store Index (lower)               | Yes                    | 1                     | No                      | 24                               |

| 56            | SIU              | Store Index (upper)               | Yes                    | 1                     | No                      | 24                               |

| 50            | ENI              | Enter Index                       | Yes                    | 0                     | No                      | 24                               |

|               | ATI              | Transmit A to Index<br>(0074054b) | No                     | 0                     | No                      | 24                               |

|               | Fixed Poi        | nt Arithmetic                     |                        |                       |                         |                                  |

| 14            | ADD              | Add                               | Yes                    | 1                     | Yes                     | 24                               |

| 15            | SUB              | Subtract                          | Yes                    | 1                     | Yes                     | 24                               |

| 24            | MUI              | Multiply Integer                  | Yes                    | 1                     | Yes                     | 24                               |

| 25            | DVI              | Divide Integer                    | Yes                    | 1                     | Yes                     | 24                               |

|               | Address A        | rithmetic                         |                        |                       |                         |                                  |

| 11            | INA              | Increase A                        | Yes                    | 0                     | Yes                     | 24                               |

| 51            | INI              | Increase Index                    | Yes                    | 0                     | No                      | 24                               |

| 54            | ISK              | Index Skip                        | Yes                    | 0                     | No                      | 24                               |

|               | Logical          |                                   |                        |                       |                         |                                  |

| 40            | SST              | Selective Set                     | Yes                    | 1                     | Yes                     | 24                               |

| 41            | SCL              | Selective Clear                   | Yes                    | 1                     | Yes                     | 24                               |

| 42            | SCM              | Selective Complement              | Yes                    | 1                     | Yes                     | 24                               |

| 43            | SSU              | Selective Substitute              | Yes                    | 1                     | Yes                     | 24                               |

| 44            | LDL              | Load Logical                      | Yes                    | 1                     | Yes                     | 24                               |

| 45            | ADL              | Add Logical                       | Yes                    | 1                     | Yes                     | 24                               |

| 46            | SBL              | Subtract Logical                  | Yes                    | 1                     | Yes                     | 24                               |

| 47            | STL              | Store Logical                     | Yes                    | 1                     | Yes                     | 24                               |

# ORDER OF INSTRUCTIONS (Cont'd)

| Octal<br>Code | Mnemonic<br>Code | Name                       | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------|----------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Shifting         |                            |                        |                       |                         |                                  |

| 01            | ARS              | A Right Shift              | Yes                    | 0                     | Yes                     | 24                               |

| 02            | QRS              | Q Right Shift              | Yes                    | 0                     | Yes                     | 24                               |

| 03            | LRS              | Long Right Shift (AQ)      | Yes                    | 0                     | Yes                     | 24                               |

| 05            | ALS              | A Left Shift               | Yes                    | 0                     | Yes                     | 24                               |

| 06            | QLS              | Q Left Shift               | Yes                    | 0                     | Yes                     | 24                               |

| 07            | LLS              | Long Left Shift (AQ)       | Yes                    | 0                     | Yes                     | 24                               |

| 34            | SCA              | Scale A                    | Yes                    | 0                     | No                      | 24                               |

| 35            | SCQ              | Scale AQ                   | Yes                    | 0                     | No                      | 24                               |

|               | Replace          |                            |                        |                       |                         |                                  |

| 70            | RAD              | Replace Add                | Yes                    | 2                     | Yes                     | 24                               |

| 71            | RSB              | Replace Subtract           | Yes                    | 2                     | Yes                     | 24                               |

| 72            | RAO              | Replace Add One            | Yes                    | 2                     | Yes                     | 24                               |

| 73            | RSO              | Replace Subtract One       | Yes                    | 2                     | Yes                     | 24                               |

|               | Storage Te       | est                        |                        |                       |                         |                                  |

| 36            | SSK              | Storage Skip               | Yes                    | 1                     | Yes                     | 24                               |

| 37            | SSH              | Storage Shift              | Yes                    | 2                     | Yes                     | 24                               |

|               | Search           |                            |                        |                       |                         |                                  |

| 64            | EQS              | Equality Search            | Yes                    |                       | Yes                     | 24                               |

| 65            | THS              | Threshold Search           | Yes                    |                       | Yes                     | 24                               |

| 66            | MEQ              | Masked Equality<br>Search  | Yes                    |                       | Yes                     | 24                               |

| 67            | MTH              | Masked Threshold<br>Search | Yes                    |                       | Yes                     | 24                               |

|               | Jumps and        | Stons                      |                        | ·                     |                         |                                  |

| 22            | AJP              | A Jump                     | No                     | ]*                    | No                      | 24                               |

| 23            | QJP              | Q Jump                     | No                     | 1*                    | No                      | 24                               |

| 55            | IJP              | Index Jump                 | Yes                    | 0                     | No                      | 24                               |

| 75            | SLJ              | Selective Jump             | No                     | 1*                    | No                      | 24                               |

| 76            | SLS              | Selective Stop             | No                     | 1*                    | No                      | 24                               |

<sup>\*</sup> Return jump only

## ORDER OF INSTRUCTIONS (Cont'd)

| Octal<br>Code | Mnemonio<br>Code | c<br>Name                          | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------|------------------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Input/Output     |                                    |                        |                       |                         |                                  |

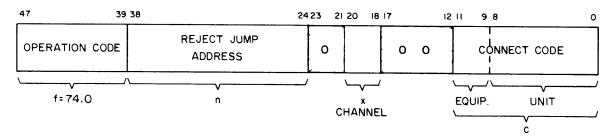

| 74.0          | CONN             | Connect                            | No                     | 0                     | No                      | 48                               |

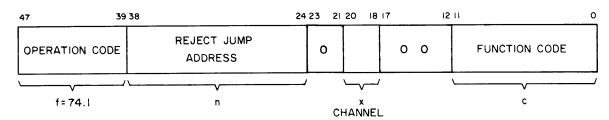

| 74.1          | EXTF             | Function                           | No                     | 0                     | No                      | 48                               |

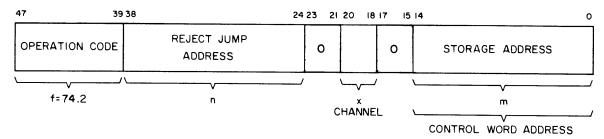

| 74.2          | BEGR             | Read                               | No                     | 0                     | No                      | 48                               |

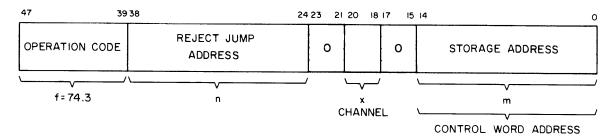

| 74.3          | BEGW             | Write                              | No                     | 0                     | No                      | 48                               |

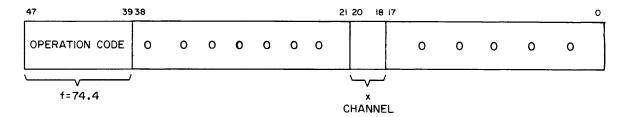

| 74.4          | COPY             | Copy Status                        | No                     | 0                     | No                      | 48                               |

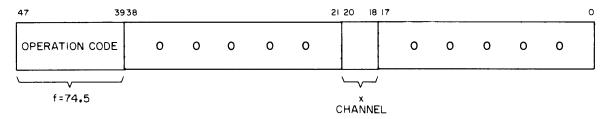

| 74.5          | CLCH             | Clear Channel                      | No                     | 0                     | No                      | 48                               |

| 74.6          | CCWD             | Change Control Word                | No                     | 0                     | No                      | 48                               |

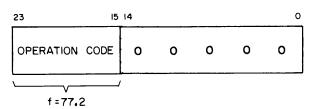

| 77.2          | CIS              | Copy Interrupt Status              | No                     |                       | No                      | 24                               |

| 77.3          | SEN              | Internal Sense                     | No                     | 0                     | No                      | 24                               |

| 77.4          | CPR              | Copy Product Register              | No                     | 0                     | No                      | 24                               |

| 77.0          | INF              | Internal Function                  | No                     | 0                     | No                      | 24                               |

|               | Miscellane       | eou s                              |                        |                       |                         |                                  |

| 77.1          | AUG              | Augment                            | Yes                    | 0                     |                         | 24                               |

| 77.5          | EUB              | Enter Upper Bound                  | No                     | 0                     | No                      | 24                               |

| 77.6          | ELB              | Enter Lower Bound                  | No                     | 0                     | No                      | 24                               |

|               | LDC              | Load Character<br>(63bv 0006500m)  | Yes                    | 1                     | Yes                     | 48                               |

|               | STC              | Store Character<br>(63bv 0006505m) | Yes                    | 2                     | Yes                     | 48                               |

|               | Illegal Co       | des                                |                        |                       |                         |                                  |

| 26            | }                |                                    |                        |                       |                         |                                  |

| 27            | Return Jur       | mp to Address                      |                        |                       |                         |                                  |

| 74.7          | ( 00             | 0020                               |                        |                       |                         |                                  |

| 77.7          | ] ]              |                                    |                        | i                     |                         |                                  |

# INSTRUCTIONS ADDED BY FLOATING POINT OPTION

| Octal<br>Code | Mnemonic<br>Code         | Name                      | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|--------------------------|---------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Single Pre<br>Point Arit | cision Floating<br>hmetic |                        |                       |                         |                                  |

| 30            | FAD                      | Floating Add              | Yes                    | 1                     | Yes                     | 24                               |

| 31            | FSB                      | Floating Subtract         | Yes                    | 1                     | Yes                     | 24                               |

| 32            | FMU                      | Floating Multiply         | Yes                    | 1                     | Yes                     | 24                               |

| 33            | FDV                      | Floating Divide           | Yes                    | 1                     | Yes                     | 24                               |

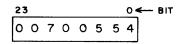

#### INTER-REGISTER TRANSMISSION

Interchange A and Q (IAQ)

The 24-bit Interchange A and Q instruction interchanges the contents of the A and Q registers.

#### **FULL-WORD TRANSMISSION**

In Full-Word Transmission instructions, a 48-bit operand or data word is used in executing the instruction.

#### LDA Load A Op. Code 12

Replaces the contents of A with a 48-bit operand contained in the storage location specified by M. Negative zero is formed in A if the operand at M is equal to negative zero.

#### LAC Load A Complement Op. Code 13

Replaces the contents of A with the complement of a 48-bit operand contained in the storage location specified by M. Negative zero is formed in A if the operand at M is equal to positive zero.

#### LDQ Load Q Op. Code 16

Replaces the contents of Q with a 48-bit operand contained in the storage location specified by M. Negative zero is formed in Q if the operand at M is equal to negative zero.

#### LDQ Load Q Complement Op. Code 17

Replaces the contents of Q with the complement of a 48-bit operand contained in the storage location specified by M. Negative zero is formed in Q if the operand at M is equal to positive zero.

#### STA Store A Op. Code 20

Replaces the contents of the designated storage location, M, with the contents of A.

#### STQ Store Q Op. Code 21

Replaces the contents of the designated storage location, M, with the contents of Q.

#### ADDRESS TRANSMISSION

- In the Address Transmission instructions, only the lower 15 bits of a 24-bit word instruction or data word are used.

- 2) In the LIU and LIL instructions, an index designation of "0" has no meaning and should not be used. If used, these instructions become pass instructions, but use some time in storage reference. The next instruction is then executed. Using "0" as an index designation does not constitute a fault.

#### LIU Load Index Upper Op. Code 52

Replaces the contents of the designated index register with the upper address portion of storage location 'm'. If b=0 this instruction becomes a pass (donothing) instruction.

#### LIL Load Index Lower Op. Code 53

Replaces the contents of the designated index register with the lower address portion of storage location 'm'. If b=0 this instruction becomes a pass (donothing) instruction.

#### SIU Store Index Upper Op. Code 56

Replaces the upper address portion of storage location 'm' with the contents of the designated index register. The remaining bits of the word in storage remain unchanged. If b=0,  $(m_{\text{tig}})$  is cleared.

#### SIL Store Index Lower Op. Code 57

Replaces the lower address portion of storage location 'm' with the contents of the designated index register. The remaining bits of the word in storage remain unchanged. If b = 0,  $(m_{lo})$  is cleared.

#### SAU Substitute Address Upper Op. Code 60

Replaces the upper portion of M with the lower order 15 bits of A. Remaining bits of M are not modified and the initial contents of A are unchanged.

#### SAL Substitute Address Lower Op. Code 61

Replaces the lower portion of M with the lower order 15 bits of A. Remaining bits of M are not modified and the initial contents of A are unchanged.

#### ENQ Enter Q Op. Code 04

The 15-bit operand, Y, is entered into Q and its highest order bit (sign bit) is extended in the re-

maining 33 bits. The largest positive 15-bit operand that can be entered into Q is 377778 ( $2^{14}$ -1) and its "0" sign bit will be duplicated in each of the remaining 33 bits of Q. Negative zero will be formed in Q if:

1)

$$(B^b) = 777778$$

and  $y = 777778$  or

2)

$$b = 0$$

and  $y = 777778$ .

#### ENA Enter A Op. Code 10

The 15-bit operand, Y, is entered into the A register and its highest order bit (sign bit) is extended in the remaining 33 bits. The largest positive 15-bit operand that can be entered into A is 377778 (2<sup>14</sup>-1) and the "0" sign bit will be duplicated in each of the remaining 33 bits. Negative zero will be formed in A if:

1)

$$(B^b) = 777778$$

and  $y = 777778$  or

2)

$$b = 0$$

and  $y = 777778$ .

#### ENI Enter Index Op. Code 50

Replaces  $(B^b)$  with the operand y. If b = 0, this instruction becomes a pass (do-nothing) instruction.

#### ATI Transmit A to Index

Transmits the lower 15 bits of A to the index register specified by b. The quantity designated by b may have values 1--6; (b=0, 7 is undefined and should not be used). The contents of the A register are not modified.

#### FIXED POINT ARITHMETIC

- 1) If the capacity of the A register,  $\pm (2^{47} 1)$ , is exceeded during the execution of the Fixed Point Arithmetic instructions (ADD, SUB, RAD, RSB, RAO, and RSO), an arithmetic overflow fault is produced. When executing the DVI instruction, if the result exceeds the capacity of the Q register,  $\pm (2^{47} 1)$ , a divide fault is produced (refer to appendix A).

- 2) The Multiply Integer instruction (MUI) uses the double register configuration QA. The least significant bit of the product is left in bit position A<sub>00</sub>. The most significant bit may be in either A or Q, depending upon the magnitude of the product.

#### ADD Add Op. Code 14

Adds a 48-bit operand obtained from storage location M to contents of A. A negative zero may be produced by this instruction if (A) and (M) are initially negative zero.

#### SUB Subtract Op. Code 15

Obtains a 48-bit operand from storage location M and subtracts it from the initial contents of A. A negative zero will be produced if the initial contents of A are negative zero and that of storage location M are positive zero.

#### MUI Multiply Integer Op. Code 24

Forms a 96-bit product from two 48-bit operands. The multiplier must be loaded into A prior to execution of the instruction. The execution address specifies the storage location of the multiplicand. The product is contained in QA as a 96-bit quantity. The operands are considered as integers and the binary point is assumed to be at the lower order (right-hand) end of the A register.

#### DVI Divide Integer Op. Code 25

Divides a 96-bit integer dividend by a 48-bit integer divisor. The 96-bit dividend must be formed in the QA register prior to executing the instruction. If a 48-bit dividend is loaded into A, the sign of Q must be set (the sign of the dividend in A must be extended throughout Q). The 48-bit divisor is read from the storage location specified by the execution address. The quotient is formed in A and the remainder is left in Q at the end of the operation. Dividend and remainder have the same sign.

# SINGLE PRECISION FLOATING POINT ARITHMETIC (Floating Point Option)

Floating Point range faults (overflow/underflow) occur if the exponent exceeds  $\pm$  (2<sup>10</sup> – 1).

#### FAD Floating Add (FPO) Op. Code 30

Forms the sum of two operands packed in floating point format. A floating point operand is read from storage location M and added to the floating point word in A. The result is normalized, rounded, and retained in A at the end of the operation. Q contains only the residue of the rounding operation at the end of the sequence.

#### FSB Floating Subtract (FPO) Op. Code 31

Forms the difference of two 48-bit operands in floating point format. The subtrahend is acquired from storage address M and is subtracted from the minuend in A. The result is rounded and normalized if necessary and retained in A. The residue from the rounding operation is left in Q at the end of the sequence.

#### FMU Floating Multiply (FPO) Op. Code 32

Forms the product of an operand in floating point format with the previous contents of A also in floating point format. The operand is read from storage location M. The product is rounded and normalized if necessary and retained in A. The residue from the rounding operation is left in Q at the end of the sequence.

#### FDV Floating Divide (FPO) Op. Code 33

Forms the quotient of two 48-bit operands in floating point format. The dividend must be loaded into A prior to executing this instruction. The divisor is read from the storage location specified by M. The quotient is rounded and normalized if necessary and retained in A at the end of the operation. The residue from the rounding operation is left in Q at the end of the operation.

#### **ADDRESS ARITHMETIC**

In the Address Arithmetic instructions, only the lower 15 bits of the operand or data words are used.

#### INA Increase A Op. Code 11

Adds Y to A. The 15-bit operand, Y, with its highest order bit (sign bit) extended, is added to A.

#### INI Increase Index Op. Code 51

Increases  $(B^b)$  by the operand 'y'. If the b designator is zero, this instruction becomes a pass or do nothing instruction.

#### ISK Index Skip Op. Code 54

Compares (B<sup>b</sup>) with 'y'. If the two quantities are equal, B<sup>b</sup> is cleared and the lower instruction is skipped. If the quantities are unequal, (B<sup>b</sup>) is increased by one. Counting in this instruction is performed in one's complement notation. (If (B<sup>b</sup>); = 777768 and  $y \neq 777768$ , then (B<sup>b</sup>); = 00000.) If b = 0, the (B<sup>b</sup>) are taken to be zero. ISK is usually restricted to the upper instruction. If used as a lower instruction, no skip is possible.

#### LOGICAL

The LDL, ADL, SBL and STL instructions achieve their result by forming a logical product. A logical product is a bit-by-bit multiplication of two binary numbers:

$$0 \times 0 = 0$$

$1 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 1 = 0$

2) A logical product is used, in many cases, to select specific portions of an operand for entry into another operation. For example, if only a specific portion of an operand in storage is to be added to (A), the operand is subjected to a mask composed of a predetermined pattern of "0's" and "1's". Forming the logical product of the operand and the mask causes the operand to retain its original contents only in those stages which have corresponding "1's" in the mask. When only the selected bits remain, the instruction proceeds to conclusion.

#### SST Selective Set Op. Code 40

Sets the individual bits of A to "1" where there are corresponding "1's" in the word at storage location M; "0" bits in the storage word do not modify the corresponding bits in A. In a bit-by-bit comparison of (A) and (M), four possible combinations of bits are possible.

1)

$$(A)_i = 1$$

2)  $(A)_i = 1$  3)  $(A)_i = 0$  4)  $(A)_i = 0$

$(M)_i = 1$   $(M)_i = 0$   $(M)_i = 1$   $(M)_i = 0$

$(A)_f = 1$   $(A)_f = 1$   $(A)_f = 1$   $(A)_f = 0$

$(M)_f = 1$   $(M)_f = 0$   $(M)_f = 1$   $(M)_f = 0$

#### SCM Selective Complement Op. Code 42

Individual bits of A are complemented where there are corresponding "1's" in the word at storage location M. If the corresponding bits at M are "0's", the associated bits of A remain unchanged.

1)

$$(A)_{i} = 1$$

2)  $(A)_{i} = 1$  3)  $(A)_{i} = 0$  4)  $(A)_{i} = 0$

$(M)_{i} = 1$   $(M)_{i} = 0$   $(M)_{i} = 1$   $(M)_{i} = 0$

$(A)_{f} = 0$   $(A)_{f} = 1$   $(A)_{f} = 1$   $(A)_{f} = 0$

$(M)_{f} = 1$   $(M)_{f} = 0$   $(M)_{f} = 1$   $(M)_{f} = 0$

#### SCL Selective Clear Op. Code 41

Clears individual bits of A where there are corresponding "1's" in the word at storage location M. If the corresponding bits at M are "0's" the associated bits of A remain unchanged.

In a bit-by-bit comparison of (A) and (M), four possible combinations of bits are possible.

1)

$$(A)_i = 1$$

2)  $(A)_i = 1$  3)  $(A)_i = 0$  4)  $(A)_i = 0$

$(M)_i = 1$   $(M)_i = 0$   $(M)_i = 1$   $(M)_i = 0$

$(A)_f = 0$   $(A)_f = 1$   $(A)_f = 0$   $(A)_f = 0$

$(M)_f = 1$   $(M)_f = 0$   $(M)_f = 1$   $(M)_f = 0$

#### SSU Selective Substitute Op. Code 43

Substitutes selected portions of an operand at storage address M into the A register where there are corresponding "1's" in the Q register (mask). The portions of A not masked by "1's" in Q are left unmodified.

#### LDL Load Logical Op. Code 44

Loads A with the logical product of Q and the designated storage location, M. The operand can be in either Q or M.

#### ADL Add Logical Op. Code 45

Adds to A the logical product of Q and the quantity in location M; the mask may be in Q or storage. Once the logical product is formed, addition follows normal rules.

#### SBL Subtract Logical Op. Code 46

Subtracts from A the logical product of the Q register and the quantity in storage location M. The mask may be in Q or storage. When the logical product is formed, the subtraction proceeds in the normal manner.

#### STL Store Logical Op. Code 47

Replaces the bits in location M with the logical product of Q and A registers. Neither (A) nor (Q) is modified. The mask may be located in A or Q.

#### SHIFTING

1) The largest practical shift count for a 48-bit register is 4810, for a 96-bit register, 9610. If a shift greater than 1778 = 12710 is attempted, the Shift Fault indicator will be set and the operand will be shifted according to the value of the lower 7 bits of K.

2) Shifts are not constant speed; that is, performing a shift of 4610 places, for example, takes longer than a shift of 1 place.

#### ARS A Right Shift Op. Code 01

Shifts contents of A to the right K places. The sign is extended and the lower bits are discarded. The largest practical shift count is 47<sub>10</sub> since the register is now an extension of the sign bit.

#### QRS Q Right Shift Op. Code 02

Shifts contents of Q to the right K places. The sign is extended and the lower bits are discarded. The largest practical shift count is 47<sub>10</sub> since the register is now an extension of the sign bit.

#### LRS Long Right Shift Op. Code 03

Shifts contents of AQ to the right K places as one 96-bit register. The A register is considered as the leftmost 48 bits and the Q register as the rightmost 48 bits. The sign of A is extended. The lower order bits of A replace the higher order bits of Q and the lower order bits of Q are discarded. The largest practical shift count is 95<sub>10</sub> since AQ is now an extension of the sign of A.

#### ALS A Left Shift Op. Code 05

Shifts contents of A to the left K places, left circular. The higher order bits of A replace the lower order bits. The largest practical shift count, 48<sub>10</sub>, returns the register to its original state.

#### QLS Q Left Shift Op. Code 06

Shifts contents of Q to the left K places, left circular. The higher order bits of Q replace the lower order bits. The largest practical shift count, 48<sub>10</sub>, returns the register to its original state.

### LLS Long Left Shift Op. Code 07

Shifts contents of AQ to the left K places, left circular, as one 96-bit register. The higher order bits of A replace the lower order bits of Q and the higher order bits of Q replace the lower order bits of A. The largest practical shift count, 96<sub>10</sub>, returns AQ to its original state.

#### **SCALE**

- Address modification does not apply. The index register is used to preserve the scale factor.

- If b = 0, scaling is executed but the scale factor is lost.

- If b = 7, indirect addressing is used and at least one storage reference is made.

- If (A) or (AQ)i is already scaled or equal to positive or negative zero, K→B<sup>b</sup>, and scaling is not executed.

- If the lower 7 bits of the shift count are initially equal to 0, k→ B<sup>b</sup>, and scaling is not executed.

- 6) The Shift Fault indicator is not affected by this instruction.

#### SCA Scale A Op. Code 34

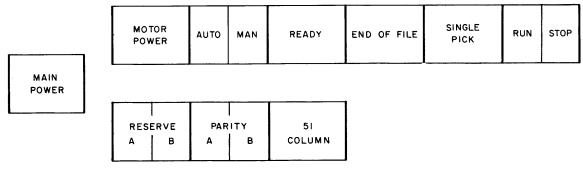

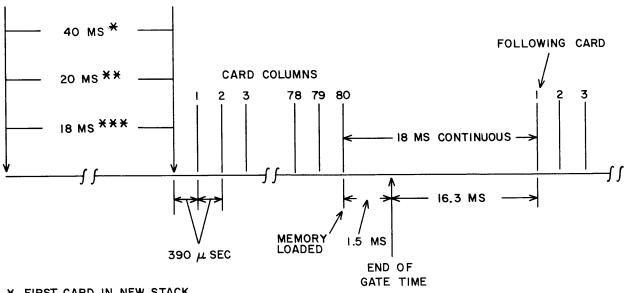

Shifts A left circularly until the most significant digit is to the right of the sign bit or until the lower 7 bits of k=0. (Maximum shift = 1778, although k may contain up to and including 777778.) The shift count (lower 7 bits of k) is reduced by one after each shift. The shift operation terminates when the lower 7 bits of k=0 or the most significant bit is to the right of the sign bit. Upon termination, bits 00 -- 14 of k are entered in the designated index register.