**Control Data**® 3400 Computer System Reference Manual

# INDEX TO INSTRUCTIONS (MNEMONIC CODES)

| Mnemonic                               | ·                                    |               | Mnemonic |                            |      |

|----------------------------------------|--------------------------------------|---------------|----------|----------------------------|------|

| Code                                   | Operation                            | Page          | Code     | Operation                  | Page |

| ************************************** |                                      | . <del></del> |          | -                          |      |

| ADD                                    | Add                                  | 3-11          | מומוו    | 11                         |      |

| ADL                                    | Add Logical                          | 3-14          | LIBJP    | Unconditional Jump         | 2 11 |

| AJP                                    | A Jump 3-17,                         |               | LIL      | Load Index (lower)         | 3-11 |

| ALS                                    | A Left Shift                         |               | LIU      | Load Index (upper)         | 3-10 |

| ARS                                    |                                      | 3-15          | LLS      | Long Left Shift (AQ)       | 3-15 |

| ATI                                    | A Right Shift<br>Transmit A to Index | 3-15          | LQC      | Load Q, Complement         | 3-10 |

| AUG                                    |                                      | 3-11          | LRS      | Long Right Shift (AQ)      | 3-15 |

| BEGR                                   | Augment<br>Read                      | 3-20          | MEQ      | Masked Equality Search     | 3-16 |

| BEGW                                   |                                      | 5-4           | MTH      | Masked Threshold Search    | 3-16 |

|                                        | Write                                | 5-4           | MUI      | Multiply Integer           | 3-12 |

| BJPL                                   | Unconditional Jump to Lower          |               | QJP      | Q Jump 3-17,               |      |

| BRTJ                                   | Unconditional Return Jump            | 3-19          | QLS      | Q Left Shift               | 3-15 |

| CCWD                                   | Change Control Word                  | 5-5           | QRS      | Q Right Shift              | 3-15 |

| CIS                                    | Copy Interrupt Status                | 4-14          | RAD      | Replace Add                | 3-15 |

| CLCH                                   | Clear Channel                        | 5-7           | RAO      | Replace Add One            | 3-15 |

| CMS                                    | Copy Mask Status                     | 4-15          | RSB      | Replace Subtract           | 3-15 |

| CONN                                   | Connect                              | 5-2           | RSO      | Replace Subtract One       | 3-16 |

| COPY                                   | Copy Status                          | 5-6           | SAL      | Substitute Address (Lower) | 3-11 |

| CPR                                    | Copy Product Register                | 4-15          | SAU      | Substitute Address (Upper) | 3-11 |

| DVI                                    | Divide Integer                       | 3-12          | SBL      | Subtract Logical           | 3-14 |

| ELB                                    | Enter Lower Bound                    | 3-22          | SCA      | Scale A                    | 3-15 |

| ENA                                    | Enter A                              | 3-11          | SCL      | Selective Clear            | 3-14 |

| ENI                                    | Enter Index                          | 3-11          | SCM      | Selective Complement       | 3-14 |

| ENQ                                    | Enter Q                              | 3-11          | SCQ      | Scale AQ                   | 3-15 |

| EQS                                    | Equality Search                      | 3-16          | SEN      | Internal Sense             | 3-14 |

| EUB                                    | Enter Upper Bound                    | 3-22          | SIL      | Store Index (Lower)        | 3-11 |

| EXTF                                   | Function                             | 5-3           | SIU      | Store Index (Upper)        | 3-11 |

| FAD                                    | Floating Add                         | 3-12          | SLJ      | Selective Jump 3-17,       | 3-19 |

| FDV                                    | Floating Divide                      | 3-13          | SLS      | Selective Stop 3-17,       | 3-19 |

| FMU                                    | Floating Multiply                    | 3-13          | SSH      | Storage Shift              | 3-16 |

| FSB                                    | Floating Subtract                    | 3-12          | SSK      | Storage Skip               | 3-16 |

| IAQ                                    | Interchange A & Q                    | 3-10          | SST      | Selective Set              | 3-14 |

| IJP                                    | Index Jump                           | 3-17          | SSU      | Selective Substitute       | 3-14 |

| INA                                    | Increase A                           | 3-13          | STA      | Store A                    | 3-10 |

| INF                                    | Internal Function                    | 4-11          | STCH     | Store Character            | 3-20 |

| INI                                    | Increase Index                       | 3-13          | STL      | Store Logical              | 3-14 |

| ISK                                    | Index Skip                           | 3-13          | STQ      | Store Q                    | 3-10 |

| LAC                                    | Load A, Complement                   | 3-10          | SUB      | Subtract                   | 3-11 |

| LDA                                    | Load A                               | 3-10          | THS      | Threshold Search           | 3-16 |

| LDCH                                   | Load Character                       | 3-20          | UBJP     | Unconditional Jump         | 3-19 |

| LDL                                    | Load Logical                         | 3-14          |          | ·                          | -    |

| LDQ                                    | Load Q                               | 3-10          |          |                            |      |

|                                        |                                      |               |          |                            |      |

|              |                    | RECORD                                | OF CHA   | ANGE NOTICES |

|--------------|--------------------|---------------------------------------|----------|--------------|

| C. N. NO.    | DATE<br>ORIGINATED | DATE<br>ENTERED                       | INITIALS | REMARKS      |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    | · · · · · · · · · · · · · · · · · · · |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              | ****               |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

| ·            |                    |                                       |          |              |

| <del> </del> |                    |                                       |          |              |

|              |                    |                                       |          |              |

|              | 1                  |                                       |          |              |

|              |                    |                                       |          |              |

|              |                    |                                       |          |              |

August, 1964 Pub. No. 60028200 Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

# **CONTENTS**

| Chapter I — Basic System Description        | 1      | Jumps and Stops                              | 3 - 17 |

|---------------------------------------------|--------|----------------------------------------------|--------|

| 3400 System Characteristics                 | 1-1    | Normal Jump                                  | 3 - 17 |

| Basic 3400 System                           | 1-2    | Return Jump                                  | 3 - 18 |

| Options                                     | 1-2    | Bank Jumps                                   | 3 - 19 |

| Chapter II — Storage Section                |        | Character Handling                           | 3 - 20 |

| Storage Word                                | 2-1    | Chapter IV — Interrupt System                |        |

| Storage Addressing                          | 2-1    | Logical Description of Interrupt System      | 4 - 1  |

| Chapter III — Computation Section           |        | Interrupt Register                           | 4-1    |

| Logical Description                         | 3-1    | Interrupt Mask Register                      | 4-1    |

| Arithmetic Section                          | 3-1    | Product Register                             | 4-1    |

| Control Section                             | 3-2    | Categories of Interrupts                     | 4-1    |

| Description of Instructions                 | 3-2    | Category I                                   | 4 - 2  |

| Class I                                     | 3-3    | Category II                                  | 4-2    |

| Class II                                    | 3-3    | Category III                                 | 4 - 3  |

| Class III                                   | 3-3    | Programming Cautions                         | 4-3    |

| Class IV Miscellaneous                      | 3-3    | Chapter V — Input/Output                     |        |

| Description of Designators                  | 3-4    | Input/Output Instructions                    | 5-2    |

| Address Modification                        | 3-4    | Control Word                                 | 5-5    |

| Address Modification Modes                  | 3-5    | Auto-Load                                    | 5-7    |

| Execution of Instructions                   | 3-5    | A010-E044                                    | 0.     |

| Symbols                                     | 3-6    | Chapter VI — Parity                          |        |

| Order of Instructions in Basic Computer     | 3-6    | Parity Generation                            | 6-1    |

| Instructions Added by Floating Point Option | 3 - 10 | Data Parity Generation                       | 6-1    |

| Inter-register Transmission                 | 3 - 10 | Parity Generation for 1/0 Channel            |        |

| Full-Word Transmission                      | 3 - 10 | Transmissions                                | 6-1    |

| Address Transmission                        | 3 - 10 | Parity Checking                              | 6-1    |

| Fixed Point Arithmetic                      | 3 - 11 | Parity Checking on Storage or                | . 1    |

| Single Precision Floating Point Arithmetic  | 3 - 12 | Transmission of Data                         | 6-1    |

| Address Arithmetic                          | 3 - 13 | Parity Checking on I/O Channel Transmissions | 6-2    |

| Logical                                     | 3 - 13 | Parity Errors                                | 6-2    |

| Shifting                                    | 3 - 14 | Operand Parity Error                         | 6-2    |

| Scale                                       | 3 - 15 | Instruction Parity Error                     | 6-2    |

| Replace                                     | 3 - 15 | 1/0 Channel Transmission Parity Error        | 6-2    |

| Storage Test                                | 3-16   | Interrupt Selection on I/O Parity Error      | 6-3    |

| Storage Search                              | 3 - 16 | External Equipment Parity Error              | 6-3    |

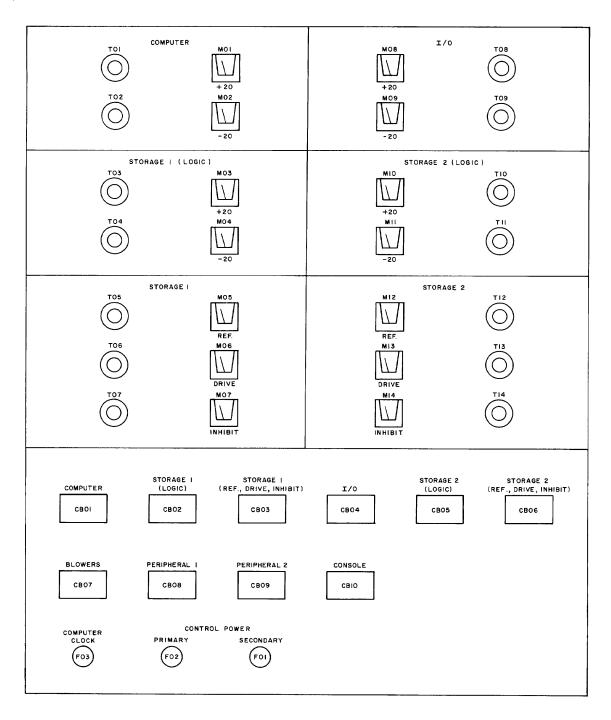

| Chapter VII - 3401 Consol      | le    | 3404 Maintenance Panel and Power   |            |  |

|--------------------------------|-------|------------------------------------|------------|--|

| Switches                       | 7-1   | Control Panel                      | 7-9        |  |

| Indicator s                    | 7 - 2 | System Status Display Panel        | 7 - 10     |  |

| Typewriter                     | 7-5   | Switches and Indicators            | 7 - 10     |  |

| Connect                        | 7-5   | Circuit Breakers                   | 7 - 17     |  |

| Function                       | 7-5   | Meters and Dials                   | 7 - 17     |  |

| Status                         | 7 - 5 |                                    |            |  |

| Programming                    | 7-7   | Glossary                           |            |  |

| Set Tabs, Margins, and Spacing | 7-7   | Appendices                         |            |  |

| Clear                          | 7-7   | A. Interruptible Conditions and Fa | ults       |  |

| Connect                        | 7-8   | B. Control Data 3400 Computer Ins  | tructions  |  |

| Check Status                   | 7-8   | C. Instruction Execution Times     |            |  |

| Function                       | 7-8   | D. Number Systems                  |            |  |

| Write                          | 7-8   | E. Table of Powers of 2            |            |  |

|                                | 7-8   | F. Octal-Decimal Conversion Tab    | le         |  |

| Read                           | 7-0   | G. Octal-Decimal Fraction Conver   | sion Table |  |

|       | FIGURES                     |        |       | TABLES                              |        |

|-------|-----------------------------|--------|-------|-------------------------------------|--------|

| 1 - 1 | 3400 Computer System        | 1-2    | 3-1   | Arithmetic Properties of Registers  | 3-1    |

| 3-1   | Return Jump                 | 3 - 18 | 4-1   | Assignment of Bits                  | 4-2    |

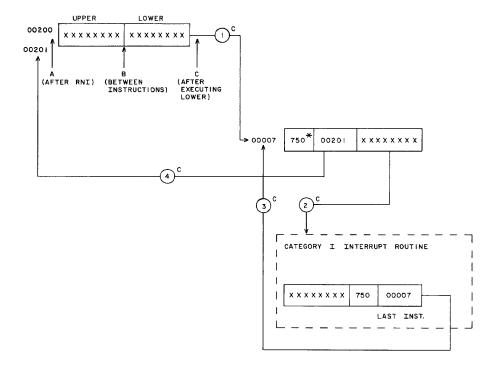

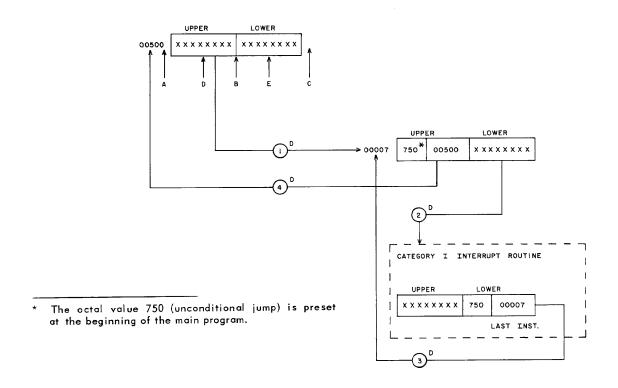

| 4-1   | Interrupt Example 1         | 4 - 4  | 4-2   | Interrupt Example 1                 | 4 - 5  |

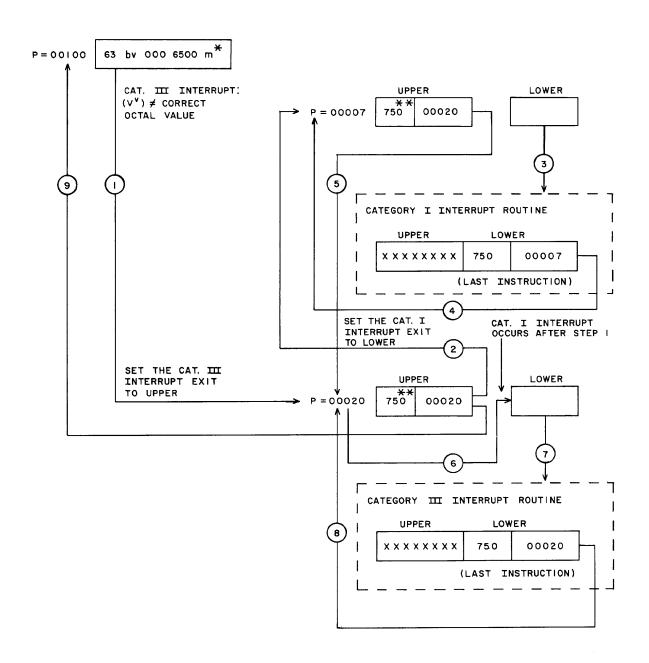

| 4-2   | Interrupt Example 2         | 4 - 6  | 4-3   | Interrupt Example 3                 | 4-7    |

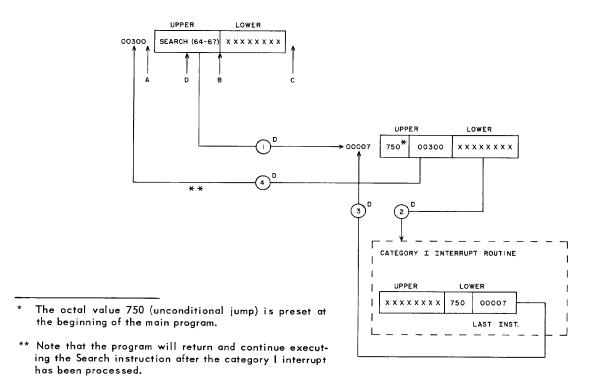

| 4-3   | Interrupt Example 3         | 4-7    | 4 - 4 | Interrupt Example 4                 | 4-9    |

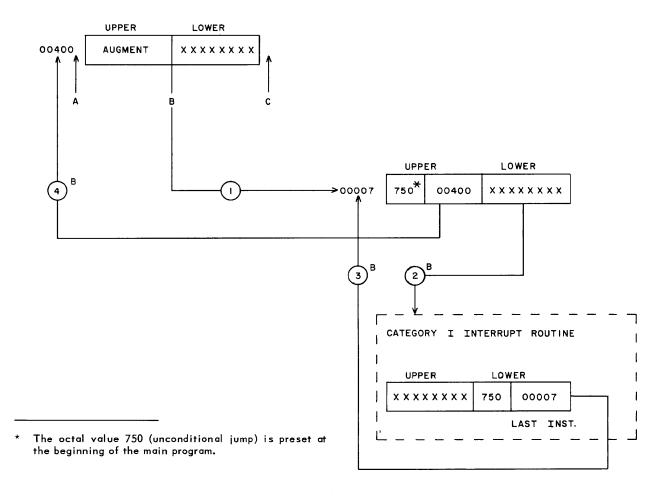

| 4-4   | Interrupt Example 4         | 4 - 8  | 4 - 5 | Interrupt Example 5                 | 4 - 10 |

| 4-5   | Interrupt Example 5         | 4-10   | 7 - 1 | Console Switches                    | 7-1    |

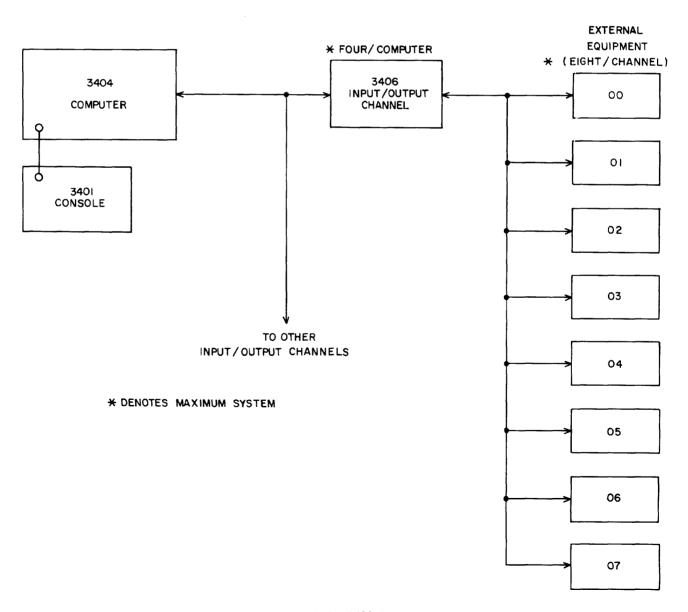

| 5-1   | 3400 System                 | 5-1    | 7-2   | Display Panel Indicators            | 7-3    |

| 7 - 1 | System Status Display Panel | 7 - 2  | 7-3   | 731 Typewriter Codes                | 7-6    |

| 7 - 2 | 3404 Maintenance Panel      | 7 - 9  | 7 - 4 | Connect, Function, and Status Codes | 7 - 7  |

| 7-3   | 3400 Power Control Panel    | 7 - 10 | 7 - 5 | 3404 Switches and Indicators        | 7 - 10 |

v

# CONTROL DATA® 3400 COMPUTER SYSTEM REFERENCE MANUAL

3400 COMPUTER

# **PREFACE**

This manual provides information for the machine-language use of the 3400 computer. Its intention is to describe the capabilities of the hardware. Options and constraints for programming are noted. Some programming examples are given to illustrate how instructions perform.

Other than using COMPASS mnemonics to abbreviate titles of instructions, no software systems are used in describing instructions.

# CHAPTER I BASIC SYSTEM DESCRIPTION

The CONTROL DATA\* 3400 is a solid-state, stored-program, general-purpose digital computing system, with large storage capacity and fast data transmission and computation speeds.

The 3400 system incorporates features of the CONTROL DATA 3600 Computer to provide program compatibility with this machine. With the several available options, a variety of configurations is possible.

#### 3400 SYSTEM CHARACTERISTICS

Stored-program, general-purpose computer

Parallel mode of operation

Single address logic

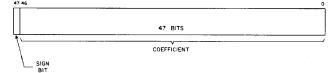

51-bit storage word (48 bits of data, 3 parity bits)

Six 15-bit index registers

Indirect addressing

Magnetic core storage

32,768 51-bit words 16,384 51-bit words

Input/Output

Transmission of 48-bit words (12-bit bytes)

Up to four separate bidirectional input/output channels

System interrupt

Flexible repertoire of instructions

Fixed point arithmetic (integer)

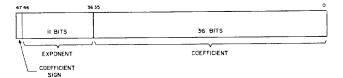

Single-precision, floating-point arithmetic (optional)

Logical and masking operations

Character handling instructions

Indexing

Storage searching

Binary arithmetic

Modulus 2<sup>48</sup> - 1 (one's complement) for single precision operations

Completely solid-state

Diode logic

Transistor amplifiers

Ready access to circuits

Console includes:

1/O Typewriter and display panel

Inter-computer communication

3400 -- 3400/3600/3800 Via 3682 Satellite 3400 -- 3100/3200/3300 Coupler

3400 -- 160/160-A }

Via 3682 Satellite and 3681 Data Channel Converter

<sup>\*</sup> Registered trademark of Control Data Corporation.

#### **BASIC 3400 SYSTEM**

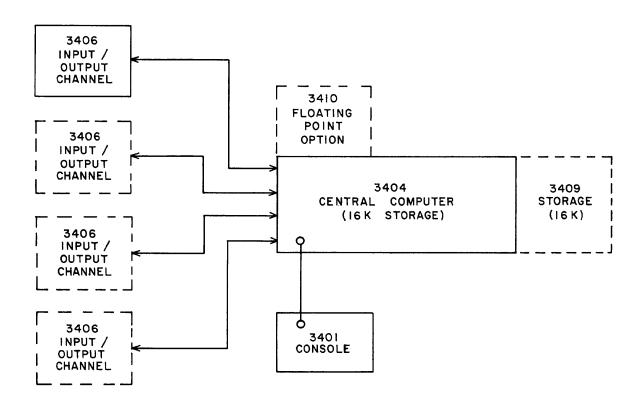

The basic 3400 system consists of a central computer, an input/output section, magnetic core storage, and a console. Over-all system operation depends on the integral operation of these elements. (See figure 1-1.)

Included in the basic computing system are operator and maintenance consoles. The consoles contain all the controls and indicators necessary to operate the system.

A set of basic programs is provided with the basic 3400 system consisting of an elemental assembler and operating system.

#### **OPTIONS**

For greater systems capability, the 3400 computing

system may be expanded with several available options. These options are:

#### 1) Floating point option (3410)

This adds four single-precision, floating-point instructions.

#### 2) 16,384 word storage

The standard 3400 system includes 32,768 words of core storage. An optional system is available with only 16,384 words of core storage. Standard programming systems for the 3400 require the use of the 3409 storage option; basic programs do not require the 3409.

#### 3) Additional Input/Output channels (3406)

The basic system may be expanded to a maximum of four bidirectional I/O channels.

Figure 1-1. 3400 Computer System (Dotted Lines Indicate Optional Additions)

# **CHAPTER II**STORAGE SECTION

The magnetic core storage section provides high-speed, random-access storage for 32,768 words. The storage section consists of the storage elements themselves, and the circuitry for addressing the storage elements.

#### STORAGE WORD

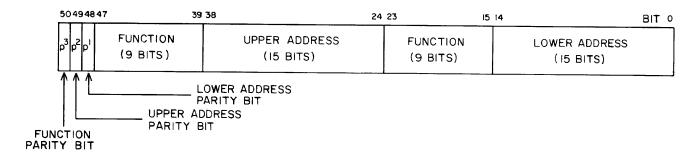

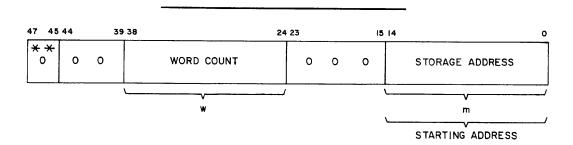

A storage word may be two 24-bit instructions, a single 48-bit instruction, or a 48-bit data word.

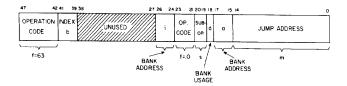

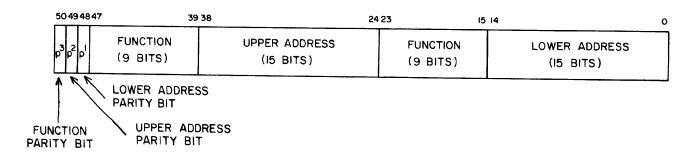

Three parity bits are appended to each 48-bit word; thus a storage word is 51 bits in length. The format of a typical storage word is diagrammed below.

The storage word is divided into three portions:

- 1) a 15-bit lower address.

- 2) a 15-bit upper address, and

- 3) an 18-bit function portion, distributed in the storage word as diagrammed. A parity bit accompanies each of these portions when the word is stored. The parity bit (P1) associated with the lower address portion is placed in bit 48 of the storage word, parity bit P2 (upper address) is placed in bit 49, and parity bit P3 (function) is placed in bit 50.

When part of the word or the entire 51 bits is read from storage, the appropriate parity bit(s) accompanies the word and the computer checks the word for parity.

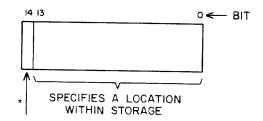

#### STORAGE ADDRESSING

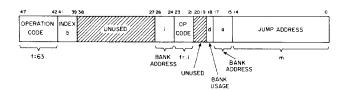

The location of each word in storage is identified by an assigned number (address). An address consists of 15 bits interpreted as shown below:

The following storage locations are used with return jump instructions for interrupt processing (unless the

<sup>\* 1)</sup> In a 3400 system with 32,768 words of core storage: If this bit is a "0", it specifies the lower section of storage which contains addresses 000008--377778; if this bit is a "1", it specifies the upper section of storage which contains addresses 400008--777778.

<sup>2)</sup> In a 3400 system with 16,384 words of core storage, this bit is always "0". It specifies the one storage section which contains addresses 000008--377778.

interrupt category is removed by adding an option):

00007 } Category | Interrupt

00030

00031 | Category | Interrupt

00032

00033 | Category | Il Interrupt

See Chapter 4 for additional information on the uses of these storage locations.

Address 000008 is reserved for use with a return jump instruction when the Restart switch is depressed. (See chapter 7.)

# **CHAPTER III**COMPUTATION SECTION

The computation section performs calculations and processes data in a parallel binary mode through the step-by-step execution of individual instructions. The instructions and data are stored in the storage section(s).

#### LOGICAL DESCRIPTION

The computation section may be functionally divided into an arithmetic section and a control section.

#### **Arithmetic Section**

The arithmetic section performs the arithmetic and logical operations necessary for executing instructions. It consists primarily of several operational registers. The operational registers are described below. Table 3-1 lists the arithmetic properties of the registers.

#### A Register

Nearly all arithmetic and logical operations use the 48-bit A register (Arithmetic register). The contents of this register may be shifted to the right or to the left, separately or in conjunction with the Q register. In certain conditional instructions, the A register is used to hold control quantities which govern operations.

#### Q Register

The 48-bit Q register (Auxiliary Arithmetic register) assists the A register in performing arithmetic and logical operations. The contents of the Q register may be shifted right or left, separately or in conjunction with the A register. Q may also be used with the A register to form a double length register, AQ or QA. In addition to assisting the A register, certain instructions reference the Q register directly.

#### P Register

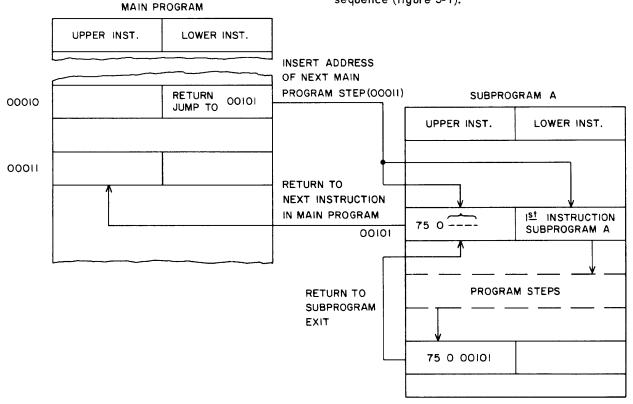

The 15-bit P register functions as a program address counter. The P register holds the address of each program step. After executing the instruction (or instructions) contained in the program step, the quantity in P is advanced by one to the address of the next instruction.

When a jump condition is met, the P register is set to the quantity specified by the execution address of

| Register        | No. of<br>Stages | Modulus            | Complement<br>Notation | Arithmetic    | Result   |

|-----------------|------------------|--------------------|------------------------|---------------|----------|

| A Register      | 48               | 2 <sup>48</sup> -1 | one's                  | su btracti ve | signed*  |

| Q Register      | 48               | 2 <sup>48</sup> -1 | on e's                 |               | signed   |

| P Register      | 15               | 2 <sup>15</sup>    | two's                  | additive      | unsigned |

| Index Registers | 15               | 2 <sup>15</sup> -1 | one's**                |               |          |

<sup>\*</sup> The result of an arithmetic operation in A satisfies A ≤ 2<sup>47</sup>-1 since A is always treated as a signed quantity. When the result in A is zero, it is always represented as 000...000 except when 111...111 is added to 111...111. In this case, the result is 111...111 (negative zero).

<sup>\*\*</sup>Though the index registers have no arithmetic capabilities themselves, address modification using the index registers is performed modulus 2<sup>15</sup>-1 (one's complement).

the jump instruction. If the instruction is a return jump, the contents of P are stored before executing the jump, permitting a return to the program sequence after the jump is made.

Since the P register is a two's complement additive register, it can generate storage addresses in sequence from 00000 to 777778. When a count of 777778 is reached, the next count in P reduces its value to 00000. (Note that in generating storage addresses by adding the contents of an index register to a base quantity, address 777778 usually cannot be reached. Refer to the section on Address Modification Modes, (p. 3-5).

#### **U** Register

The 48-bit Program Control register (U) holds the program step while it is being executed. All operations necessary to execute an instruction are governed by the contents of this register.

#### B<sup>1</sup> - B<sup>6</sup> (Index Registers)

Six 15-bit index registers may be used to:

- 1) Hold quantities used as address modifiers.

- 2) Hold control quantities for certain instructions.

The index registers may also be explicitly referenced by certain instructions (refer to Repertoire of Instructions section).

#### Interrupt Register

Each interruptible condition in the system is connected to a particular bit position of the Interrupt register. The lower bit positions detect internal interrupt conditions such as overflow, divide fault, and exponent fault. The upper bit positions are interrupt lines coming from each of the four possible communication channels.

#### Interrupt Mask Register

This register enables testing of external interrupt lines and internal conditions. The bit positions of this register match the Interrupt register. Interrupt occurs on a condition if the bit of the Mask register is set to "1". The Internal Function instruction may be used to set or clear bits in this register.

#### **Product Register**

The product register contains the bit-by-bit logical product of the Interrupt register and the Interrupt Mask register (refer to the Interrupt section).

#### Bounds Registers (Upper and Lower)

Two bounds registers serve as a memory and jump lock-out. The Lower bounds register holds an 8-bit Lower bound address. The Upper bounds register holds an 8-bit upper bound address. The upper 8 bits of the 15-bit storage address S are compared with the contents of the bounds registers when bounds checking is in effect.

#### **Control Section**

The control section of the computer directs the operations required to execute instructions and establishes the timing relationships needed to perform these operations in the proper sequence. It also sends the preliminary commands necessary to begin the processing of input/output data.

The control section acquires an instruction from storage, interprets it, and sends the necessary commands to other sections. A program step may be a single 48-bit instruction or a pair of 24-bit instructions which together occupy a single storage location as a 48-bit word.

The program address counter, P, is a two's complement additive register. It provides program continuity by generating in sequence the storage addresses which contain the individual program steps. Usually, at the completion of each program step, the count in P is advanced by one to specify the address of the next program step.

The Program Control register, U, holds a program step while it is being executed. If the program step is a pair of 24-bit instructions, the upper instruction is executed first, followed by the lower instruction.

#### DESCRIPTION OF INSTRUCTIONS

A computer word consists of 48 bits and may be interpreted as one 48-bit data word, a 48-bit instruction, or two 24-bit instructions.

Most instructions designated by three-letter mnemonic codes are 24-bit instructions common to the 1604 and 3600 computers. These instructions are arranged in a 48-bit word; the higher order 24 bits are called the upper instruction and the lower order 24 bits are called the lower instruction.

Instructions which are not common to the 1604 computer and designated by mnemonic codes of three or four letters, differ in format and in word length (some are 24 bits; others are 48 bits).

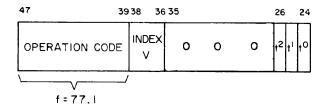

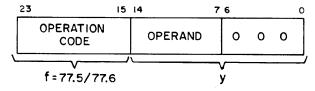

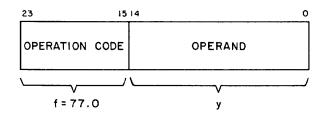

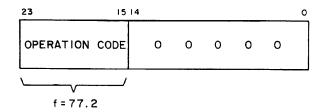

Instruction formats are arranged in four major classes, according to differences in word length and the position of the function code within the format. A typical format from each class is outlined below. Designators used within these formats are explained at the end of this section. For a comprehensive description of instructions, refer to the Repertoire of Instructions section.

#### Class I

Class I instruction formats are 24 bits in length and have 6-bit function codes, 'f'. All instructions common to the 1604 and 3600 computers and designated by three-letter mnemonic codes are included in this category.

| 23 | 18 | 17 15 14     |           | BIT o |

|----|----|--------------|-----------|-------|

|    | f  | b<br>or<br>j | m, y or k |       |

INSTRUCTIONS DESIGNATED BY THREE-LETTER MNEMONICS

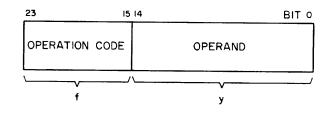

#### Class II

Class II instruction formats are 24 bits in length and have 9-bit function codes. All instructions in this category are designated by mnemonic codes of three letters.

#### Class III

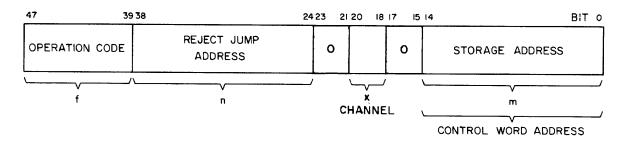

Class III instruction formats are 48 bits in length and have 9-bit function codes. All instructions in this category are designated by mnemonic codes of four letters.

#### Class IV Miscellaneous

See pages 3-20, 3-21, and 3-22.

#### DESCRIPTION OF DESIGNATORS

| Designators  | used    | throughou | t the   | Description | of  |

|--------------|---------|-----------|---------|-------------|-----|

| Instructions | section | and in i  | nstruct | ion formats | are |

explained below. For specific interpretations of designators, refer to the individual instructions.

| Designator |                              | <u>Use</u>                                                                                              |

|------------|------------------------------|---------------------------------------------------------------------------------------------------------|

| Ь          | Index                        | Specifies index register (B) used, or whose contents are used in the operation.                         |

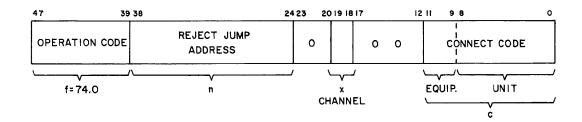

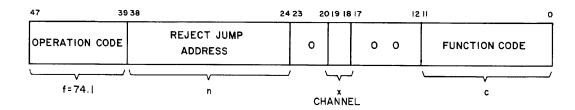

| c          | Connect and Function         | Specifies codes used in Connect and Function instructions.                                              |

| f          | Function Code                | A 6 or 9-bit code (depending on the operation) which specifies the operation to be performed.           |

| i          | Condi <b>t</b> ion           | Conditions operations in jumps and stops.                                                               |

| k          | Unmodified Shift Count       | Number of shifts to be executed.                                                                        |

| К          | Modified Shift Count         | $[K = k + (B^b)]$                                                                                       |

| m          | Unmodified Execution Address | Address of operand.                                                                                     |

| М          | Modified Execution Address   | $[M = m + (B^b)]$                                                                                       |

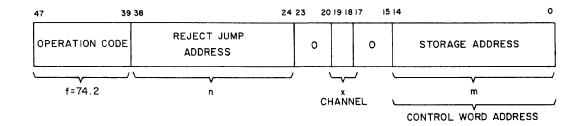

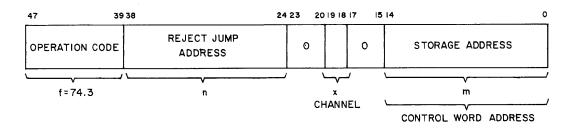

| n          | Reject Jump Address          | Used with I/O instructions.                                                                             |

| ٧          | Second Index                 | Specifies second index register (V) used, or whose contents are used in the operation.                  |

| w          | Word Count                   | A 15-bit quantity which specifies the number of words to be processed in a data transmission operation. |

| ×          | Channel Number               | Specifies 1/0 channel; also used to specify channel whose status will be read or sensed.                |

| у          | Unmodified Operand           | Used in execution address portion of instruction; specifies this address will be used as the operand.   |

| Υ          | Modified Operand             | $[Y = y + (B^b)]$                                                                                       |

#### ADDRESS MODIFICATION

The portion of the instruction word designated by 'm', 'y', or 'k', is often termed the base execution address. The base execution address may be used as (1) a shift count, 'k', (2) an operand, 'y', (3) an address of an operand, 'm', in storage. The execution address may be modified or left unmodified depending on the index designator. The execution address is modified by adding the contents of the designated index register to the execution address. If left unmodified, the lower-case symbols 'k', 'y', or 'm', are used. If the address is modified, the symbols are capitalized.

The modified shift count is represented by:

1)

$$K = k + (B^b)$$

where:

= modified shift count

= unmodified shift count (execution address)

$(B^b)$  = contents of index register b

If the index designator = 0, then K = k.

The modified operand is represented by:

2)

$$Y = y + (B^b)$$

where:

= modified operand

y = unmodified operand (execution address)  $(B^b)$  = contents of index register b

If the index designator = 0, then Y = y.

The modified operand address is represented by:

3)  $M = m + (B^b)$  where:

$(B^b)$  = contents of index register b If the index designator = 0, then M = m.

#### ADDRESS MODIFICATION MODES

Three possible modes of address modification, as determined by the index designator, are:

- b = 0 No address modification. The execution address is directly interpreted.

- b = 1-6 Relative address modification. The execution address is modified as outlined previously. One's complement arithmetic is used in determining the modified execution address.

#### NOTE

Since one's complement arithmetic is used in determining the relative address, address 777768 is the highest address which can be generated. Address 777778 cannot be reached by indexing. For example, modifying execution address 777768 by adding, in one's complement arithmetic, an index value of 1, results in 00000. During address modification, the modified address will equal 777778 only if: (1) the unmodified execution address equals 777778 and b=0, or (2) the unmodified execution address equals 777778 and  $(B^b)=777778$ .

3) b = 7 Indirect addressing. A storage reference is made to the location specified by the execution address. The lower order 18 bits of the word at this storage location are interpreted as the index

designator 'b' (3 bits) and execution address (15 bits) of the present instruction. The new index designator may refer to any one of the three modes.

#### **EXECUTION OF INSTRUCTIONS**

A program example and a step-by-step explanation of its execution is outlined below. Instructions from Class I are used in the example to help explain the use of various designators.

The storage reference is initiated at address 00300 (the address held in the P register). The 48-bit word is read from address 00300 and entered into U. Computer operation is now dependent upon the interpretation of the 24-bit instruction in the upper half of U.

The operation code, LDA, and the index designator, 0, are translated. The function of the LDA instruction is to load the A register with the contents of the designated storage location. Because the index designator is 0, the execution address is not modified. The translation of the operation code initiates the sequence of commands which executes the instruction, and the operand in address 00200 is loaded into A.

The lower instruction in U is translated. The ADD instruction causes the quantity in storage location M to be added to the contents of the A register. Since the index designator is not 0 or 7, the contents of the index register are added to the execution address to form M (M = m + (B $^{\rm b}$ ) = 00210g + 00100g = 00310g). The contents of storage address 00310 are added to the contents of the A register, completing the instruction. The contents of the P register are increased by one and the next program step at address 00301 is read from storage, entered into U, and translated.

#### Example:

Storage Address

f

b

m

f

b

m

00300

LDA

0

00200

ADD

1

00210

$(B^1) = 00100_8$

#### **SYMBOLS**

The following symbols are used in the Order of Instructions section.

| Α              | The A register                                                                                            |

|----------------|-----------------------------------------------------------------------------------------------------------|

| A <sub>n</sub> | The binary digit in position 'n' of the A register                                                        |

| Вр             | Designated index register                                                                                 |

| LA             | Lower address; execution address portion of lower instruction of a program step                           |

| Q              | Auxiliary Arithmetic register                                                                             |

| UA             | Upper address                                                                                             |

| ()             | Contents of a register or storage location                                                                |

| ()'            | One's complement contents of a register or storage location                                               |

| ( )f           | Final contents of a register or storage location                                                          |

| ( )i           | Initial contents of a register or storage location                                                        |

| #              | A flag to denote the instruction must be located in the upper instruction position of an instruction word |

| v              | The logical inclusive OR function                                                                         |

| <del>*</del>   | The logical exclusive OR function                                                                         |

| ^              | The logical AND function                                                                                  |

#### ORDER OF INSTRUCTIONS IN BASIC COMPUTER

| Octal<br>Code | Mnemonic<br>Code | Name                              | Indirect<br>Addressing | Storage *<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------|-----------------------------------|------------------------|-------------------------|-------------------------|----------------------------------|

|               | Inter-Regis      | ster Transmission                 |                        |                         |                         |                                  |

|               | IAQ              | Interchange A and Q<br>(00700554) | No                     | 0                       | No                      | 24                               |

|               | Full-Word        | Transmission                      |                        |                         |                         |                                  |

| 12            | LDA              | Load A                            | Yes                    | 1                       | Yes                     | 24                               |

| 16            | LDQ              | Load Q                            | Yes                    | 1                       | Yes                     | 24                               |

| 20            | STA              | Store A                           | Yes                    | 1                       | Yes                     | 24                               |

| 21            | STQ              | Store Q                           | Yes                    | 1                       | Yes                     | 24                               |

| 13            | LAC              | Load A, Complement                | Yes                    | 1                       | Yes                     | 24                               |

| 17            | LQC              | Load Q, Complement                | Yes                    | 1                       | Yes                     | 24                               |

<sup>\*</sup> If indirect addressing is designated, at least one additional storage reference is required.

# ORDER OF INSTRUCTIONS (Cont'd)

| Octal<br>Code | Mnemonic<br>Code       | Name                              | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|------------------------|-----------------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Address                | Fransmission                      |                        |                       |                         |                                  |

| 61            | SAL                    | Substitute Address<br>(lower)     | Yes                    | 1                     | Yes                     | 24                               |

| 60            | SAU                    | Substitute Address<br>(upper)     | Yes                    | 1                     | Yes                     | 24                               |

| 04            | ENQ                    | Enter Q                           | Yes                    | 0                     | Yes                     | 24                               |

| 10            | ENA                    | Enter A                           | Yes                    | 0                     | Yes                     | 24                               |

| 53            | LIL                    | Load Index (lower)                | Yes                    | 1                     | No                      | 24                               |

| 52            | LIU                    | Load Index (upper)                | Yes                    | 1                     | No                      | 24                               |

| 57            | SIL                    | Store Index (lower)               | Yes                    | 1                     | No                      | 24                               |

| 56            | SIU                    | Store Index (upper)               | Yes                    | 1                     | No                      | 24                               |

| 50            | ENI                    | Enter Index                       | Yes                    | 0                     | No                      | 24                               |

|               | ATI                    | Transmit A to Index<br>(0074054b) | No                     | 0                     | No                      | 24                               |

|               | Fixed Point Arithmetic |                                   |                        |                       |                         |                                  |

| 14            | ADD                    | Add                               | Yes                    | 1                     | Yes                     | 24                               |

| 15            | SUB                    | Subtract                          | Yes                    | 1                     | Yes                     | 24                               |

| 24            | MUI                    | Multiply Integer                  | Yes                    | 1                     | Yes                     | 24                               |

| 25            | DVI                    | Divide Integer                    | Yes                    | 1                     | Yes                     | 24                               |

|               | Address A              | Arithmetic                        |                        |                       |                         |                                  |

| 11            | INA                    | Increase A                        | Yes                    | 0                     | Yes                     | 24                               |

| 51            | INI                    | Increase Index                    | Yes                    | 0                     | No                      | 24                               |

| 54            | ISK                    | Index Skip                        | Yes                    | 0                     | No                      | 24                               |

|               | Logical                |                                   |                        |                       |                         |                                  |

| 40            | SST                    | Selective Set                     | Yes                    | ī                     | Yes                     | 24                               |

| 41            | SCL                    | Selective Clear                   | Yes                    | 1                     | Yes                     | 24                               |

| 42            | SCM                    | Selective Complement              | Yes                    | 1                     | Yes                     | 24                               |

| 43            | SSU                    | Selective Substitute              | Yes                    | 1                     | Yes                     | 24                               |

| 44            | LDL                    | Load Logical                      | Yes                    | 1                     | Yes                     | 24                               |

| 45            | ADL                    | Add Logical                       | Yes                    | 1                     | Yes                     | 24                               |

| 46            | SBL                    | Subtract Logical                  | Yes                    | 1                     | Yes                     | 24                               |

| 47            | STL                    | Store Logical                     | Yes                    | 1                     | Yes                     | 24                               |

# ORDER OF INSTRUCTIONS (Cont'd)

| Code    Sh   O1   A                                                                           | Anemonic Code  hifting ARS ARS ALS ALS ALS ALS ALS ALS ALS ALS ALS AL | —<br>Storage Skip                                                                                                                                                      | Indirect Addressing  Yes Yes Yes Yes Yes Yes Yes Yes Yes Ye | Storage References  0 0 0 0 0 0 0 0 2 2 2 2 2 | Address Modification  Yes Yes Yes Yes Yes No No Yes | Number of Instruction Bits  24 24 24 24 24 24 24 24 24 24 24 24 24 |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 01 Al 02 Qi 03 Li 05 Al 06 Qi 07 L 34 SG 35 SG 70 R 71 R 72 R 73 R 36 SG 37 SG 64 E 65 T 66 M | ARS ARS ALS ALS ALS ALS ALS ALS ALS ALS ALS AL                        | Q Right Shift Long Right Shift (AQ) A Left Shift Q Left Shift Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Subtract One St Storage Skip | Yes                     | 0<br>0<br>0<br>0<br>0<br>0<br>0               | Yes Yes Yes Yes Yes No No Yes Yes Yes Yes Yes                                           | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24           |

| 01 Al 02 Qi 03 Li 05 Al 06 Qi 07 L 34 SG 35 SG 70 R 71 R 72 R 73 R 36 SG 37 SG 64 E 65 T 66 M | ARS ARS ALS ALS ALS ALS ALS ALS ALS ALS ALS AL                        | Q Right Shift Long Right Shift (AQ) A Left Shift Q Left Shift Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Subtract One St Storage Skip | Yes                     | 0<br>0<br>0<br>0<br>0<br>0<br>0               | Yes Yes Yes Yes Yes No No Yes Yes Yes Yes Yes                                           | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24           |

| 02 Q1 03 L1 05 A1 06 Q1 07 L 34 S0 35 S0 70 R 71 R 72 R 73 R 36 S1 37 S1 64 E 65 T 66 M       | RS LRS LLS LLS GCA GCQ RAD RSB RAO RSO Gtorage Te                     | Q Right Shift Long Right Shift (AQ) A Left Shift Q Left Shift Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Subtract One St Storage Skip | Yes                     | 0<br>0<br>0<br>0<br>0<br>0                    | Yes Yes Yes Yes No No Yes Yes Yes Yes                                                   | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24           |

| 03                                                                                            | RS ALS ALS ALS ALS ALS ACA ACQ Replace RAD RSB RAO RSO Actorage Te    | Long Right Shift (AQ) A Left Shift Q Left Shift Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Subtract One Replace Subtract One          | Yes Yes Yes Yes Yes Yes Yes Yes Yes                         | 0<br>0<br>0<br>0<br>0                         | Yes Yes Yes No No Yes Yes Yes Yes Yes                                                   | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>24                 |

| 05 Al 06 Ql 07 L 34 SG 35 SG 70 R 71 R 72 R 73 R 36 SG 37 SG 64 E 65 T 66 M                   | ALS ALS ALS ALS ACA ACQ Replace RAD RSB RAO RSO Atorage Te            | A Left Shift Q Left Shift Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Add One Replace Subtract One                                     | Yes Yes Yes Yes Yes Yes Yes Yes Yes                         | 0<br>0<br>0<br>0                              | Yes Yes No No Yes Yes Yes Yes Yes                                                       | 24<br>24<br>24<br>24<br>24<br>24<br>24<br>24                       |

| 07 L 34 S0 35 S0 70 R 71 R 72 R 73 R 36 S3 37 S5 64 E 65 T 66 M                               | LLS SCA SCQ Replace RAD RSB RAO RSO Storage Te                        | Long Left Shift (AQ) Scale A Scale AQ  Replace Add Replace Subtract Replace Add One Replace Subtract One                                                               | Yes Yes Yes Yes Yes Yes Yes                                 | 0<br>0<br>0<br>2<br>2<br>2<br>2<br>2          | Yes No No Yes Yes Yes Yes Yes                                                           | 24<br>24<br>24<br>24<br>24<br>24<br>24                             |

| 34 SG 35 SG 70 R 71 R 72 R 73 R 36 SG 37 SG 64 E 65 T 66 M                                    | SCA SCQ Replace RAD RSB RAO RSO Storage Te                            | Scale A Scale AQ  Replace Add Replace Subtract Replace Add One Replace Subtract One  St Storage Skip                                                                   | Yes Yes Yes Yes Yes Yes                                     | 0<br>0<br>2<br>2<br>2<br>2<br>2               | No<br>No<br>Yes<br>Yes<br>Yes<br>Yes                                                    | 24<br>24<br>24<br>24<br>24<br>24                                   |

| 35 SO                                                     | SCQ Replace RAD RSB RAO RSO Storage Te                                | Scale AQ  Replace Add Replace Subtract Replace Add One Replace Subtract One  st Storage Skip                                                                           | Yes Yes Yes Yes Yes Yes                                     | 2<br>2<br>2<br>2<br>2                         | Yes<br>Yes<br>Yes<br>Yes                                                                | 24<br>24<br>24<br>24<br>24<br>24                                   |

| 70 R 71 R 72 R 73 R 36 Si 37 Si 64 E 65 T 66 M                                                | Replace<br>RAD<br>RSB<br>RAO<br>RSO<br>Storage Te                     | Replace Add Replace Subtract Replace Add One Replace Subtract One  st Storage Skip                                                                                     | Yes<br>Yes<br>Yes<br>Yes                                    | 2<br>2<br>2<br>2                              | Yes<br>Yes<br>Yes<br>Yes                                                                | 24<br>24<br>24<br>24<br>24                                         |

| 70 R 71 R 72 R 73 R 36 Si 37 Si 64 E 65 T 66 M                                                | RAD<br>RSB<br>RAO<br>RSO<br>Storage Te                                | Replace Subtract Replace Add One Replace Subtract One  st Storage Skip                                                                                                 | Yes<br>Yes<br>Yes                                           | 2 2 2                                         | Yes<br>Yes<br>Yes                                                                       | 24<br>24<br>24                                                     |

| 70 R 71 R 72 R 73 R 36 Si 37 Si 64 E 65 T 66 M                                                | RAD<br>RSB<br>RAO<br>RSO<br>Storage Te                                | Replace Subtract Replace Add One Replace Subtract One  st Storage Skip                                                                                                 | Yes<br>Yes<br>Yes                                           | 2 2 2                                         | Yes<br>Yes<br>Yes                                                                       | 24<br>24<br>24                                                     |

| 72 R 73 R  36 Si 37 Si  64 E 65 T 66 M                                                        | RAO<br>RSO<br>Storage Te<br>SSK                                       | Replace Add One Replace Subtract One  st Storage Skip                                                                                                                  | Yes<br>Yes                                                  | 2 2                                           | Yes<br>Yes                                                                              | 24<br>24                                                           |

| 72 R 73 R  36 S: 37 S: 64 E 65 T 66 M                                                         | RAO<br>RSO<br>Storage Te<br>SSK                                       | Replace Subtract One st Storage Skip                                                                                                                                   | Yes                                                         | 2                                             | Yes                                                                                     | 24                                                                 |

| 36 Si<br>37 Si<br>64 E<br>65 T<br>66 M                                                        | Storage Te                                                            | Replace Subtract One st Storage Skip                                                                                                                                   |                                                             |                                               |                                                                                         |                                                                    |

| 36 Si<br>37 Si<br>64 E<br>65 T<br>66 M                                                        | SSK                                                                   | —<br>Storage Skip                                                                                                                                                      | Yes                                                         | 1                                             | Yes                                                                                     | 24                                                                 |

| 36 Si<br>37 Si<br>64 E<br>65 T<br>66 M                                                        | SSK                                                                   | —<br>Storage Skip                                                                                                                                                      | Yes                                                         | 1                                             | Yes                                                                                     | 24                                                                 |

| 37 S. S. S. 64 E. 65 T. 66 M                                                                  |                                                                       |                                                                                                                                                                        | 1                                                           |                                               |                                                                                         | 1                                                                  |

| 64 E<br>65 T<br>66 M                                                                          | SSH                                                                   | Storage Shift                                                                                                                                                          | Yes                                                         | 2                                             | Yes                                                                                     | 24                                                                 |

| 64 E<br>65 T<br>66 M                                                                          | Search                                                                |                                                                                                                                                                        |                                                             |                                               |                                                                                         |                                                                    |

| 65 T<br>66 M                                                                                  | EQS                                                                   | Equality Search                                                                                                                                                        | Yes                                                         | N                                             | Yes                                                                                     | 24                                                                 |

| 66 M                                                                                          | THS                                                                   | Threshold Search                                                                                                                                                       | Yes                                                         | N                                             | Yes                                                                                     | 24                                                                 |

| 67 M                                                                                          | MEQ                                                                   | Masked Equality<br>Search                                                                                                                                              | Yes                                                         | N                                             | Yes                                                                                     | 24                                                                 |

|                                                                                               | мтн                                                                   | Masked Threshold<br>Search                                                                                                                                             | Yes                                                         | N                                             | Yes                                                                                     | 24                                                                 |

| J                                                                                             | Jumps and Stops                                                       |                                                                                                                                                                        |                                                             |                                               |                                                                                         |                                                                    |

|                                                                                               | AJP                                                                   | A Jump                                                                                                                                                                 | No                                                          | 1*                                            | No                                                                                      | 24                                                                 |

| 1                                                                                             | QJP                                                                   | Q Jump                                                                                                                                                                 | No                                                          | 1*                                            | No                                                                                      | 24                                                                 |

|                                                                                               | IJP                                                                   | Index Jump                                                                                                                                                             | Yes                                                         | 0                                             | No                                                                                      | 24                                                                 |

|                                                                                               | SLJ                                                                   | Selective Jump                                                                                                                                                         | No                                                          | 1*                                            | No                                                                                      | 24                                                                 |

|                                                                                               | SLS                                                                   | Selective Stop                                                                                                                                                         | No                                                          | 1*                                            | No                                                                                      | 24                                                                 |

|                                                                                               | UBJP<br>BRTJ                                                          | Unconditional Jump<br>Unconditional Return                                                                                                                             | Yes                                                         | 0                                             | Yes                                                                                     | 48                                                                 |

| 63.1 E                                                                                        |                                                                       | Jump<br>Unconditional Jump                                                                                                                                             | Yes<br>Yes                                                  | 0                                             | Yes<br>Yes                                                                              | 48                                                                 |

<sup>\*</sup> Return jump only

## ORDER OF INSTRUCTIONS (Cont'd)

| Octal<br>Code                                        | Mn emonio<br>Code | Name                               | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|------------------------------------------------------|-------------------|------------------------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|                                                      | Input/Output      |                                    |                        |                       |                         |                                  |

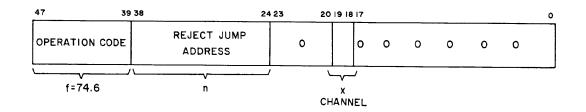

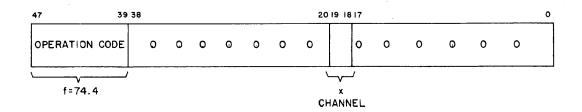

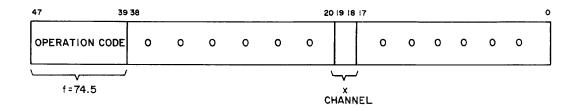

| 74.0                                                 | CONN              | Connect                            | No                     | 0                     | No                      | 48                               |

| 74.1                                                 | EXTF              | Function                           | No                     | 0                     | No                      | 48                               |

| 74.2                                                 | BEGR              | Read                               | No                     | 1                     | No                      | 48                               |

| 74.3                                                 | BEGW              | Write                              | No                     | 1                     | No                      | 48                               |

| 74.4                                                 | COPY              | Copy Status                        | No                     | 0                     | No                      | 48                               |

| 74.5                                                 | CLCH              | Clear Channel                      | No                     | 0                     | No                      | 48                               |

| 74.6                                                 | CCWD              | Change Control Word                | No                     | 0                     | No                      | 48                               |

| 77.2                                                 | CIS               | Copy Interrupt Status              | No .                   | 0                     | No                      | 24                               |

| 77.2                                                 | CMS               | Copy Mask Status                   | No                     | 0                     | No                      | 24                               |

| 77.3                                                 | SEN               | Internal Sense                     | No                     | 0                     | No                      | 24                               |

| 77.4                                                 | CPR               | Copy Product Register              | No                     | 0                     | No                      | 24                               |

| 77.0                                                 | INF               | Internal Function                  | No                     | 0                     | No                      | 24                               |

|                                                      | Miscellaneous     |                                    |                        |                       |                         |                                  |

| 77.1                                                 | AUG               | Augment                            | Yes                    | О                     | No                      | 24                               |

| 77.5                                                 | EUB               | Enter Upper Bound                  | No                     | О                     | No                      | 24                               |

| 77.6                                                 | ELB               | Enter Lower Bound                  | No                     | 0                     | No                      | 24                               |

|                                                      | LDCH              | Load Character<br>(63bv 0006500m)  | Yes                    | 1                     | Yes                     | 48                               |

|                                                      | STCH              | Store Character<br>(63bv 0006505m) | Yes                    | 2                     | Yes                     | 48                               |

|                                                      | Illegal Co        | de s                               |                        |                       |                         |                                  |

| 00* 26 27 62 63* 74.0* → 74.7 77.0* 77.5* 77.6* 77.7 | 74.6* Retu        | rn Jump to Address<br>00020        |                        |                       |                         |                                  |

<sup>\*</sup> See instruction description

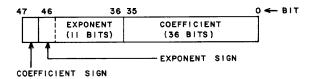

#### INSTRUCTIONS ADDED BY FLOATING POINT OPTION

| Octal<br>Code | Mnemonic<br>Code                           | Name              | Indirect<br>Addressing | Storage<br>References | Address<br>Modification | Number of<br>Instruction<br>Bits |

|---------------|--------------------------------------------|-------------------|------------------------|-----------------------|-------------------------|----------------------------------|

|               | Single Precision Floating Point Arithmetic |                   |                        |                       |                         |                                  |

| 30            | FAD                                        | Floating Add      | Yes                    | 1                     | Yes                     | 24                               |

| 31            | FSB                                        | Floating Subtract | Yes                    | 1                     | Yes                     | 24                               |

| 32            | FMU                                        | Floating Multiply | Yes                    | 1                     | Yes                     | 24                               |

| 33            | FDV                                        | Floating Divide   | Yes                    | 1                     | Yes                     | 24                               |

# INTER-REGISTER TRANSMISSION IAQ Interchange A and Q

The 24-bit Interchange A and Q instruction interchanges the contents of the A and Q registers. The 00 instruction is illegal if bits  $00 \rightarrow 17$  contain other than the exact code shown (with the exception of the transmit A to Index instruction).

#### **FULL-WORD TRANSMISSION**

In Full-Word Transmission instructions, a 48-bit operand or data word is used in executing the instruction.

### LDA Load A Op. Code 12

Replaces the contents of A with a 48-bit operand contained in the storage location specified by M. Negative zero is formed in A if the operand at M is equal to negative zero.

# LAC Load A Complement Op. Code 13

Replaces the contents of A with the complement of a 48-bit operand contained in the storage location specified by M. Negative zero is formed in A if the operand at M is equal to positive zero.

# LDQ Load Q Op. Code 16

Replaces the contents of Q with a 48-bit operand contained in the storage location specified by M. Negative zero is formed in Q if the operand at M is equal to negative zero.

# LQC Load Q Complement Op. Code 17

Replaces the contents of Q with the complement of a 48-bit operand contained in the storage location specified by M. Negative zero is formed in Q if the operand at M is equal to positive zero.

#### STA Store A Op. Code 20

Replaces the contents of the designated storage location, M, with the contents of A.

# STQ Store Q Op. Code 21

Replaces the contents of the designated storage location, M, with the contents of Q.

#### ADDRESS TRANSMISSION

- In the Address Transmission instructions, only the lower 15 bits of a 24-bit word instruction or data word are used.

- 2) In the LIU and LIL instructions, an index designation of "O" has no meaning and should not be used. If used, these instructions become pass instructions, but use some time in storage reference. The next instruction is then executed. Using "O" as an index designation does not constitute a fault.

# LIU Load Index Upper Op. Code 52