# 6600 CENTRAL PROCESSOR

Volume I

CONTROL & MEMORY

#### 6600 CENTRAL PROCESSOR

Volume I

Control and Memory

# FOR TRAINING PURPOSES ONLY

This book was compiled and written by members of the instructional staff of

CONTROL DATA INSTITUTE CONTROL DATA CORPORATION

Publication No. 020167

March, 1967

# CONTENTS

| CHAPTER | Ι    | COI  | NCE  | PT   | OF   | T.  | HE  | 6   | 60  | 0   | CE: | NT. | RA  | L   | PR  | OC: | ES | SO | R |   |   |   |   |   |   |   |   |              |

|---------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|---|---|---|---|---|---|---|---|---|--------------|

| Int     | trod | luc  | tio  | n.   | •    | •   | •   | •   | •   | •   |     | •   | •   | •   |     | •   | •  | •  | • | • | • | • | • | • |   | • | • | 1-1          |

| B10     | ock  | Dia  | agr  | am   | Ana  | al: | ys: | is  | •   | •   | •   | •   | •   | •   | •   | •   | •  | •  | • | • | • | • | • | • | • | • | • | 1-6          |

| Cer     | ntra | ı1 1 | 1em  | ory  | 7 •  |     | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | •  |   | • | • |   | • | • | • | • | ٠ | 1-13         |

| Ins     | stru | ıct: | ion  | Со   | nti  | rol | L.  | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | •  | • |   | • | • | • | • | • |   |   | 1-16         |

| Res     | serv | at:  | ion  | Со   | nt   | rol | l . |     | •   | •   | •   |     |     | •   |     | •   |    |    |   |   |   | • | • | • | • | • | • | 1-24         |

| Reg     | 3ist | er   | Eχ   | it/  | 'Ent | try | 7 ( | Cor | ntı | co: | 1.  | •   | •   | •   | •   | •   | •  | •  | • | • | • | • | • | • | • | • | • | 1-30         |

| CHAPTER | II   | CI   | INT: | RAL  | , MI | EMC | R   | Z E | ADI | R   | ES  | s ( | COI | NT. | ROI | L   |    |    |   |   |   |   |   |   |   |   |   |              |

| Int     | rod  | luct | io   | n.   | •    |     |     |     | •   |     | •   | •   | •   |     | •   | •   |    | •  |   |   |   |   |   | • | • | • |   | 2-1          |

| Stu     | ınt  | Воз  | د L  | ogi  | c A  | Ana | 113 | /si | İs  | •   | •   |     | •   | •   | •   | •   | •  | •  | • |   | • | • | • | • | • |   |   | 2-3          |

| Exc     | han  | ge   | Ju   | mp.  |      | •   | •   |     |     |     | •   | •   | •   | •   |     | •   |    | •  |   | • |   |   |   |   | • |   |   | 2-13         |

| Per     | iph  | era  | ı1 I | Rea  | d/V  | √ri | .te | ٠.  | •   |     | •   | •   | •   |     |     | •   | •  | •  |   |   |   | • | • |   |   | • | • | 2-20         |

| Cer     | ıtra | 1 F  | ≀ea∙ | d/W  | rit  | e   |     | •   |     |     | •   | •   |     |     |     | •   | •  |    |   |   |   |   | • | • |   | • |   | 2-25         |

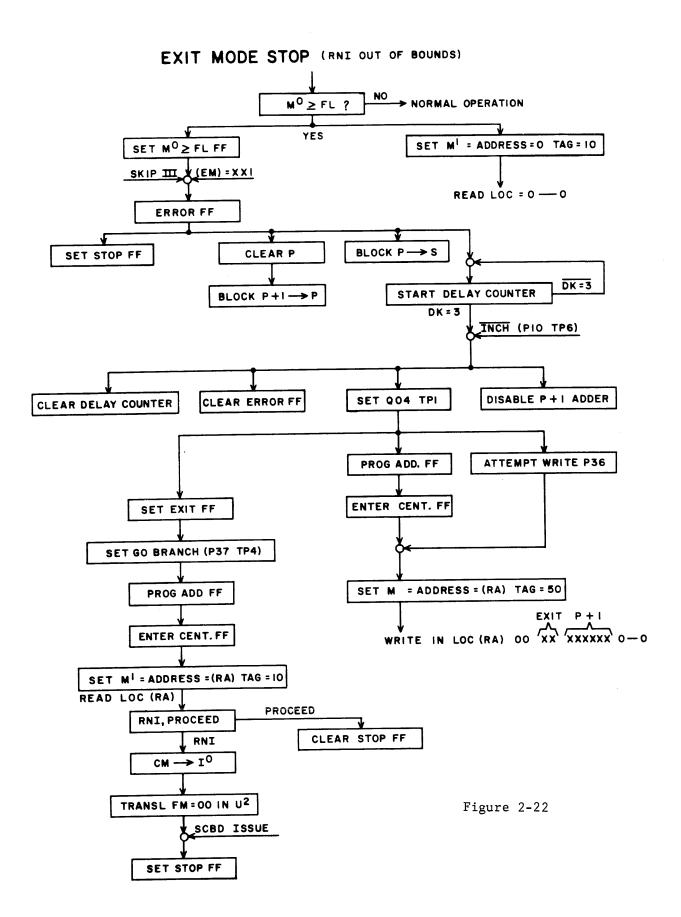

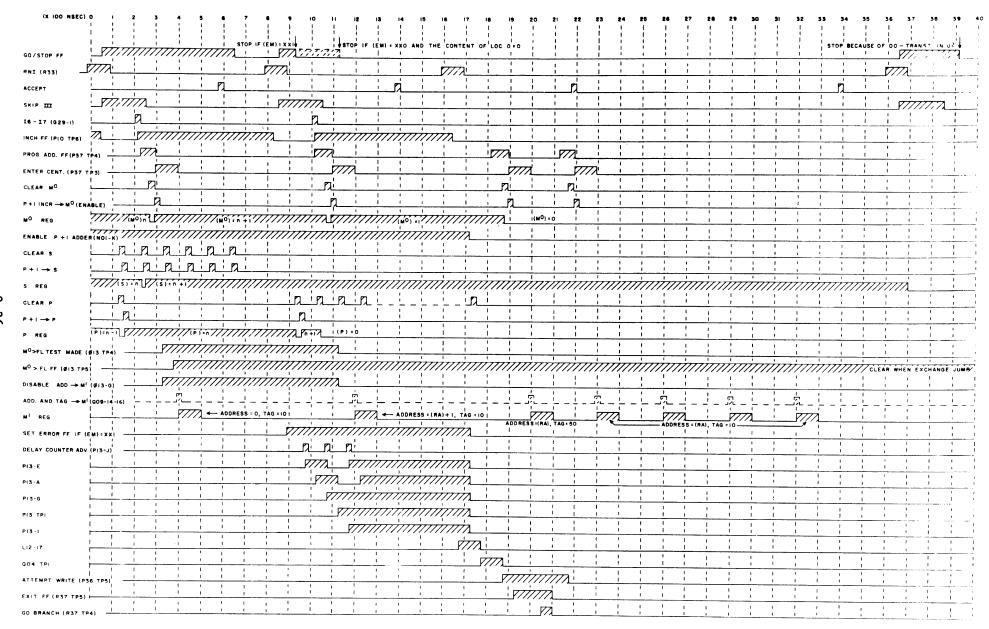

| Exi     | .t M | ode  | i    |      | •    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   |    |    | • | • | • | • | • | • | • | • | • | 2-29         |

| CHAPTER | III  | C    | EN:  | ΓRA  | LM   | 1EM | OR  | Υ   | CC  | N   | ۲RC | ΣL  |     |     |     |     |    |    |   |   |   |   |   |   |   |   |   |              |

| Int     | rod  | uct  | ior  | n .  | •    | •   | •   |     |     |     | •   |     |     |     |     | •   |    |    |   | • |   |   |   |   |   | • |   | 3-1          |

| Sto     | rag  | e S  | equ  | ıen  | ce   | Со  | nt  | ro  | 1   |     | •   | •   | •   | •   | •   | •   | •  |    |   |   |   |   |   |   |   |   |   | 3-6          |

|         | a D  |      |      |      |      |     |     |     |     |     |     |     |     |     |     |     |    |    |   |   |   |   |   |   |   |   |   | 3-10         |

| CHAPTER | IV   | IN   | STI  | RUC' | TIC  | N   | IS  | su  | Έ   | CC  | rno | RC  | L   |     |     |     |    |    |   |   |   |   |   |   |   |   |   |              |

| Int     | rodu | uct  | ior  | 1.   | •    |     |     |     |     |     |     |     | •   |     |     |     | •  |    | • | • |   |   |   | • |   |   |   | 4-1          |

| Ins     | tru  | cti  | on   | Sta  | ack  |     | •   |     |     |     |     |     | •   |     |     | •   |    |    |   |   |   |   | • |   | • |   |   | 4-1          |

| Ins     | truc | cti  | on   | Res  | gis  | te  | rs  |     |     |     |     |     |     |     |     | _   |    | _  |   |   |   |   |   |   |   |   |   | <i>1</i> . 5 |

| P                | arcel (        | Counter | •   | •    |     | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 4-11 |

|------------------|----------------|---------|-----|------|-----|----|----|-----|------|-----|----|------|-----|-----|---|---|---|---|---|---|---|---|---|---|------|

| I                | nch Cou        | inter . | •   | •    |     | •  | •  | •   |      | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • |   | • | 4-13 |

| I                | ssue Co        | ontrol. | •   | •    |     | •  | •  | •   | •    | •   | •  | •    | •   | •   |   | • |   | • | • | • | • | • |   |   | 4-19 |

| S                | top Ins        | structi | on  | Is   | sue | ٠. | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 4-19 |

| P                | roceed         | Instru  | cti | .on  | Ιs  | su | es | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 4-23 |

| СНАРТЕ           | R V R          | ESERVAT | ION | C    | TMC | RO | L  |     |      |     |    |      |     |     |   |   |   |   |   |   |   |   |   |   |      |

| I                | ntroduc        | tion .  | •   | •    |     | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • |   | • |   | • | • | 5-1  |

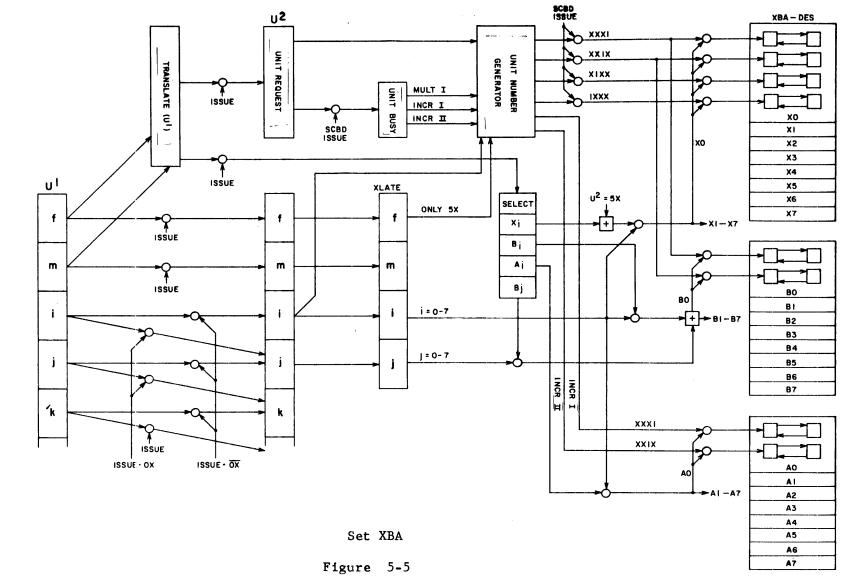

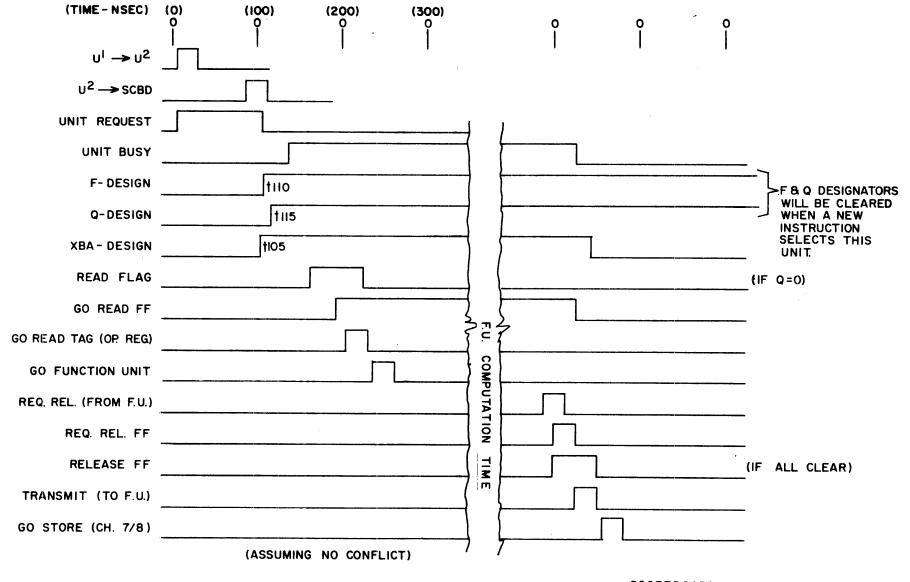

| P                | lacing         | Reserv  | ati | on:  | s . | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 5-3  |

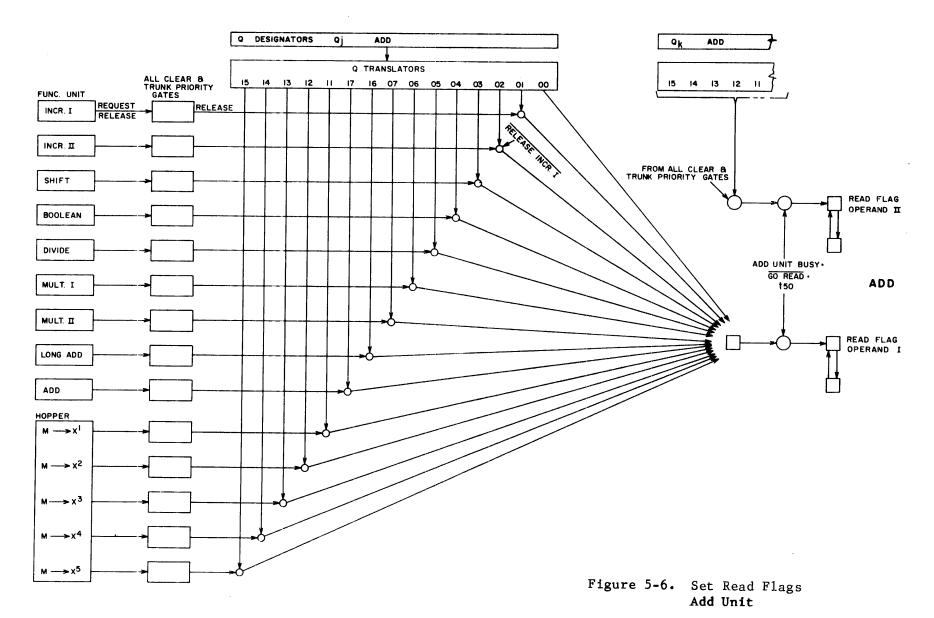

| S                | et Read        | l Flags | •   | •    |     | •  | •  | •   | •    | •   |    | •    | •   | •   | • | • | • | • | • | • | • |   | • | • | 5-10 |

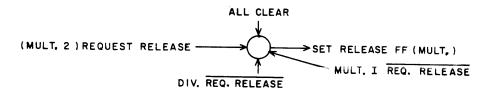

| R                | elease.        |         | •   | • (  |     | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 5-14 |

| СНАРТЕ           | R VI E         | ENTRY/E | ХII | CC   | NT  | RO | L  | ANI | ) [  | AC  | ſΑ | TF   | RUN | IKS | 3 |   |   |   |   |   |   |   |   |   |      |

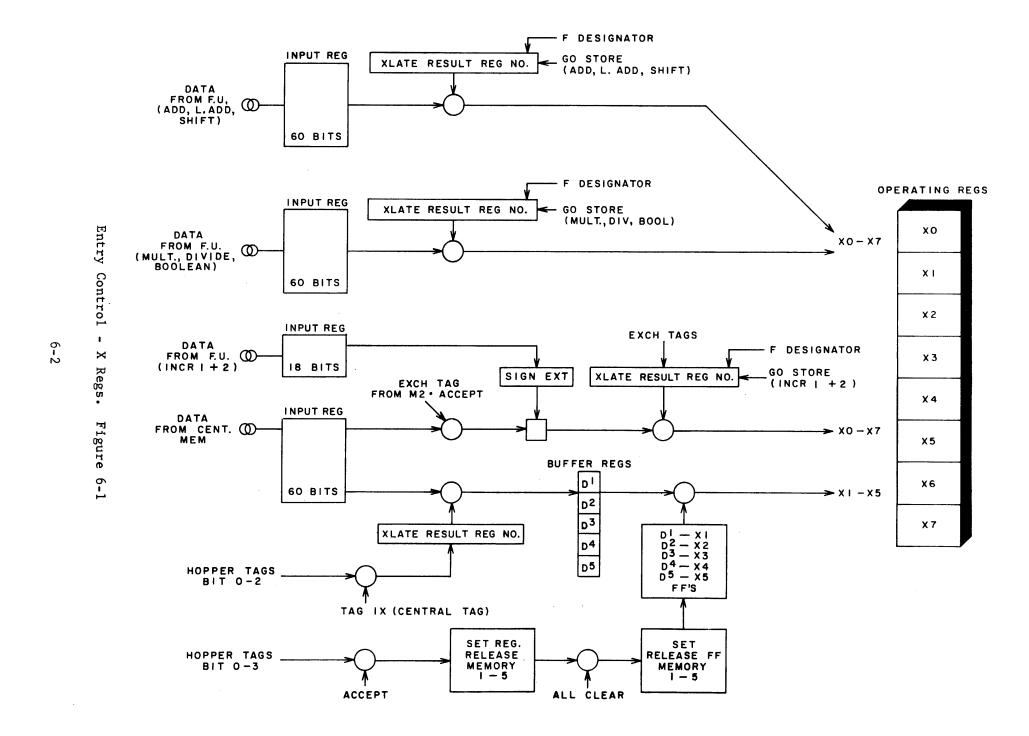

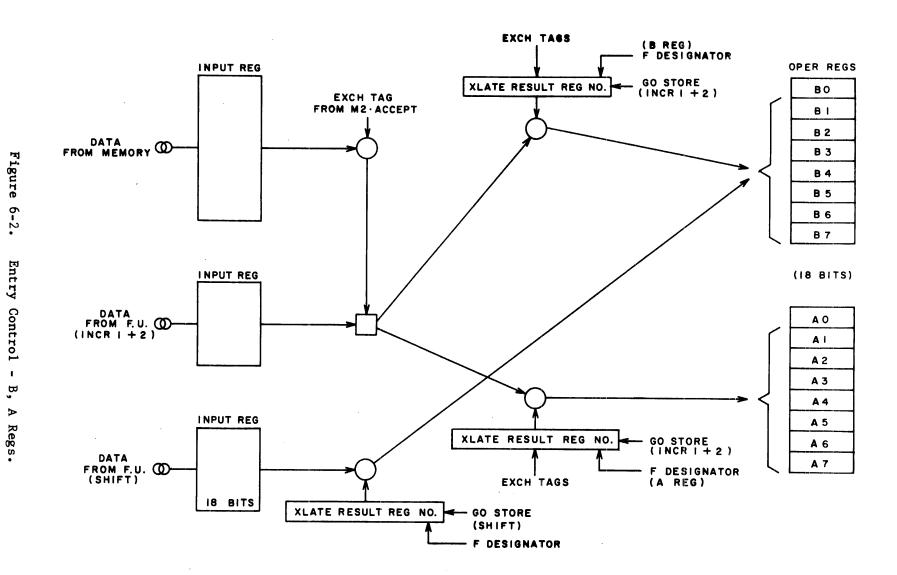

| E                | ntry Co        | ntrol.  | •   | •    |     | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 6-1  |

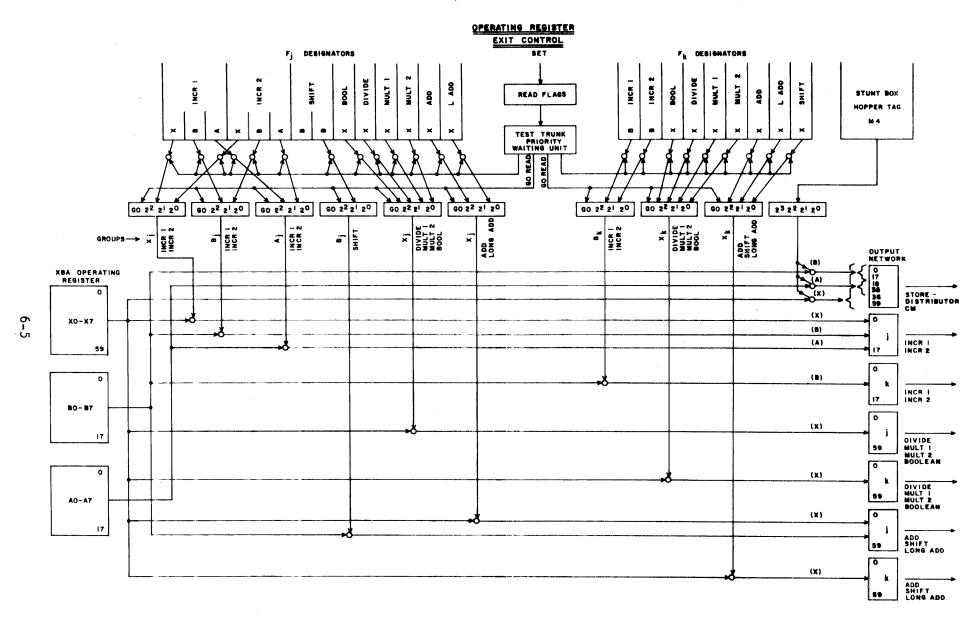

| E                | <b>xit</b> Cor | trol .  | •   | •    | •   | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • |   | • | • | 6-1  |

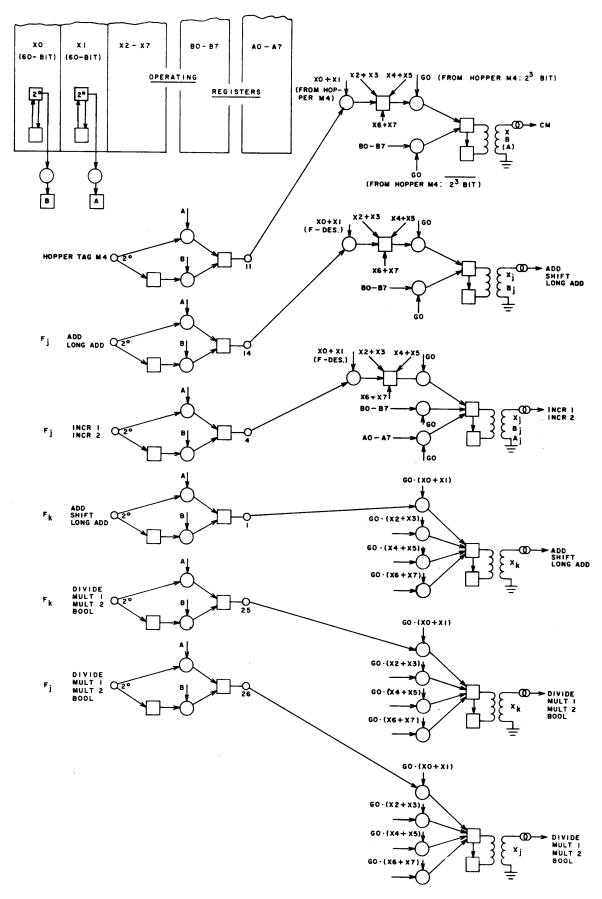

| D                | ata Tru        | ınks    | •   | •    |     | •  | •  | •   | •    | •   | •  | •    | •   | •   | • | • | • | • | • | • | • | • | • | • | 6-4  |

| APPEND           | IX A C         | ENTRAL  | PR  | OCI  | ESS | OR | T  | IM] | INC  | 3 1 | O  | TE S | 5   |     |   |   |   |   |   |   |   |   |   |   |      |

| <b>A DDENI</b> D | TYRN           | IONSTAN | DAR | ם מי | )PF | RΔ | ממ | FC  | ) RN | 1S  |    |      |     |     |   |   |   |   |   |   |   |   |   |   |      |

## CHAPTER I

CONCEPT OF THE 6600 CENTRAL PROCESSOR

#### CHAPTER I

### CONCEPT OF THE 6600 CENTRAL PROCESSOR

#### INTRODUCTION

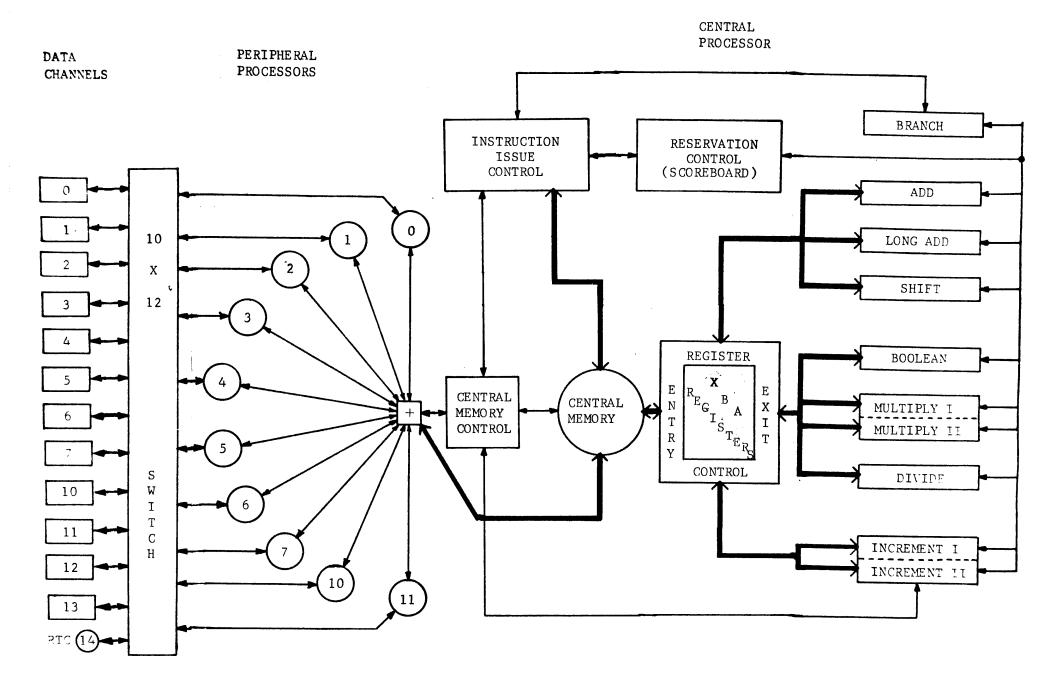

The CONTROL DATA® 6600 Computer System, through use of high-speed transistor logic and a design philosophy based on concurrent (or parallel) processing, is today recognized as the world's fastest and most powerful computer. The rapid throughput achieved by the 6600 system can be attributed in part to the concurrency that exists in several areas of the Central Processor.

#### MEMORY BANK PHASING '

The Central Memory is divided into memory banks, each of which contains 4096(10) 60-bit central processor words. A 131K central memory is composed of 32 such banks; a 65K memory has 16 banks. Since each bank has its own circuitry for the X & Y drive lines, inhibit lines, sense lines and memory cycle timing, each is capable of operating independently. This, in turn, permits memory cycles to be phased (overlapped) by 100 nanoseconds, to effectively reduce minimum access time to 100 nsec (e.g., a memory cycle is one microsecond in duration, but ten may be initiated each usec as long as they are to different banks). The bank phasing scheme, in addition to a memory cycle which is in itself extremely fast, eliminates a great portion of the memory waiting time that is inherent in the majority of computers.

#### INSTRUCTION STACK

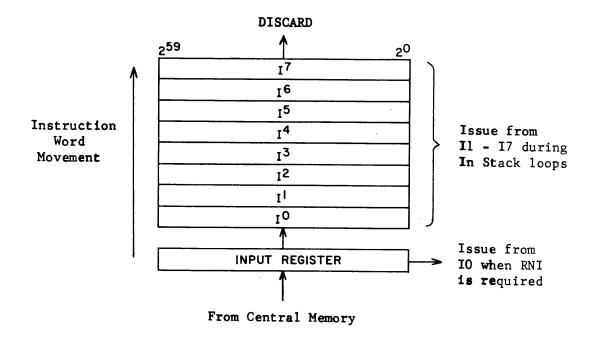

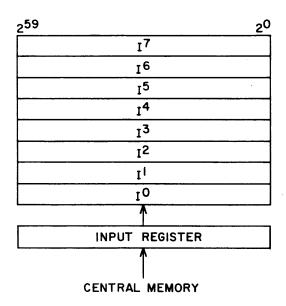

A group of flip-flop registers referred to as the Instruction Stack is provided in the 6600 for the purpose of holding an iterative sequence of instructions (a program loop). The Stack can hold a loop containing up to 27 instructions (up to 4 instructions per word) which may then be executed without the need for instruction word memory references (RNIs).\* Initially, the eight stack registers (I registers) are filled by reading instruction words from central memory. As each word is read into and executed from IO (See Figure 1-1), the preceding words move up in the stack and a new word is entered into the first I register. When the stack is filled, the movement of instruction words causes the top word (in

<sup>\*</sup> Although 27 instructions may at first appear to limit the programmer's capability, it should be considered that the 6600 is designed primarily as a scientific machine. Consequently, a good many programs will be of a mathematical nature (i.e., matrix analysis). Also, each instruction can designate two source operands and one result destination. When viewed in this light, 27 instructions are, in most cases, more than adequate.

<sup>&</sup>lt;sup>®</sup>Registered trademark of Control Data Corporation.

17) to be discarded. When instructions are being executed in the stack (looping), no movement occurs and the stack information remains static. In this manner, the necessity of fetching each instruction from memory is eliminated during short loops. The memory access time savings should be obvious.

Figure 1-1

#### Operating Registers

Another property of the Central Processor decreases the number of memory references required to read and store operands. Twenty-four operating registers provide a flip-flop storage facility for 60-bit operands and 18-bit addresses and indexing values. Eight 60-bit registers (designated XO - X7) provide for the storage of integer and floating point values in a 60-bit format. Eight 18-bit registers (designated AO - A7) provide storage for central memory addresses of operands which are read or stored in memory. Eight 18-bit registers (designated BO - B7) provide for storage of indexing values, used for modification of addresses and operands. Since most central processor instructions can designate two source operands (taken from X, B or A registers) and one result destination (X, B or A register), considerable operand manipulation can take place by use of the operating registers, thereby further decreasing the number of memory accesses needed. Proper use of the instruction stack and operating registers makes possible, execution of program loops which require no memory references -- for instructions, operands or storage of results.

#### Functional Units

Another area of concurrency in the 6600 Central Processor is that of parallel arithmetic (functional) units. Ten logically independent functional units are provided to allow several instructions to be in various stages of execution at the same time. The following list describes the functional units and their corresponding cycle times:

|     | UNIT                         | TIME (nanoseconds) |

|-----|------------------------------|--------------------|

| 1)  | ADD (floating)               | 400                |

| 2)  | MULTIPLY 1 (floating)        | 1000               |

| 3)  | MULTIPLY 2 (floating)        | 1000               |

| 4)  | DIVIDE (floating)            | 2900               |

| 5)  | BOOLEAN (logical)            | 300                |

| 6)  | LONG ADD (integer)           | 300                |

| 7)  | SHIFT                        | 300 - 400          |

| 8)  | INCREMENT 1 (indexing)       | 300                |

| 9)  | INCREMENT 2 (indexing)       | 300                |

| 10) | BRANCH (branch instructions) | 800 - 1400         |

Each unit is assigned a group of instructions which it, and only it, processes. For example, the ADD unit processes all single precision, double precision, rounded and unrounded floating point add opcodes. The SHIFT unit handles opcodes that require shifting: left and right shifts, normalize operations, packing, unpacking, etc.

Separate functional units eliminate the necessity for sequential execution of program steps, a property which is inherent in most present-day computers. Instead, unrelated instructions may be processed out of sequence, causing a considerable decrease in the over-all execution time of a program. Of course, if a source operand for one unit is the result operand of another, the first unit must wait until the second completes its calculation and returns the result. Also, if two division steps are needed in sequence, the second must wait until the first completes, since only one divide unit exists. On the other hand, two multiply operations may take place at the same time because two multiply units are provided. The point to be stressed is that in most operational programs the instructions need not be executed in sequence. Instead, the majority of problems are composed of a series of smaller steps which are only indirectly related. The following programming comparison should illustrate this point.

The problem that follows is solved first by using a sequential computer and secondly, by using the 6600 with its functional units. Individual instruction execution times are assumed to be the same in both machines. Also, both have the capability of reading two.

source operands and returning one result by use of operating registers (X, B and A).

THE PROBLEM:

$$\left(\frac{A + B}{C}\right) \cdot (A^2 + B^2 + C)$$

THE OPERATING REGISTER CONTENTS: (where () means "the contents of")

(X1) = the value, A

(X2) = the value, B

(X3) = the value, C

THE PROBLEM THUS BECOMES:

$$\left[\frac{(x_1) + (x_2)}{(x_3)}\right] \cdot \left[(x_1)^2 + (x_2)^2 + (x_3)\right]$$

USING THE SEQUENTIAL COMPUTER: (where → means "replaces")

|    | Instructions                       | <u>Time</u> (nanoseconds) |

|----|------------------------------------|---------------------------|

| 1. | $(X1) + (X2) \longrightarrow (X4)$ | 400                       |

| 2. | $(X4) / (X3) \rightarrow (X5)$     | 2900                      |

| 3. | $(X1) * (X1) \longrightarrow (X6)$ | 1000                      |

| 4. | $(X2) * (X2) \longrightarrow (X7)$ | 1000                      |

| 5. | $(X6) + (X3) \longrightarrow (X0)$ | 400                       |

| 6. | $(X0) + (X7) \longrightarrow (XX)$ | 400                       |

| 7. | $(X5) * (X7) \longrightarrow (X6)$ | <u>1000</u>               |

|    | TOTAL TIME                         | 7100                      |

Since the instructions must be executed in sequence, the total execution time is the sum of the individual execution times, or 7.1 microseconds.

USING THE 6600:

1.

$$(X1) + (X2) \rightarrow (X4)$$

2.  $(X1) * (X1) \rightarrow (X6)$

3.  $(X2) * (X2) \rightarrow (X7)$

4.  $(X4) / (X3) \rightarrow (X5)$

5.  $(X6) + (X3) \rightarrow (X0)$

6.  $(X0) + (X7) \rightarrow (X7)$

7.  $(X5) * (X7) \rightarrow (X6)$

(NOTE: Time is shown in microseconds)

Using parallel functional units, the program execution time is only 4.3 microseconds, a reduction of approximately 40%.

Although the same saving will not occur in all programs, the example illustrates that, through efficient programing, a considerable decrease in execution time occurs. Even when a program is not optimized, a time saving will be realized. Details of time implications from the preceding chart are considered in later topics.

#### Summary

Several unique features are incorporated in the design of the 6600 central processor, including: 1) thirty-two (or sixteen) 4K, phased memory banks, 2) an instruction stack containing eight 60-bit registers, 3) twenty-four operating registers and 4) ten independent functional units. These provisions work in conjunction with each other to provide extremely rapid program execution times. Whenever parallel processing capabilities are provided in a computer, control circuitry is required to ensure that all features work together (without calamity) to produce a high-speed processing system,

#### BLOCK DIAGRAM ANALYSIS

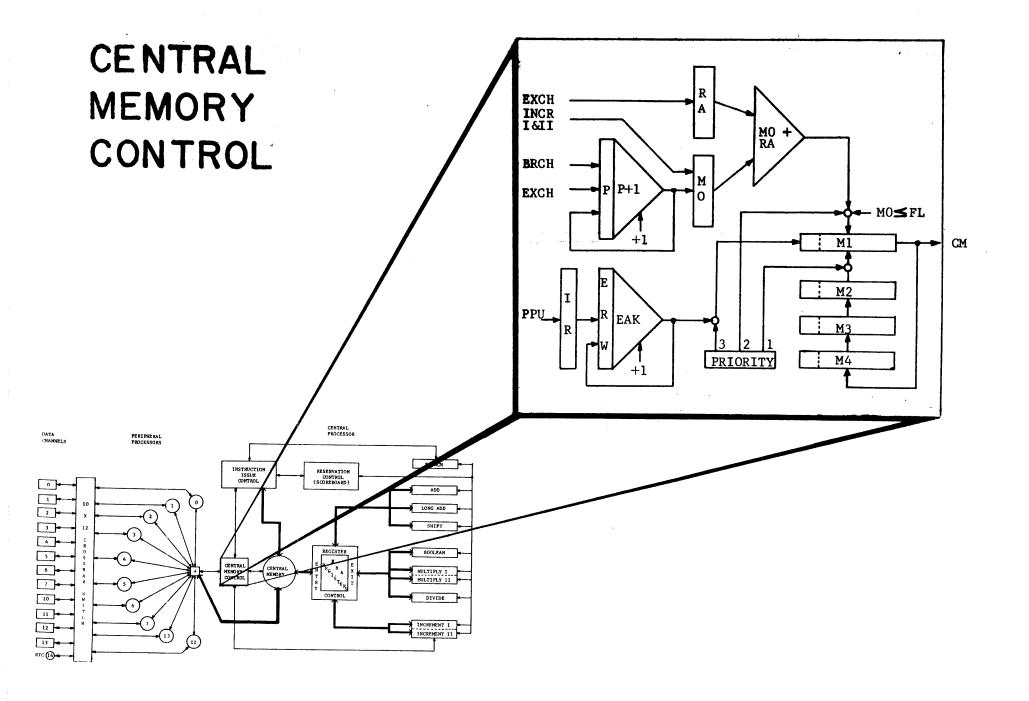

#### CENTRAL MEMORY ADDRESS CONTROL

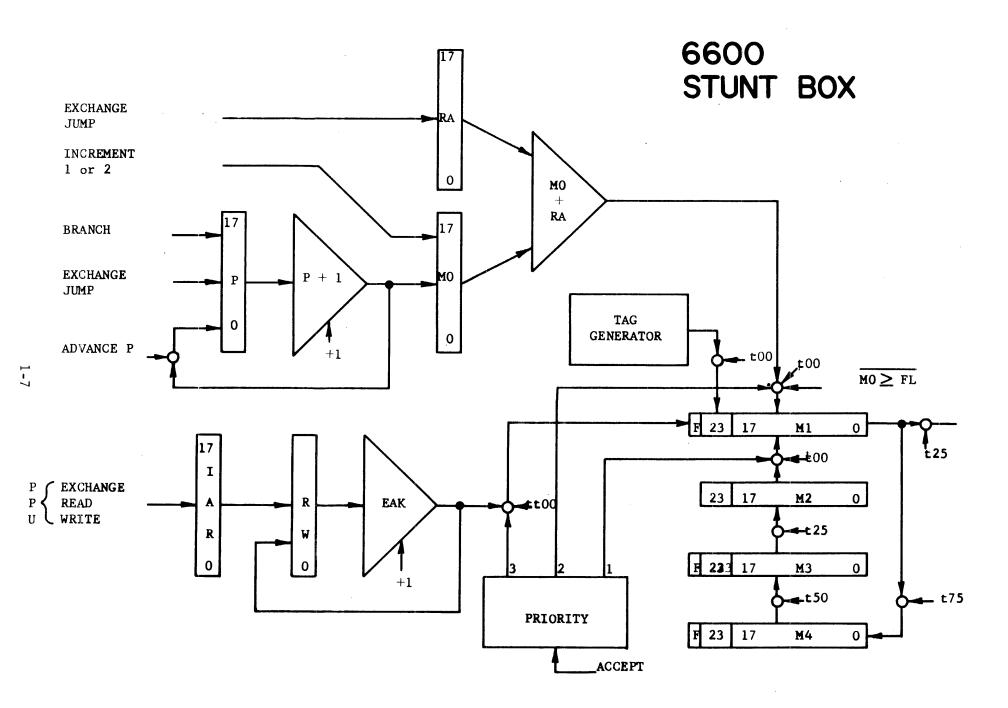

References to Central Memory can be initiated from various sources in the 6600. Peripheral Processors make central memory references during the central read, write and exchange jump instructions. The Central Processor uses central memory to fetch instruction words or to read and store operands. An orderly means for handling these memory requests and distributing the associated data must be utilized. This is complicated by the fact that the 6600 memory banks are phased to allow several memory cycles to be in progress at any one time. Therefore, it is very possible that a memory reference request be made to a bank that is already busy processing a memory cycle, so that the address must be saved and then re-issued. It is also conceivable that two requests occur simultaneously, requiring that a decision be made regarding which address will be issued first. Not only must the address be manipulated methodically, but the source or destination of the data associated with each address must be "remembered" by the control logic. These functions are accomplished for the most part, by the Central Memory Control logic, more often referred to as the Stunt Box.

Analysis of the Stunt Box takes place in the following sequence:

- 1) Hopper

- 2) Priority Network

- 3) Tag Generation and Distribution

#### HOPPER

The Hopper is a mechanism used to save conflicting addresses so they may be re-issued to the memory banks repeatedly, if necessary, until accepted and processed. Along with addresses, the Hopper saves gating information used to enable the data corresponding to each address through the memory Data Distribution logic to or from memory.

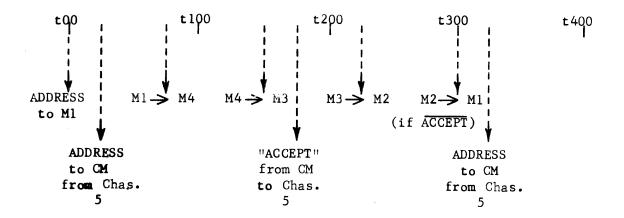

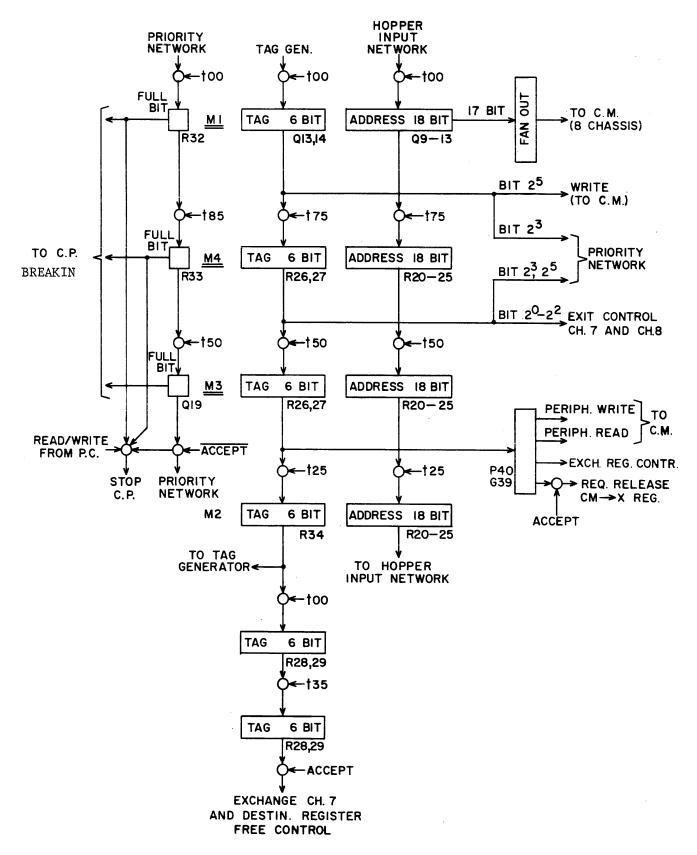

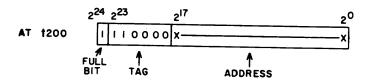

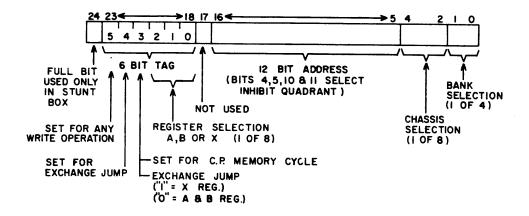

Physically, the Hopper is four flip-flop registers (designated M1, M2, M3 and M4) each of which stores an 18-bit address, 6-bit tag and a Full bit (except M2, which has no Full bit). Refer to Figure 1-2. The registers are connected to each other in such a manner as to allow information to circulate through each of the registers (the concept is similar to the Peripheral Processor barrel). A 75 nanosecond time interval exists between each register and produces a total re-circulation time of 300 nsec. For example, an address entered into M1 at time 00 enters M4 at t75, M3 at t150, M2 at t225 and (if it must be re-issued) re-enters M1 at t300.

Figure 1-2

In actuality, only 17 of the 18 available address bits are used in a 131K central memory. The 18th bit is round throughout the memory circuitry, but is never utilized. The 6-bit tag is generated when an address is first entered into the hopper (specifically, M1) and it contains all the information necessary to properly distribute the associated data. Tag generation and distribution is almost a subject in itself and is treated separately later in this section. The Full bits found in M1, M3 and M4 indicate that a meaningful address and tag are contained in the respective register. It is set when an address and tag are entered into M1. There is no full bit in M2, since the Accept signal (explained below) serves a similar purpose.

Approximately 50 nsec after entering an address into M1, the address is automatically sent to the memory banks, where the lower 5 bits are examined to select one of the 32 banks. If the desired bank is not in use (busy), an Accept signal is returned to the Stunt Box to indicate that no conflict exists and the memory cycle has been initiated. The address saved in the Hopper is then discarded. If the desired bank is busy, an Accept will not be returned. Its absence causes the associated address to be re-entered into M1 (from M2) and subsequently, reissued to the memory banks. The cycle will recur every 300 nsec until the address is accepted.

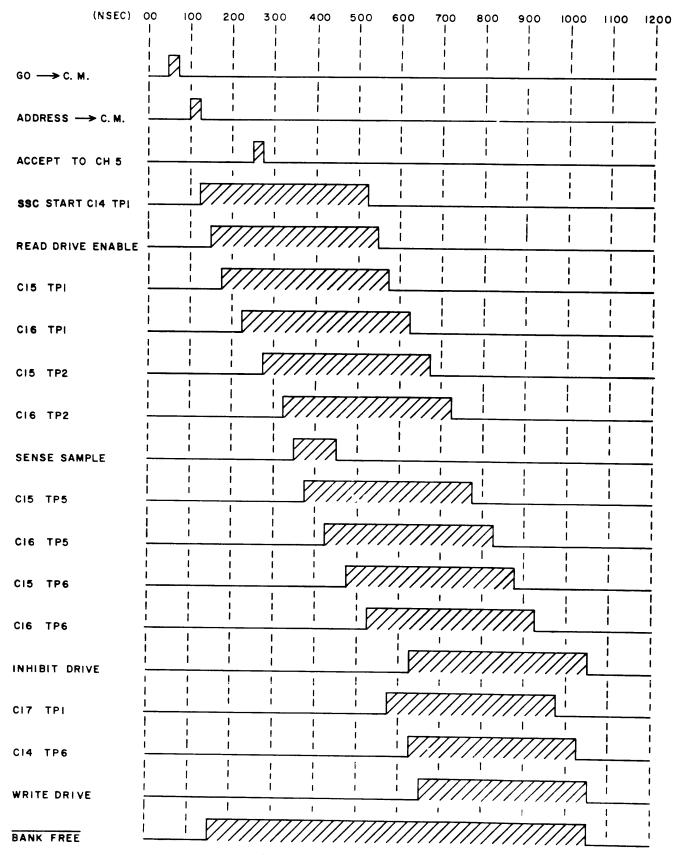

Figure 1-3, a timing diagram, verifies that the Accept is returned to the Stunt Box in time to disable (or if not returned, enable) the transfer of M2 to M1. If an Accept is generated, it will be received on Chassis 5 about 175 nsec after entering the associated address into M1 (t175). This allows 125 nsec of logic delay time before the Accept is used to disable the M2—>M1 transfer (t300). Since M2 was not transferred to M1, the following transfer of M3 to M2 will destroy (write over) the contents of M2.

Figure 1-3.

#### PRIORITY NETWORK

Because more than one source exists for addresses entered into M1 (See Figure 1-2) a Stunt Box Priority Network is necessary to ensure organized handling of simultaneous memory requests. Each address source has a fixed priority, as follows:

First Hopper (M2  $\longrightarrow$  M1)

Second Central Processor (M0 → M1)

Third Peripheral Processor (ERW → M1)

#### HOPPER PRIORITY

In only one circumstance is re-entry of an address to M1 required: when an address has been sent to the memory banks and was not accepted due to a bank conflict. Non-acceptance of an address is indicated by not receiving an Accept from the memory banks 175 nsec. after issuing an address.before enabling an M2 —>M1 transfer it should also be determined that M2 contains a meaningful address. This is indicated by the presence of a Full bit. Since M2 does not contain a Full bit, the M3 Full bit is checked. (It is time delayed to ensure that M3 has been transferred to M2 before the check is made.) Thus, two conditions must be met to grant first priority:

#### CENTRAL PRIORITY

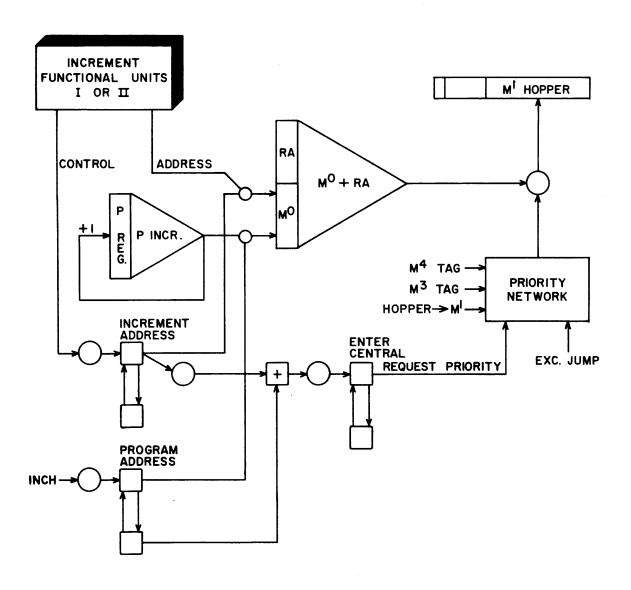

Two sub-priorities exist under Central Priority because central processor memory references may be originated in two independent operations

- 1) Instruction word fetching (RNI's)

- 2) Reading and storing operands

In the first case, the address is obtained from the P register and in the second, from one of the two Increment Functional Units. If requests from both sources occur simultaneously, the operand address is entered first, then the instruction address. In either case, the address is entered into an 18-bit register, MO (Figure 1-2). At the same time a control flip-flop called "Enter Central" is set and indicates that an address is in MO waiting for entry into M1. (In a sense, the Enter Central flip-flop requests priority #2). Thus, one condition required for priority #2 is that Enter Central is set to indicate that an address is in MO waiting for entry into M1.

A second condition needed for central priority is that priority #1 does not exist (i.e., the address in M2 was accepted or M2 does not contain a meaningful address).

A special circumstance arises which also must be considered in granting central priority. This is the case when read and store requests are made to the same memory address. This might occur when an instruction word modification is made followed by an RNI request for the modified word. If the two addresses enter the hopper in sequence (store location X, then read location X) storing before reading cannot be guaranteed because a bank conflict may exist with the store address. The operation (read or store) that is performed first depends strictly on when the bank goes BUSY. Whichever address is sent to the banks first (after BUSY) will be accepted and will cause a conflict for the second reference to the same location. Thus, it would be possible, in the above instance, to read the unmodified instruction word when actually, the modified word was desired. The reverse situation might also occur, wherein a location was to be read before modification.

To resolve the above cases, additional logic is required in the priority #2 circuitry which prevents a Central Read address from being entered into the Hopper if any (Peripheral or Central) Write address is in the Hopper. Also, if a Central Write is attempted, no Central Read address may be in the Hopper. (Prevention of a Central Write and Peripheral Read out of sequence is a software responsibility.)

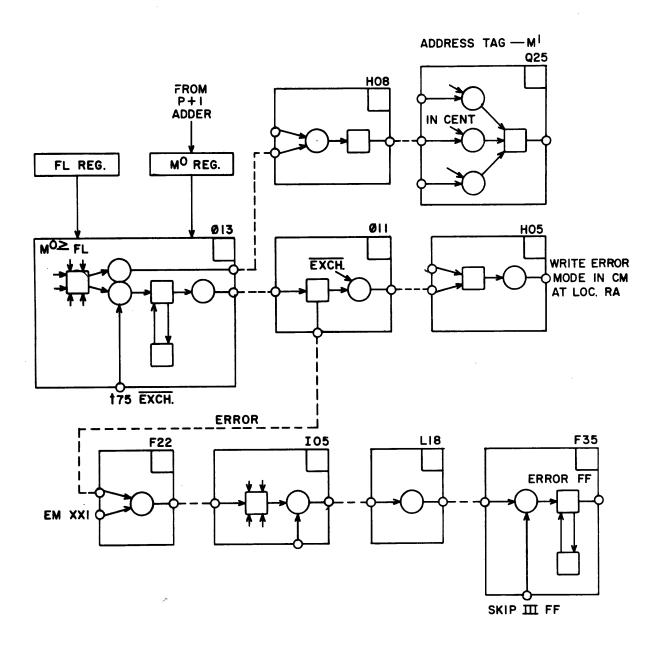

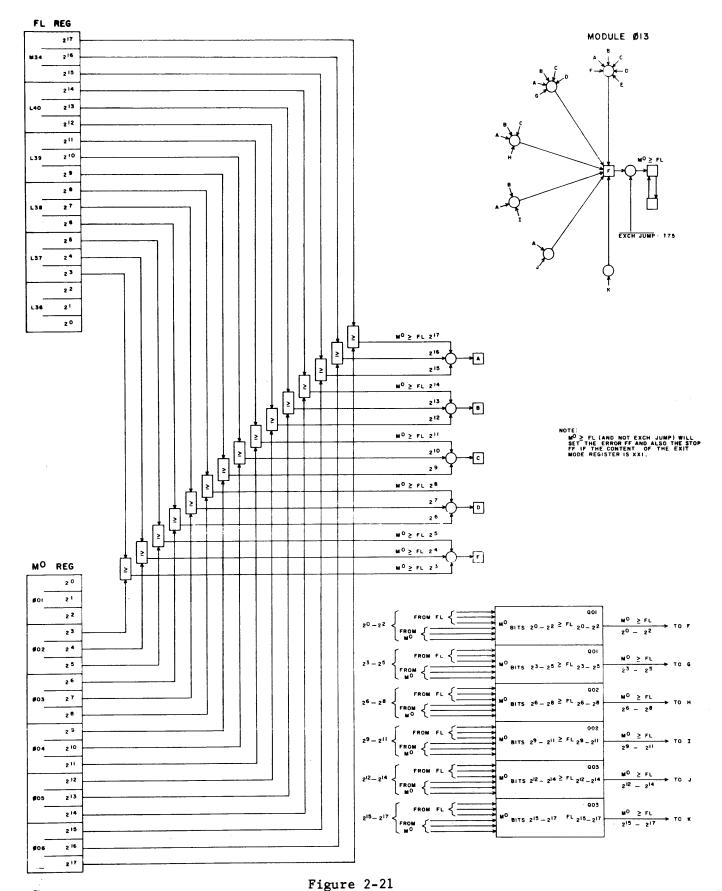

The fourth, and final condition needed for Central Priority, is that the address being referenced must not be out of the bounds for this particular program. Memory bounds for a program are defined upon initialization of the routine (EXCHANGE JUMP) by the RA (Reference Address) and FL (Field Length) values. RA specifies the lower bound and RA + FL -1, the upper bound. Each central memory reference adds to the value RA, the content of P (for RNI's) or the Increment I or II address (for operand references). Thus, the address being referenced (P, Incr. I or Incr. II) is said to be the "relative" address. The absolute CM address is the sum of the relative address and the content of RA. The relative address is always entered into MO. A special Adder adds MO to RA and yields the absolute address. Another circuit compares the content of MO with the content of FL. If MO FL, the desired reference is "Out of Bounds", and the memory reference will not take place because Central Priority will not be granted. Thus, the condition MO FL is also a condition required for granting Priority 2.

The following Boolean formula summarizes the conditions required for granting Central Priority:

#### PERIPHERAL PRIORITY

Peripheral priority for CM references is granted only if neither Hopper nor Central priority exists and there is a peripheral processor request for a CM access. Since only one PPU request can occur at a time, no sub-priorities are required.

The PPU's request CM references in three situations:

- 1) Read central memory

- 2) Write central memory

- 3) Exchange jump.

In all three cases, a PPU will send an 18-bit address to the Input Address Register (IAR) of the Stunt Box (See Figure 1-2). To specify the type of reference being requested, a Read , Write or Exchange pulse accompanies the address. These are used as a control function, to properly gate information to and from CM (See Hopper Tag discussion which follows). The presence of one of the three control pulses results in the Request for Priority #3. Thus, the Boolean expression for Peripheral Priority is as follows:

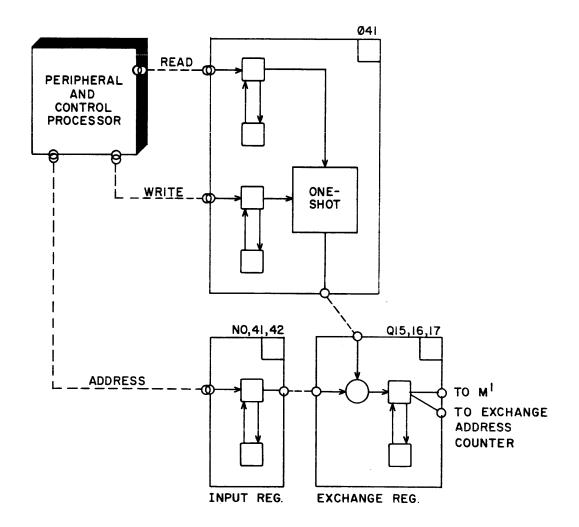

During peripheral processor read and write operations in central memory, a new address is sent to the IAR for every memory reference desired. For exchange jumps, only the starting address of the exchange jump package (in CM) is sent. It is the responsibility of the central processor to advance this address automatically in order to exchange the required information. This is accomplished by the Exchange Address Counter (EAK) which is utilized only during exchange jumps. It increments the exchange address for each of the 16 locations referenced.

#### HOPPER TAG GENERATION AND DISTRIBUTION

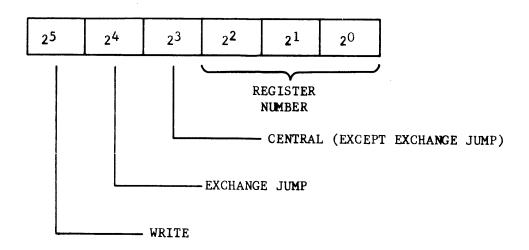

As previously mentioned, when an address is entered into M1, a 6-bit tag is also entered. It is used to properly gate data into and out of Gentral Memory. The tag bit positions are named as follows:

The bit  $(2^5)$  will be set any time the associated address is that of intermation to be stored (written) into Central Memory.

The bit  $(2^4)$  is set only during exchange jumps to indicate that the associated data is to be exchanged with registers in the CPU.

The bit  $(2^3)$  is set any time a memory reference is initiated by the Central Processor (Priority 2) and allows information to be gated to or from the CPU, as opposed to a PPU. During exchange jumps, the bit is set to indicate that an X register is to be exchanged, or cleared to indicate that A, B and Control Registers (P, RA, FL, etc.) are to be exchanged.

The bits  $(2^0 - 2^2)$  indicate (when applicable) which X, B, or A register number is to be stored, read into, or exchanged. Table 1-1 lists all legal tag numbers (in octal) and their meaning. Decoding circuitry exists only for those tags listed. Any other bit combination will either not be decoded, or will be decoded as one of the legal tags.

TABLE 1-1. HOPPER TAGS

|    |                          | 1  |                        |

|----|--------------------------|----|------------------------|

| 00 | Peripheral Read          | 63 | Exchange EM, A3, B3    |

| 10 | CP RNI                   | 64 | Exchange RA(ecs) A4,B4 |

| 11 | CP Read → X1             | 65 | Exchange FL(ecs) A5,B5 |

| 12 | CP Read → X2             | 66 | Exchange A6,B6         |

| 13 | CP Read → X3             | 67 | Exchange A7,B7         |

| 14 | CP Read → X4             | 70 | Exchange X0            |

| 15 | CP Read → X5             | 71 | Exchange X1            |

| 40 | Peripheral Write         | 72 | Exchange X2            |

| 50 | Return Jump + Error Stop | 73 | Exchange X3            |

| 56 | CP Write X6              | 74 | Exchange X4            |

| 57 | CP Write X7              | 75 | Exchange X5            |

| 60 | Exchange P, A0           | 76 | Exchange X6            |

| 61 | Exchange RA(cm) A1,B1    | 77 | Exchange X7            |

| 62 | Exchange FL(cm) A2,B2    |    |                        |

A tag = 00 indicates a Peripheral Read address since all bits equal zero. This is interpreted as meaning:

(WRITE) (EXCHANGE) (CENTRAL) or Peripheral Read.

In this case the register bits  $(2^0 - 2^2)$  have no meaning and are not translated.

A tag = 10 indicates a Central Read Next Instruction (RNI) since the Central bit  $(2^3)$  is set and all other bits are cleared. Since a Central Read of Memory to X0 is not possible, the clear state of bits  $2^0$  -  $2^2$  in this case indicate that an instruction word is to be read from Memory.

A tag = 11 indicates that a Central Read to X1 is to be performed. Bits  $2^0$  -  $2^2$  in this case indicate the X register number. Tags 12-15 are also Central Reads to X registers, but to X2 - X5, respectively.

A tag = 40 indicates a Peripheral Write operation, since the write bit  $(2^5)$  is set and the Central and Exchange bits  $(2^3 \& 2^4)$  are both cleared.

A tag = 50 indicates a Central Return Jump or Error Mode Stop memory reference. Bits  $2^0$  -  $2^2$  are meaningless in this case since a Central Write (tag = 5X) of X0 is not possible. Since storage of information in central memory is required in the above cases, the 50 tag is reserved for this purpose.

Tags = 56 & 57 are generated when storage of X6 or X7, respectively, is desired. Bits  $2^0$  -  $2^2$  again indicate the register number.

Tags 60 - 77 are all generated during an Exchange Jump operation. Bit  $2^3 = 0$  indicates that A, B or Control registers are to be exchanged. Bit  $2^3 = 1$  indicates that an X register is to be exchanged. Bits  $2^0 - 2^2$  specify the operating register number (i.e., X, B or A) or the control register (i.e. P, RA, FL, or EM) to be exchanged. Note that these are the only cases when bit  $2^4$  (the Exchange bit) is set.

After a memory reference is initiated, the associated tag is decoded and will enable the gating of the desired information into and/or out of Central Memory, to or from the desired location (XBA registers, control registers, read or write pyramids, etc.).

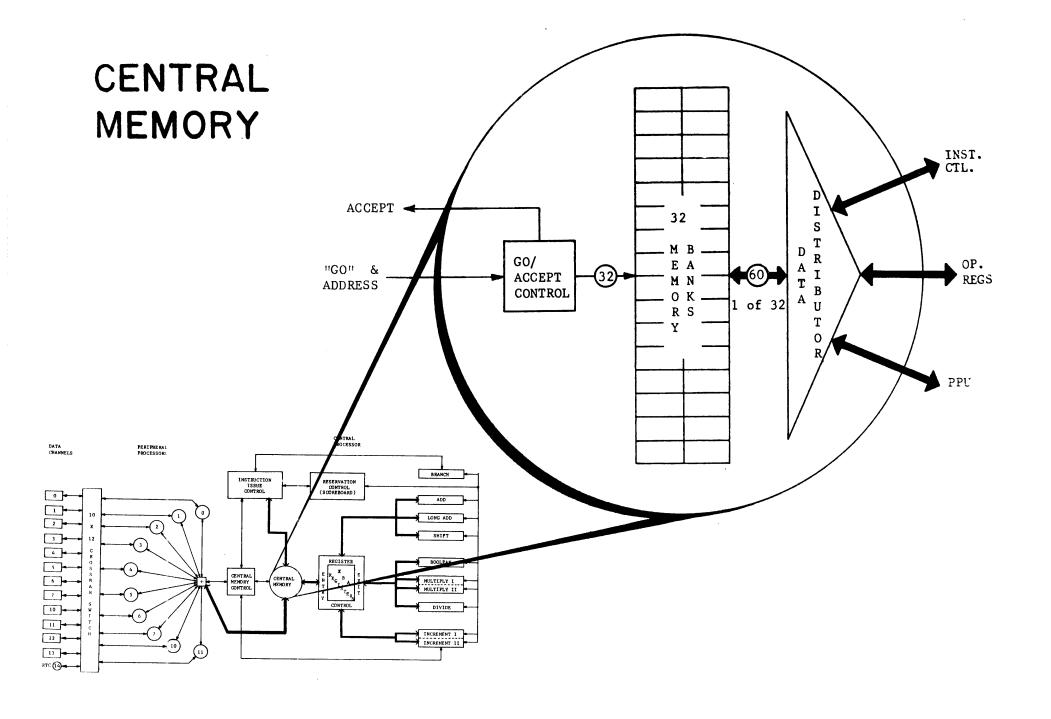

#### CENTRAL MEMORY

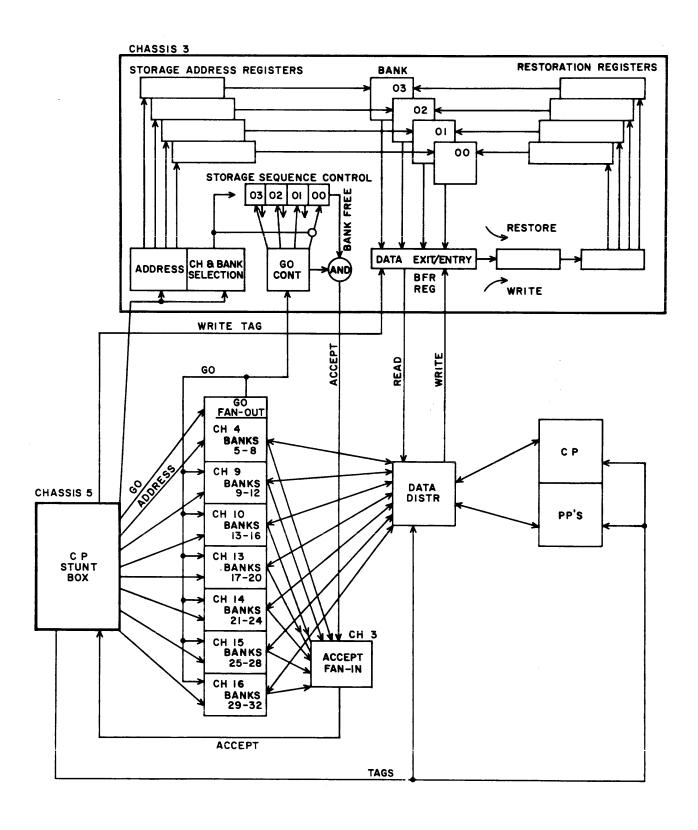

The 6600 Central Memory is composed of 60-bit words located in 16 or 32 memory banks each of which contains 4K words. This results in 65K or 131K memory sizes, respectively. In either case, 4 banks are contained on a chassis.

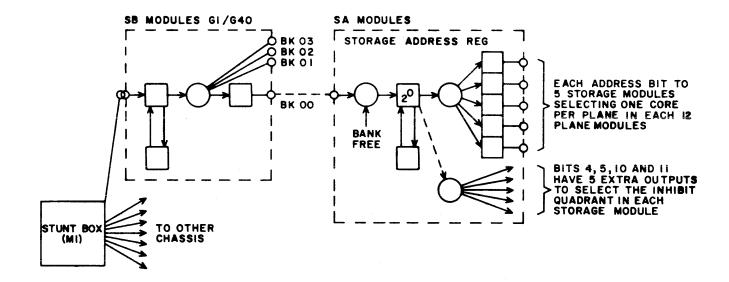

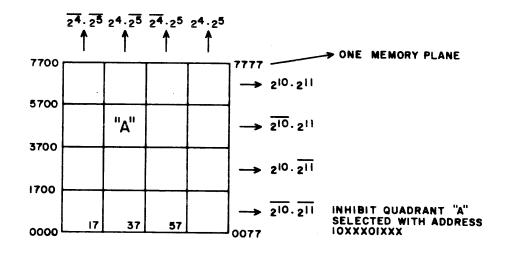

Selections of bank and chassis are made by decoding the lower 4 (for 65K memories) or 5 bits (for 131K memories) of the address. For example, in 131K system,

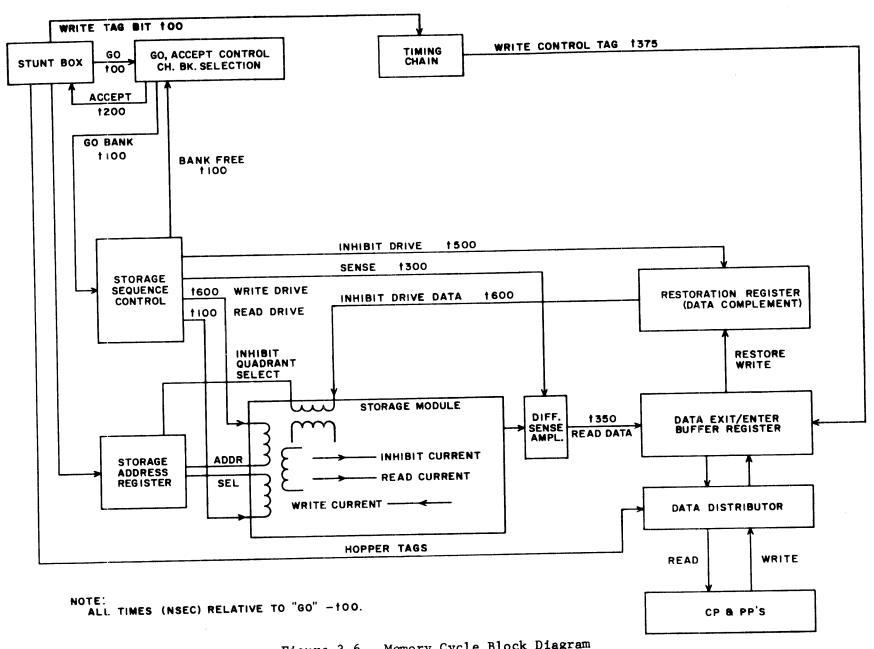

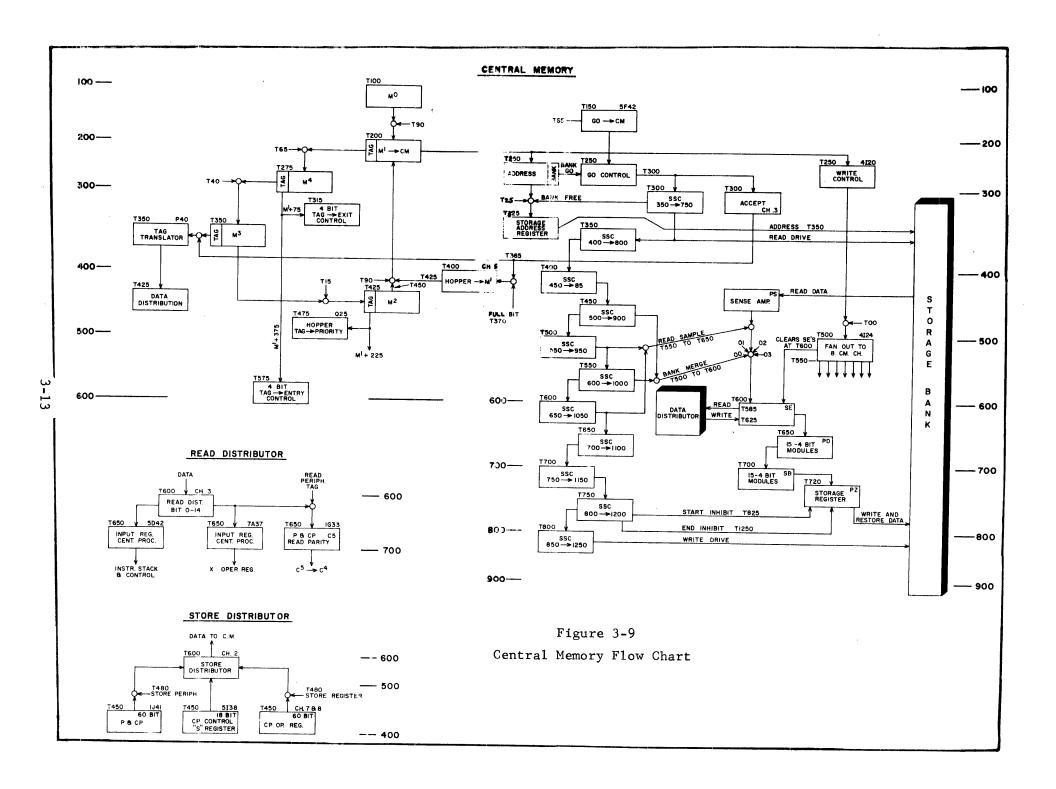

bits  $2^0$  and  $2^1$  select one of 4 banks on a chassis, while bits  $2^2$ ,  $2^3$  &  $2^4$  select one of 8 chassis. The address is sent from Chassis 5 to all memory chassis of a system and all chassis decode the lower bits of the address. Only one chassis will recognize its bit configuration  $(2^2 - 2^4)$ . By decoding bits  $2^0$  and  $2^1$ , the bank selection is made. If the selected bank is free (i.e., a memory cycle is not already in progress) the Accept signal is returned to the stunt box and a Go signal is sent to the selected Storage Sequence Control circuit (SSC). The SSC is a simple flip-flop timing chain which generates the read/write memory cycle.

The selected address within the selected bank is determined by decoding the remaining 12-bits of the 17-bit address (16 bits for a 65K system). While a memory cycle is in progress, the bank busy signal (bank not free) disables initiation of other memory cycles within that bank. It also disables the return of the Accept signal to Chassis 5, which causes the address to be retried at the 300 nsec stunt box rate.

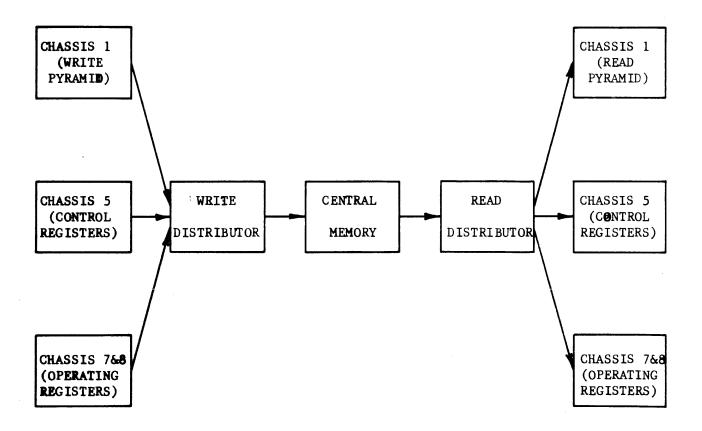

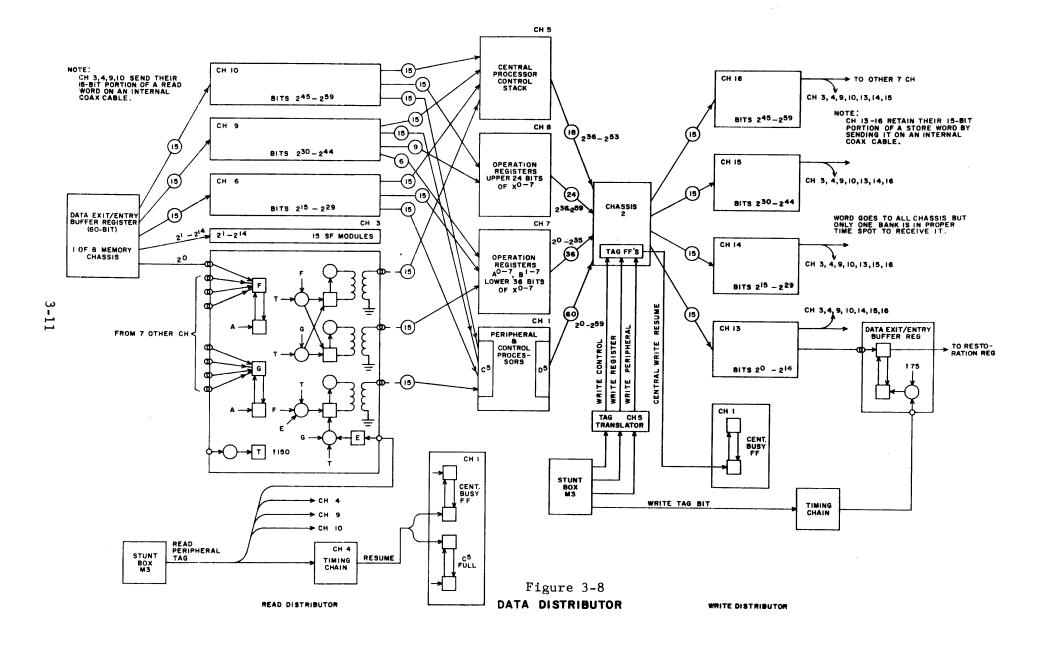

The information being read from or stored into central memory is gated by a circuit called the Read/Write distributor. It, in essence, distributes information to and from the 4 Chassis connected to central memory as shown in Figure 1-4.

Figure 1-4.

Determination of which information is to be gated is made by decoding of the Hopper tag associated with each address and ANDing the decoded signal with the Accept for that address.

Information is gated from the Write Pyramid on Chassis 1 to CM via the write distributor during PPU central memory write operations (tag = 40).

Information is gated from Chassis 5 during return jumps and Error Mode Stops (tag = 50).

Information is gated from Chassis 7 and 8 during Exchange Jumps (tags = 60 - 77) and central processor store operand operations (tags = 56 or 57).

Information is sent from C.M. via the Read distributor to Chassis 1 during PPU central memory read operations (tag = 00).

Information is sent to Chassis 5 during Exchange Jumps (tags = 60 - 65) and RNI (tag = 10) operations.

Information is sent to Chassis 7 and 8 during Exchange Jumps (tags = 60 - 77) and central processor operand read (tags = 11 - 15) operations.

It is re-emphasized that in all cases of gating the Read/Write distributor the Accept signal is necessary. This ensures that the information desired is properly timed for entry to or exit from memory.

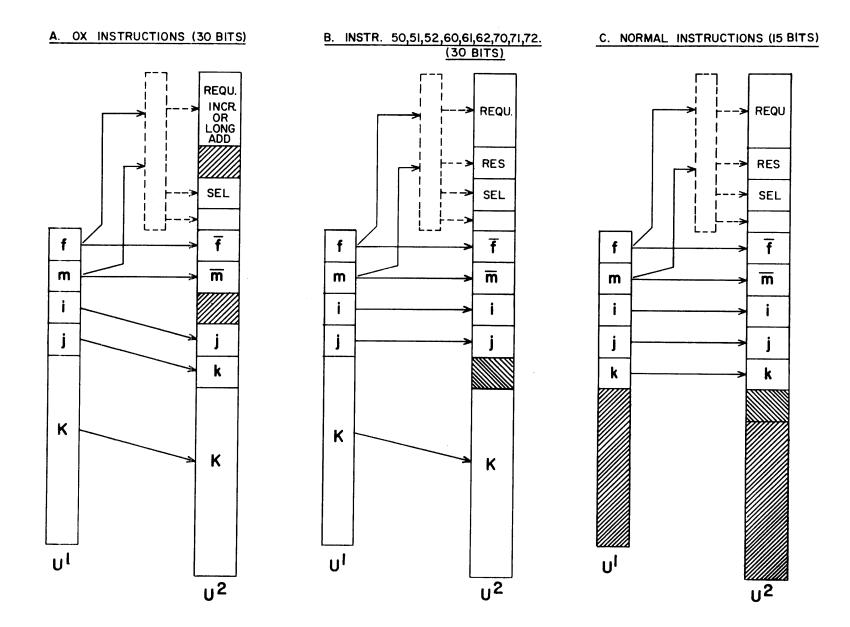

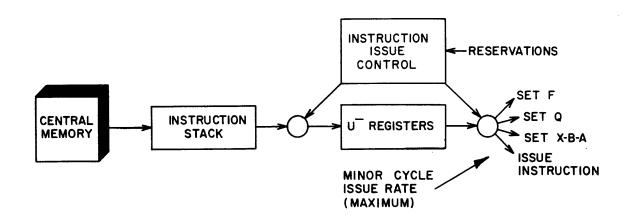

#### INSTRUCTION CONTROL

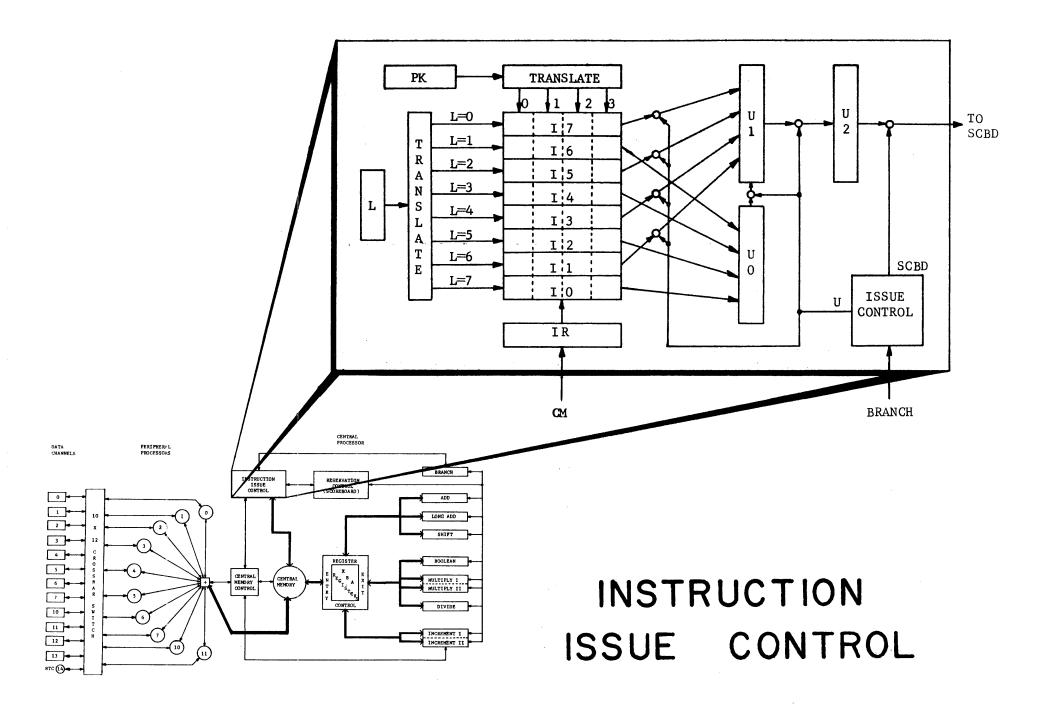

Instructions in the Central processor are executed from the Instruction Stack (shown in Figure 1-1). Each 60 bit Stack register can contain up to four instructions, since the Central processor employs both a 15 bit and a 30 bit instruction format, and as few as two. The responsibility of Instruction Control is to determine that a 60 bit Instruction word has become available to the stack, sort out the 15 or 30 bit instructions within that word, and then deliver the instructions to Reservation Control so they can be executed.

Initially all instruction words (a 60 bit memory word fetched by an RNI request) move into the bottom rank of the stack (IO) when Instruction Control receives the RNI tag (TAG = 108 and accept) from the Stunt Box. The RNI tag also signals Instruction Control to begin the process of sorting instructions within that word and transfering them to Reservation Control. The total process is called Instruction Issue, and the sorting of instructions is referred to as Parcelling.

#### INSTRUCTION ISSUE

Instructions can be issued from any rank of the stack, however if we were to assume an initial condition such as at the end of an Exchange Jump sequence we would see issue beginning with the upper instruction in IO. Once a program is in execution, program control can be transferred to some higher rank of the stack by a Branch instruction. This situation forces Instruction control to keep track of which rank of the stack the Program address is currently indicating. The "Locator" (L) register and counter perform this function. Control of the L count would be very similar to control of the Program Address. However, L refers to a particular rank of the stack so it would only vary between 08 through 78. Example: L count = 08 indicates program control is currently in IO. L count = 78 indicates program control in I7. An initial Master Clear would set the L count to 08, so we can see that Instruction Issue would start from the bottom rank of the stack.

NOTE: The L register contains the complement of the L count.

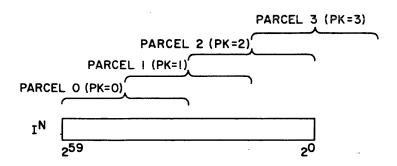

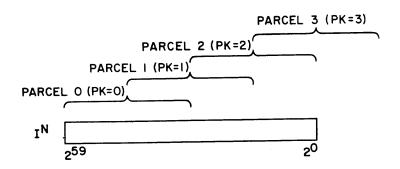

Now that we have selected a particular rank of the stack, we must concern ourselves with sorting out the instructions within that rank. In other words we must parcel the instructions from the selected rank of the stack. Each rank is considered to have four overlapping 30-bit Parcels.

```

These are: parcel 0 - bits 30 through 59

parcel 1 - bits 15 through 44

parcel 2 - bits 00 through 29

parcel 3 - bits 44 through 14 (end around)

```

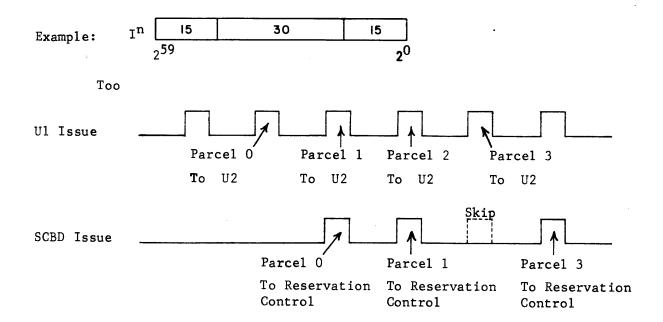

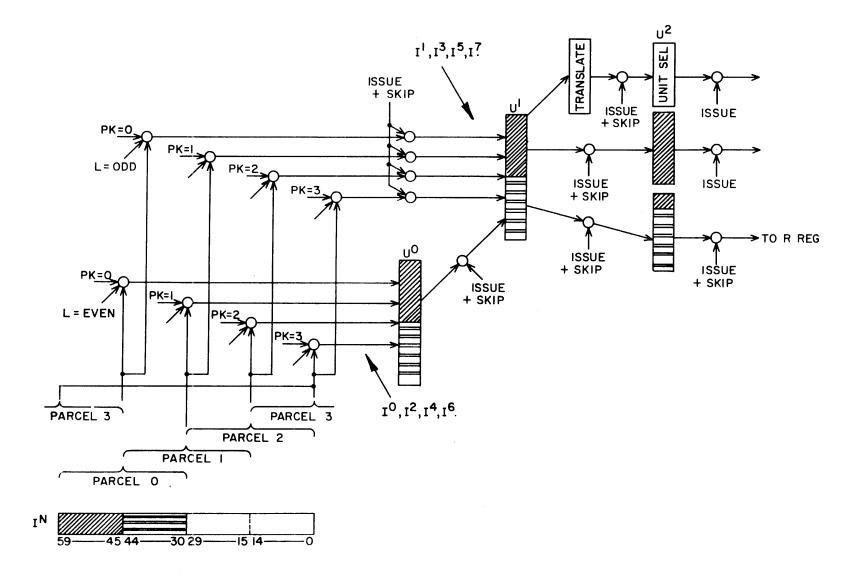

Figure 1-5 Instruction Word Parcels

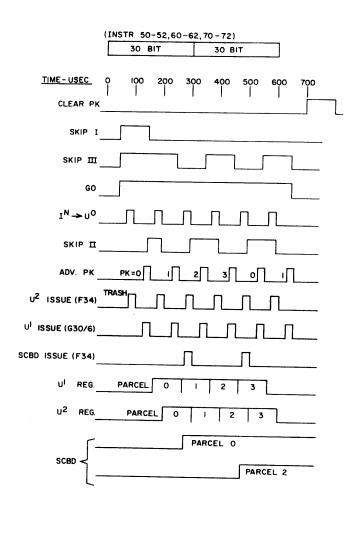

By examining each word with the 30 bit parcels we guarantee the detection of any possible combination of instructions within that word. If the instruction contained within the parcel happens to be a 15 bit instruction the lower 15 bits of the parcel are discarded and the next sequential parcel is extracted. However, if a 30 bit instruction is encountered, the entire parcel would be used and the next sequential parcel would be skipped.

#### Example:

| In | 15  | 15 | 15 | 15 |

|----|-----|----|----|----|

| :  | 259 |    |    | 20 |

Here each parcel would be extracted in sequence with the lower 15 bits of each parcel being discarded.

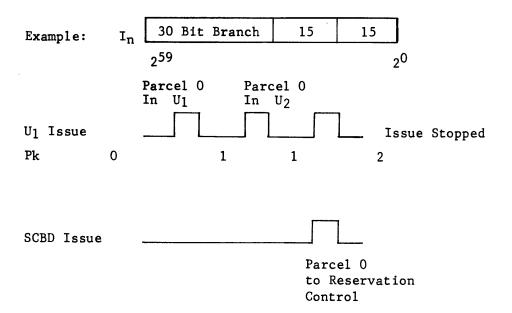

| In | 15  | 30 | 15 |

|----|-----|----|----|

|    | 259 |    | 20 |

In this example parcel 0 and 1 would be extracted in sequence all 30 bits of parcel 1 would be used, so parcel 2 would be skipped.

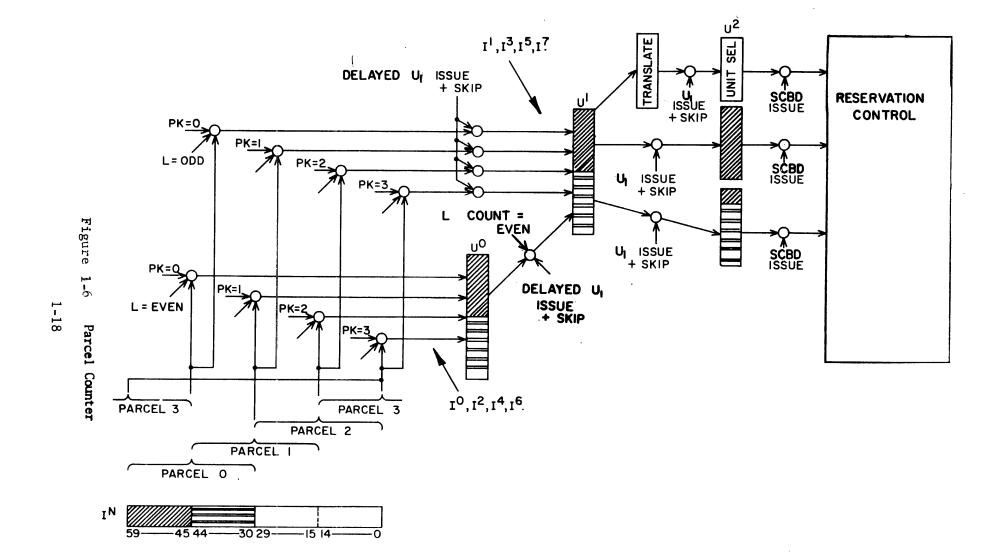

Instruction Control uses a two bit Parcel Counter (PK) to keep track of the current parcel and will generally advance the parcel counter after each parcel is extracted. An initial PK=0 condition would be set by Master Clear.

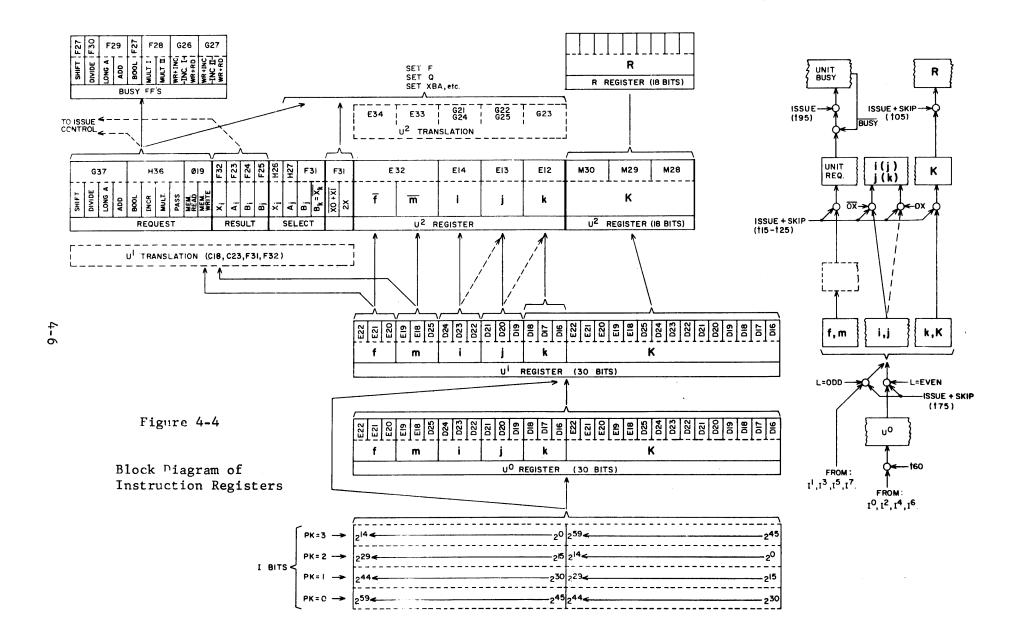

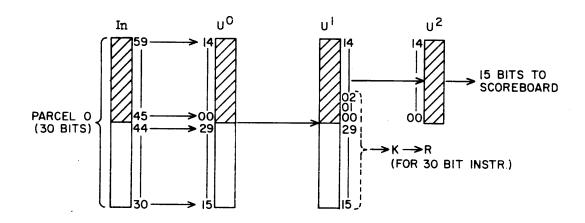

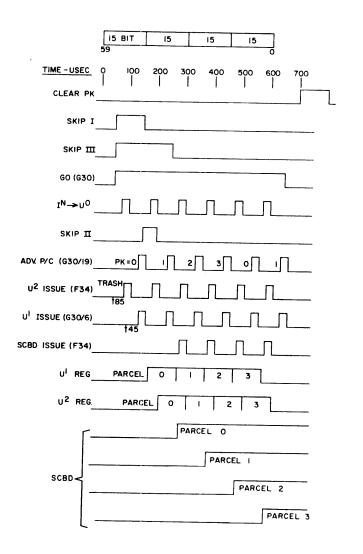

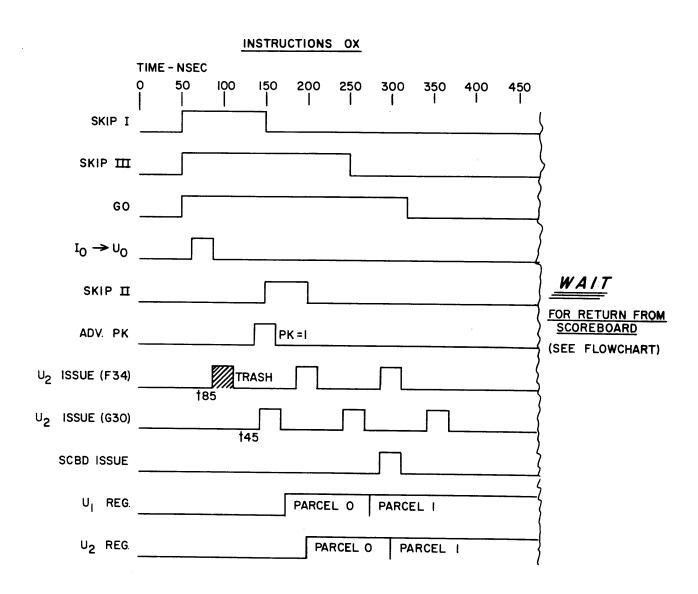

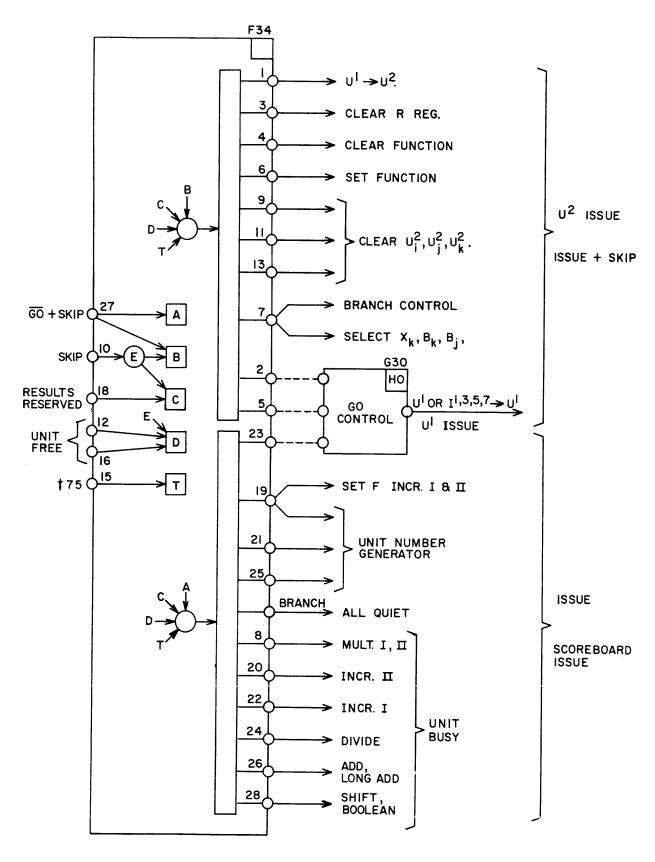

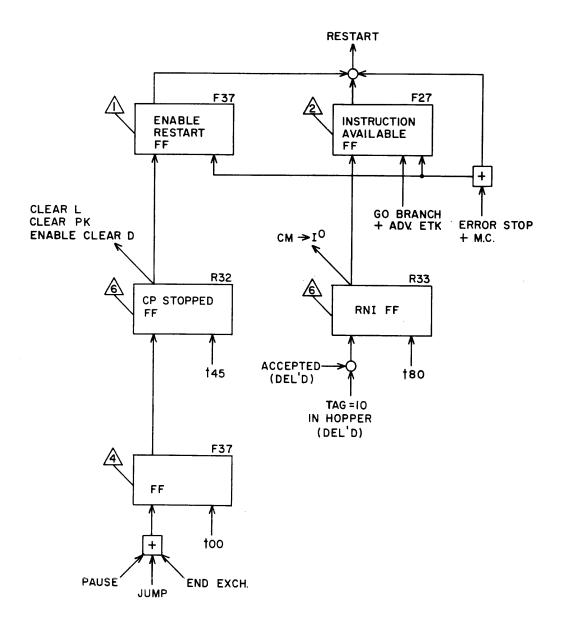

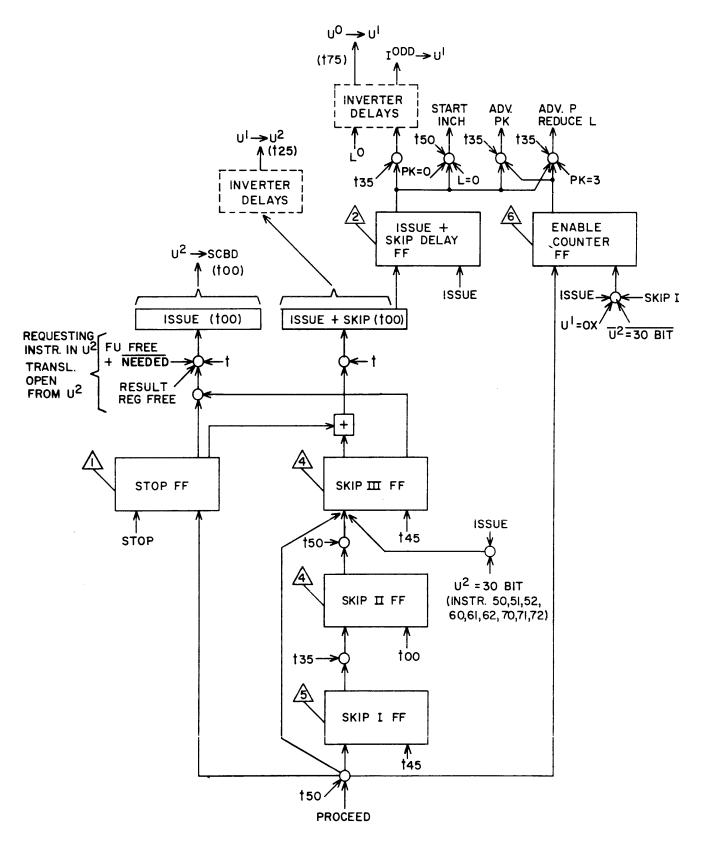

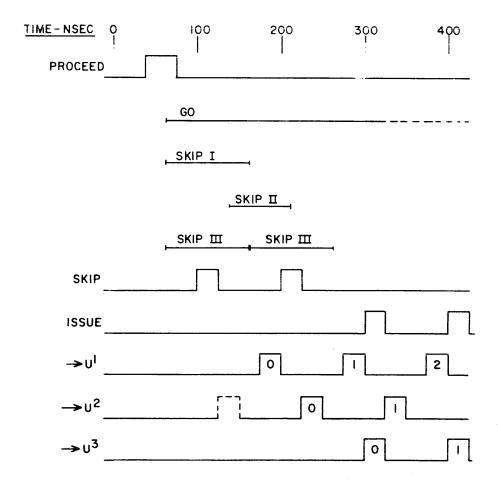

Initial Instruction issue begins with the L count = 0 (I0), PK = 0 (bits 30 through 59), and, as previously mentioned, the first Instruction word after an Exchange Jump comes from Central Memory to IO as a result of the RNI tag. The tag also starts the Issue operation, so the rest of our analysis can now be concerned with moving the instructions to Reservation Control. Figure 1-B shows the path each parcel will take.

Issue Control, generates two types of issue pulses. These are:

Ul issue - A pulse that gates the selected parcel to the Ul and U2 instruction registers and advances PK. This pulse occurs at a minor cycle rate during the issue sequence.

Scoreboard

Issue - A pulse that gates the parcel from the U2 instruction register to Reservation Control. This issue can also occur at a minor cycle rate.

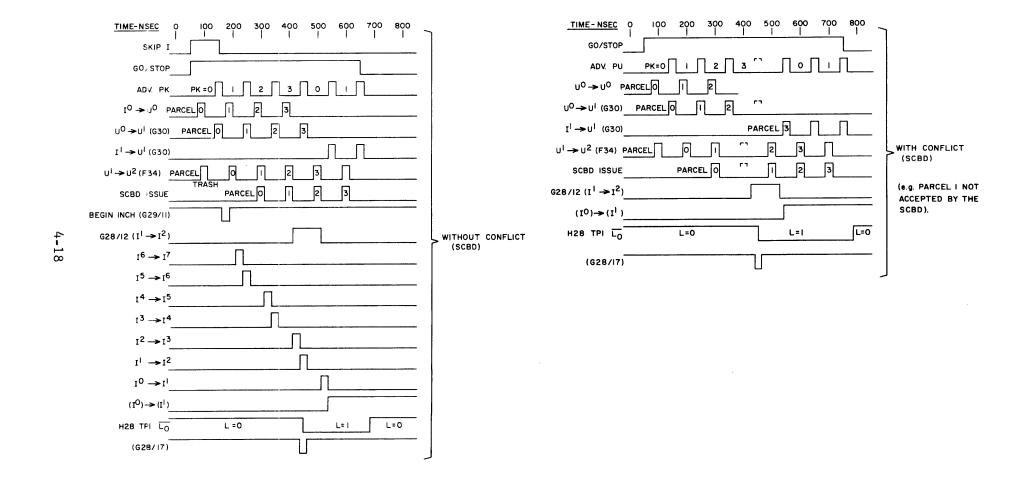

With eight different L counts and four different Parcel counts, it is easy to see that  $32_{10}$  different parcels must move through the U1 and U2 registers. Sixteen of these parcels(PK = 0, 1, 2, 3 L count = 0, 2, 4, 6) move from the even-numbered ranks of the stack to U0 before U1 issue would move then to U1. It is not necessary to have an issue pulse to move parcels to U0, so we would see the selected parcel from the selected even rank of the stack move into U0 automatically. In our initial case Parcel 0 of I0 would be the first parcel extracted to U0 and the first U1 issue pulse would move the parcel to U1.

Notice that at this time there have not been meaningful parcels in U1 or U2, so as far as the U2 register is concerned it receives "Trash" on the first U1 issue. Also, no scoreboard issue should be generated until after the first meaningful parcel has moved into U2. The PK being advanced to 1 by U1 issue would cause parcel 1 of I0 to be extracted to U0, so on the next U1 issue parcel 1 would move to U1, parcel 0 would enter U2, and PK would advance to 2.

One more U1 issue would move parcel 2 to U1, parcel 1 from U1 to U2, so at this time the first Scoreboard issue must occur to issue parcel 0 to Reservation Control. From this point both U1 and Scoreboard issue can continue at a minor cycle rate until parcel 3 is issued to Reservation Control (three more issue pulses).

All of the possible instructions in IO have now been put into

execution, and issue must stop until the next 60-bit Instruction word becomes available from Central Memory. This is called a "Pause".

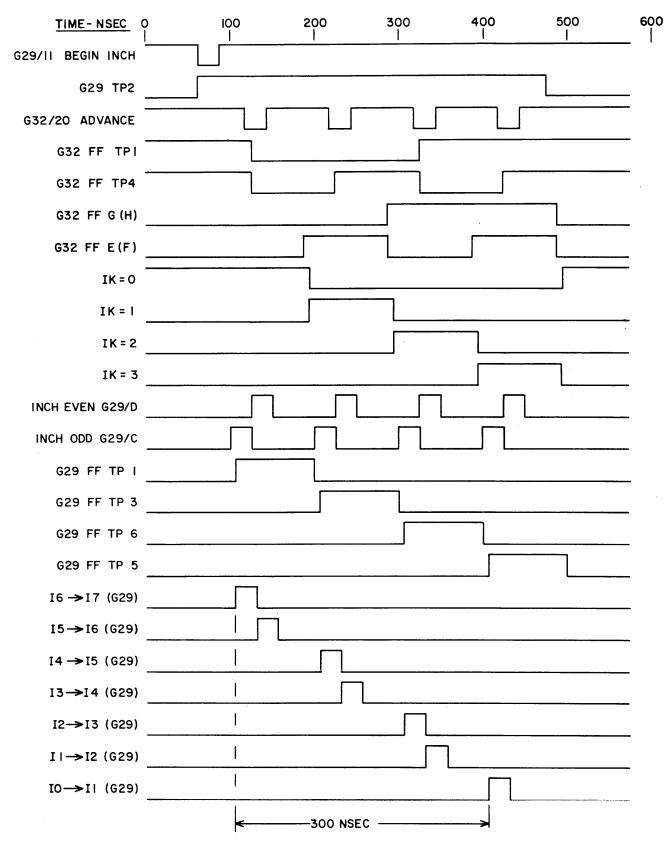

The Pause could be quite lengthy if Instruction Control had not had the foresight to request another RNI from Central Memory. This request is made any time L count = 0, PK = 0, and Ul issue. It is easy to see why the request is made under those conditions, once it is realized that IO is the bottom rank of the stack and after issuing from IO there wouldn't be any place to go for the next instruction. There is one other operation that comes into play at this time, and it is the process of moving the current instruction words of the stack up to make room for the next instruction word from Central Memory (Inching).

Inch is also started when L count = 0, PK = 0, and U1 issue. During the Inch process each rank of the stack is shifted up starting with an I6 to I7 transfer and continuing with I5 to I6, I4 to I5, I3 to I4, I2 to I3, I1 to I2, and I0 to I1 in that sequence.

Four minor cycles (400 nsecs) are necessary to complete the Inch, and it becomes necessary to advance the L count to 1, since the last Inch transfer moves the current Instruction word from IO (L count = 0) to Il (L count = 1). An important point to realize here is the I6 to I7 transfer destroys the Instruction word that was in I7. Consequently, a program loop that is to be executed within the Stack must fit in the stack between Il and I7. A quick examination of the stack reveals a maximum in Stack Program length of  $27_{10}$  instructions.

| 17 | 15 | 15 | 15     | 15     |

|----|----|----|--------|--------|

| 16 | 15 | 15 | 15     | 15     |

| 15 | 15 | 15 | 15     | 15     |

| 14 | 15 | 15 | 15     | 15     |

| 13 | 15 | 15 | 15     | 15     |

| 12 | 15 | 15 | 15     | 15     |

| 11 | 15 | 15 | 30 Bit | Branch |

| 10 |    |    |        |        |

Figure 1-7 Maximum In Stack Loop

The analysis of Instruction Issue to this point has assumed straight line program execution with no complications. There are, however, many special situations which may be encountered. Whenever a 30-bit Instruction is encountered in a parcel, Instruction Control must cause the next sequential parcel to be skipped. The skipping is accomplished merely by not generating a Scoreboard issue when the unwanted parcel is in U2.

There is also the possibility that Issue may have to be stopped if either the Functional Unit or the Result register (required by the parcel) are Busy. This is accomplished by Instruction control translating the parcel when it is in Ul and setting a Unit Request FF and Result Register Select FF when the parcel enters U2. Each Unit Request FF interrogates the corresponding Unit Busy FF in Reservation Control, and, if the Unit is busy, a signal is generated which blocks all Issue pulses un il the Unit becomes not busy.

A similar operation occurs with the Result register except the Result Register Select FF must be ANDed with a translation for the "i" portion of the Parcel to determine which portion of the Reservation List should be examined for a Reservation. The Reservation List (XBA) is where all Result register reservations are held by Reservation Control.

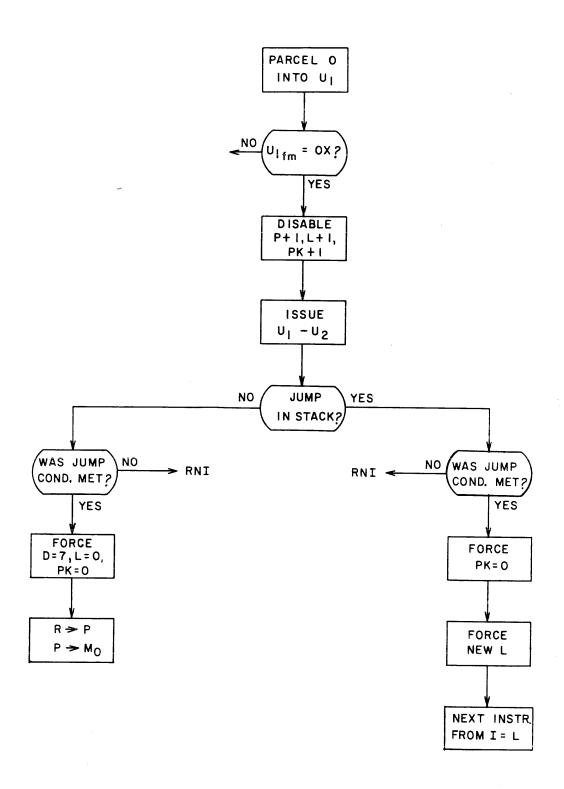

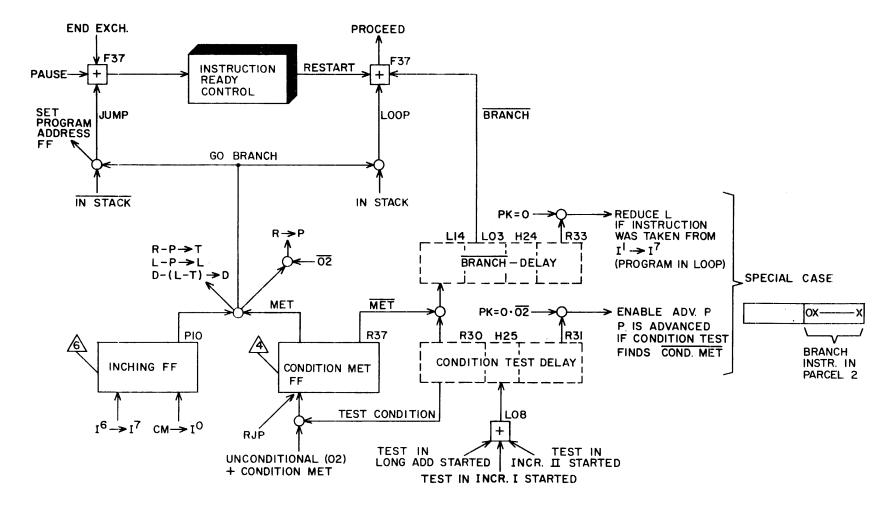

Probably the most involved operation in Instruction Control occurs when a Branch Instruction is encountered, and, even though the Branch Unit will execute the instruction, Issue Control must set itself up for proper operation. The reason for the complication of course, is that a Branch Instruction can do one of the following three:

Loop - a conditional Branch, condition met, and In Stack.

Jump - an unconditional Branch or a conditional branch, condition met, and not In Stack.

No Branch - a conditional Branch, condition not met.

Instruction Control will set itself up for the No Branch Condition by setting the Parcel Count equal to the parcel count of the next parcel to be issued, and then stopping Issue after issuing the Branch.

By controlling the Parcel count in this manner it is possible to restart issue the same as if it were starting after an RNI. Once the Branch has been issued, the Branch Unit makes a series of tests to determine whether the branch is to an instruction word already in the Stack.

The test results are only enabled on the Conditional Branch instructions  $03_8$  through  $07_8$  and enable these instructions to Loop. The first test is made by subtracting the current Program Address (P) from the Jump Address (R), and if the difference (T) is  $\pm 7$  or less the Branch may be In Stack.

However, a further test must be made to see if a jump of T places can be made relative to the current position in the Stack which is reflected by L. This is the L-T test and, if there is not an end-around borrow from the test, the branch still may be In Stack.

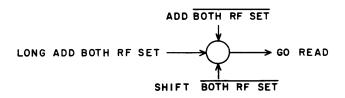

If R-P gave a positive result, the jump was forward and the L-T test being made successfully would say In Stack, but if R-P was negative, the branch was backward and a further test must be made to see if there is a usable instruction in the rank of the stack to which the jump is being made. Conveniently, the result of the L-T test would be the new L setting if the Branch is to be made, and this is subtracted from the Stack Depth Counter register (D). The D-(L-T) test is only necessary on the backward jumps (R-P negative) and, if it is successfully made, the branch would be In Stack. The Branch unit uses the Long Add unit to make the Branch Condition test for the 03g instructions, and the Increment units to test the 04g through 07g instructions. If the condition is met, a Go Branch signal is generated. If the R-P, L-T, D-(L-T) have all been successful, a Loop Proceed is generated.

If Go Branch occurs and R-P, L-T, and D-(L-7) were not successful, a Jump is generated. If Go Branch does not occur, a No Branch Proceed is generated. On a Loop Proceed, the Jump Address (R) is transferred to P, the result of the L-T test is gated to L, the Parcel Count is set to  $0_8$ , and Issue is restarted. On the Jump an R to P transfer is also accomplished, but L is set to  $0_8$  (L count =  $0_8$ ), the Parcel count is cleared, and an RNI request is made to the Stunt Box. (Issue would restart as a result of the RNI.) The No Branch Proceed merely restarts Issue, since this is why Instruction Control has been set up. There are many special cases that affect Instruction Control during branch instructions, but these will be covered in Section 4 along with a more detailed explanation of the other Instruction Control operations.

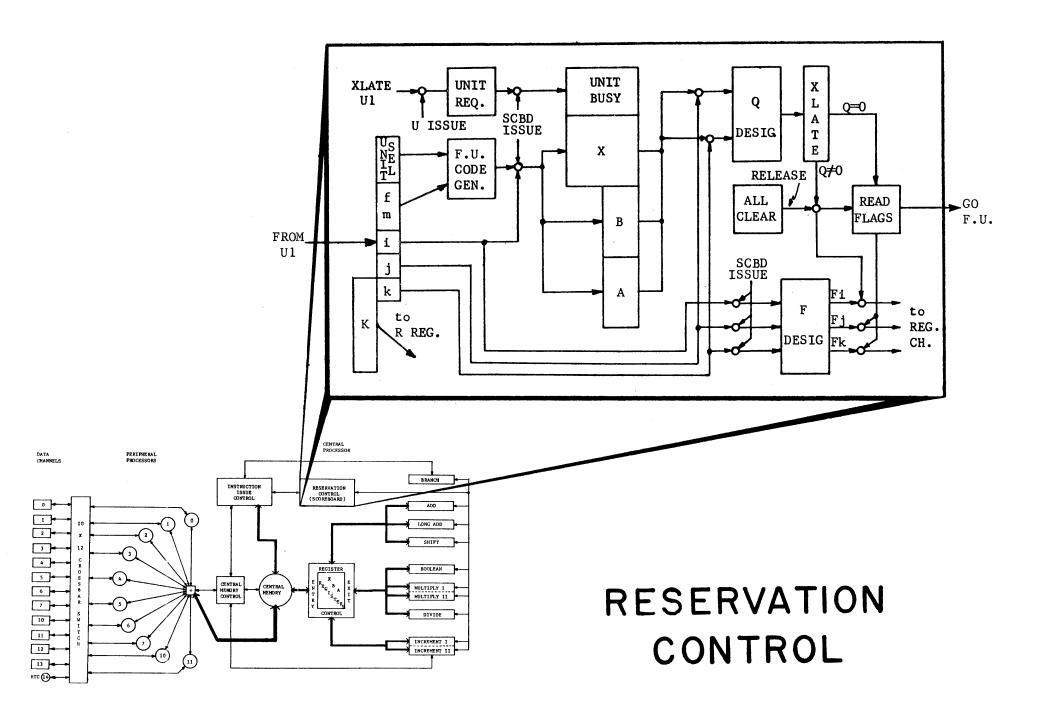

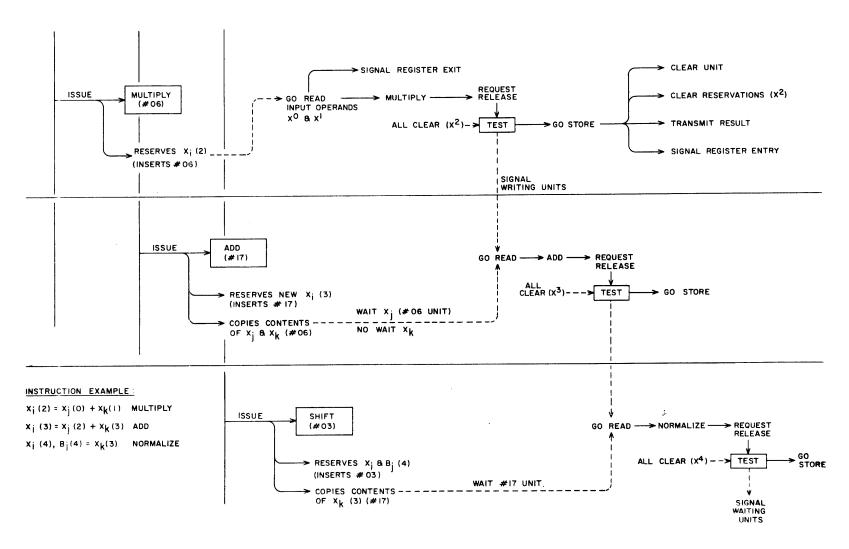

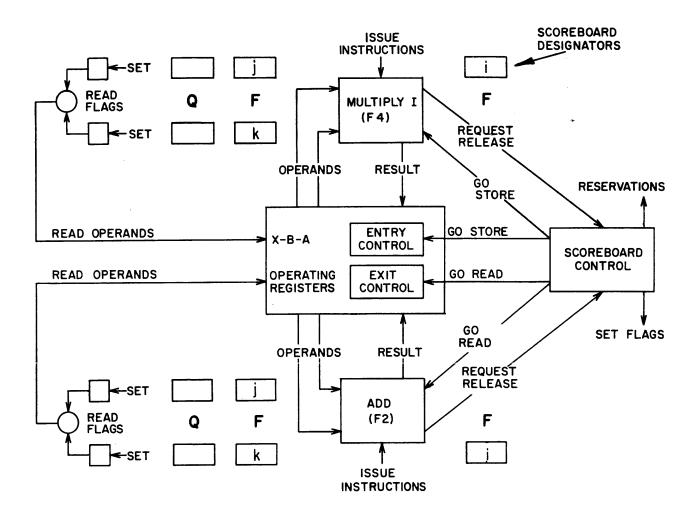

# RESERVATION CONTROL (SCOREBOARD)

The need for reservation control logic in the 6600 Central Processor arises due to the parallel processing concept of the CPU. This capability necessitates an orderly means of utilizing the functional units, operating registers and memory circuitry, since it is possible that several instructions require the same functional unit, operating register, etc. The scoreboard, then, makes the required reservations of each instruction and provides a means for the orderly handling of conflicts which may occur between instructions.

Conflicts are categorized into three groups - first, second and third order. The types of conflicts are defined as follows:

FIRST ORDER: A conflict between two instructions that require the same functional unit or the same result registers.

EXAMPLE 1: Functional Unit Conflict

$F X 6 = X1 \oplus X2$  $F X 5 = X3 \oplus X4$

Both instructions need the Floating Add functional unit for their calculation. Since only one such unit exists, the second instruction must wait until the first is finished, before it can be executed. Note that if two Multiply instructions are coded in sequence, no functional unit conflict occurs since two multiply units are provided.

EXAMPLE 2: Result Register Conflict

F X6 = X1 + X2F X6 = X4 \* X5

Both instructions require X6 for their result. In this case, the Floating Add result would be returned to X6 before the Multiply result was desired.

There are then, two types of First Order Conflicts - functional unit and result register. In all cases of first order conflicts, issuance of instructions stops until the conflict is resolved. In other words, no further instructions are initiated (including the one which "sees" the conflict) until the first of the conflicting instructions has completed. In conclusion, first order conflicts temporarily stop issuance of instructions at the point of conflict.

2) SECOND ORDER: A conflict that occurs when an instruction requires the result register of a previously initiated instruction as a source operand.

**EXAMPLE:**

$$F(X6) = X1 + X2$$

$F(X7) = X5 / (X6)$

In this case, the Divide unit needs X6, which is the result of the Add instruction, as one of its source operands. The Divide Unit must obviously wait for the Add unit to time out, but instruction issue will not stop. Instead, the Scoreboard will delay the start of the Divide instruction until the Add unit has stored its result. Subsequent instructions may be issued as long as no First Order conflicts exist.

The result of a Second Order Conflict is to delay the execution of the conflicting instruction only.

3) THIRD ORDER: A conflict that occurs when one instruction must store its result in a register which is to be used as a source operand for a previously issued instruction.

**EXAMPLE:**

$$F X3 = X1 / X2$$

$F X5 = X4 * X3$

$F X4 = X0 + X6$

In this example, due to the relatively long execution times of the Divide and Multiply op. codes and the second order conflict (X3) of these units, the Add instruction will complete its calculation before the Multiply unit has read its operands (both operands are always read at the same time; therefore, all second order conflicts must be resolved). Since the Multiply instruction is intended to read X4 before it is changed by the Add instruction, storage of the Add result must be delayed until the Multiply Unit begins its calculation. Thus, third order conflicts do not delay issue or calculation, but rather the storage of a result operand.

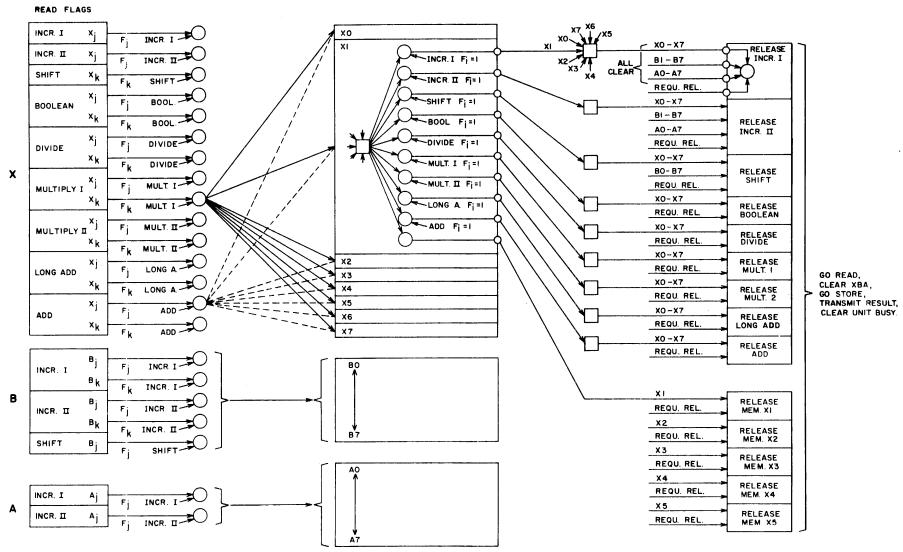

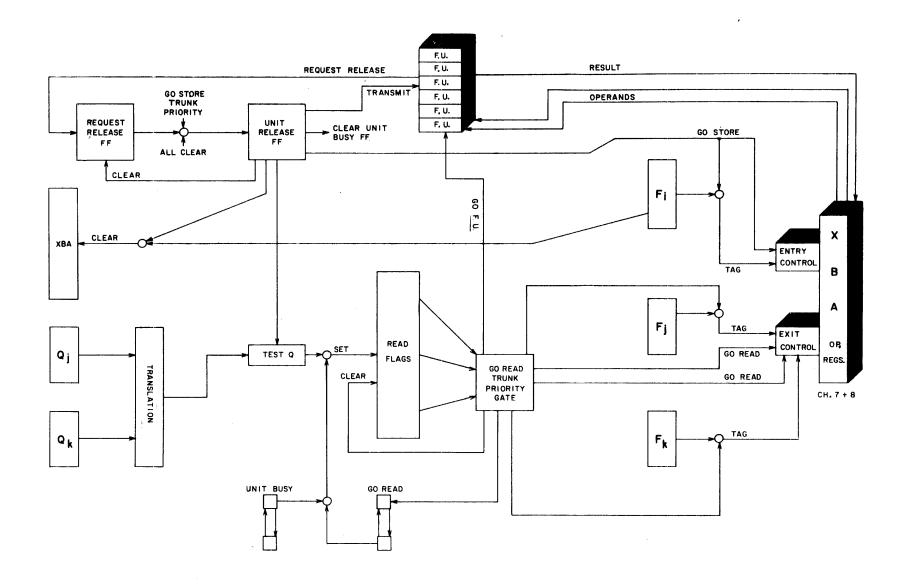

The following discussion explains, at the block diagram level, how these conflicts are handled by the scoreboard. Figure 1-8 should be used in following the explanation.

FIRST-ORDER CONFLICTS

First-order conflicts are defined as either functional unit or result register conflicts. If either type exists, no issues can be generated.

Functional unit conflicts are determined by checking the Unit Request flip-flops against the Unit Busy flip-flops. Recall that Unit Requests are set at the

SCOREBOARD BLOCK DIAGRAM

Figure 1-8

time an instruction is transferred from U1 to U2. The Unit Request flip-flop sets depending upon the op.code that is translated (from U1 fmi portion). When an instruction is issued to the scoreboard, among other things, a Unit Busy flip-flop will be set. This in effect, reserves a functional unit for a particular op.code - it will remain reserved until the given instruction has completed execution, at which time the Unit Busy flip-flop is cleared to allow a subsequent instruction to use that functional unit. Thus, when a given unit is needed (as determined by a set Unit Request flip-flop) it can be used only if the associated Unit Busy flip-flop is cleared. If the Unit Busy is set, a functional unit conflict exists and generation of issues is disabled until the unit is freed.

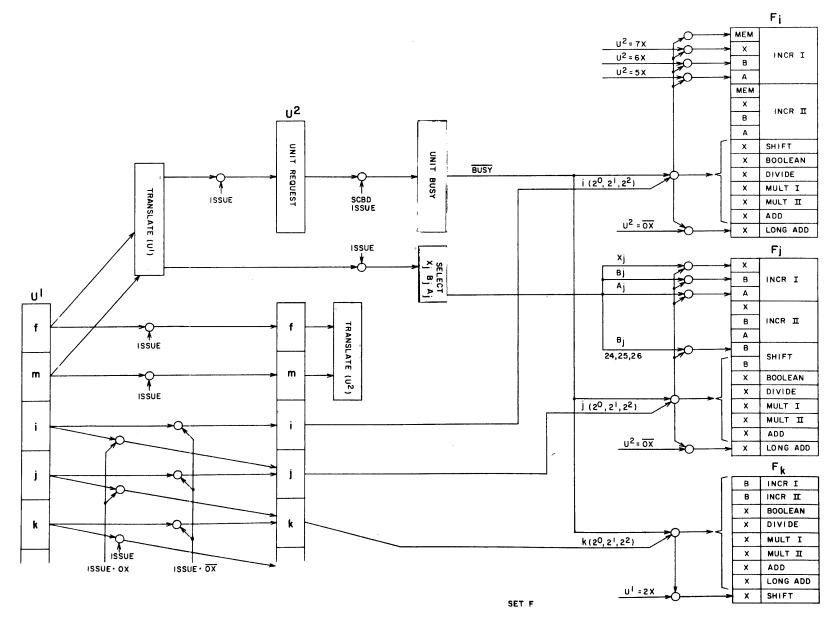

In determining the existance of result register conflicts, a comparison of the request and reservation logic is also made. Upon issuing an instruction to U2, Result flip-flops are set according to the op.code translation. Four such flip-flops exist and specify a result register group (i.e. Xi, Bi, Ai or Bj). The specific register within a group is determined by translating the i or j octals (as specified by the Result flip-flops). For example, if the Xi flip-flop is set and the U2 i digit = 3, X3 is the result register desired.

The result register reservations are placed in the "XBA reservation list" when an instruction is issued to the scoreboard. This list is composed of 24 "slots", where-in codes are placed to specify which functional unit has reserved each of the 24 operating registers. For example, a code of 16<sub>(8)</sub> in the X4 slot of the reservation list indicates that X4 is reserved for the result of the LONG ADD functional Unit. The complete list of possible codes follows:

| UNIT                   | CODE |

|------------------------|------|

| Increment 1            | 01   |

| Increment 2            | 02   |

| Shift                  | 03   |

| Boolean                | 04   |

| Divide                 | 05   |

| Multiply 1             | 06   |

| Multiply 2             | 07   |

| Read Memory, Channel 1 | 11   |

| Read Memory, Channel 2 | 12   |

| Read Memory, Channel 3 | 13   |

| Read Memory, Channel 4 | 14   |

| Read Memory, Channel 5 | 15   |

| Long Add               | 16   |

| Add                    | 17   |

|                        |      |

Any slot that contains an all-zero code indicates that the associated operating register is not reserved. Any non-zero code indicates that the associated register is reserved for a result. Thus, if translation of U2 indicates that X4 is specified as a result register and the X4 slot of the reservation list is zero, no conflict occurs. If the X4 slot is not equal to zero, the register is reserved. Thus, a conflict exists and issues are disabled until the conflict is resolved.

Notice from the list of codes that 5 are named Read Memory, Channel X. These are necessary for the  $5 \times 1 - 5 \times 5$  instructions. They return results from Memory to X 1 - X 5 and must make a result register reservation. In this sense, Memory acts like a functional unit.

In summary, both cases of first-order conflicts are handled similarly in that requests for units or result regsiters (made at U2 time) are checked against reservations existing in the Scoreboard. If a conflict exists, issues are disabled until the conflict is resolved.

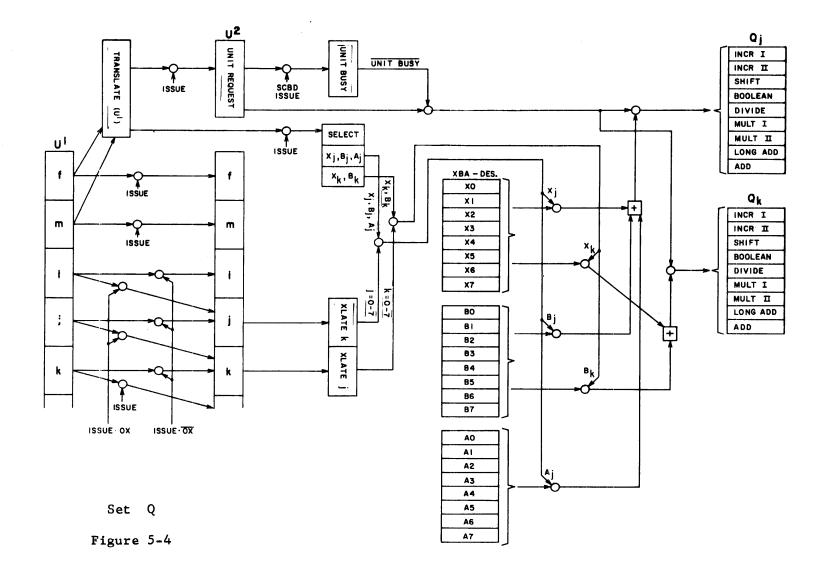

#### SECOND-ORDER CONFLICTS

Second-order conflicts occur when a functional unit requires as a source operand, the result of another functional unit. The source operands are defined by the j and k octals of U2 in conjunction with the select flip-flops which are set with a U2 transfer. The select flip-flops define the source register group as well as the octal digit specifying the register within that group (i.e. Xj, Bj, Aj, Bk or Xk). By ANDing select flip-flops with the j and k octal digit translations, specific registers are selected.

Determination of whether or not the desired registers are reserved is made by looking at the content of the XBA reservation list, but not directly. Each functional unit has 4-bit Q designators which, when an instruction is issued to the scoreboard, receive the contents of the XBA slot associated with the desired source operand registers. For example, the following instruction sequence causes a second order conflict:

$$F X 5 = X3 * X2$$

$F X 6 = X2 + X5$

The Multiply I unit reserves X5 by placing a code of  $06_{(8)}$  in the X5 slot of the reservation list. Assuming that no other instructions have been issued, no other reservations exist when the Add instruction is issued. Since the Add unit wished to read X2 and X5, it transfers to its Qj and Qk designators the content of the X2 and X5 slots, respectively. At this point, the Add Qj designator equals  $00_{(8)}$  and Qk equals  $06_{(8)}$ . In essence, this tells the Add unit that its j operand (X2) is not reserved by the Multiply I unit. Since a functional unit does not begin calculation until after it can read both operands, the Add unit must wait until Multiply I returns its result to X5.

Associated with each functional unit are flip-flops, called Read Flags, which when set, indicate that the desired operand (s) can be read. The Add unit has two Read Flags, one for the Xj operand and one for Xk. Read Flags can be set in two ways, both of which result from translating the Q designators.

- 1) If Q = 00(8), a Read Flag can be set since the desired operand is not reserved.

- 2) If  $Q \neq 00_{(8)}$ , a Read Flag cannot be set until the functional unit, whose code is in Q, has completed its calculation and returned its result to the result register. Completion of a functional unit's operation is indicated by a signal called Release (discussed in detail under third order conflicts)

In the above example, the Add unit's Xj Read Flag is set immediately, since Qj=0. The Xk Read Flag is set when the Release for Multiply 1 occurs, since Qk translates as  $06_{8}$ . Each possible non-zero Q translation is tied to the "Release" signal for the associated functional unit, so it is possible to set a Read Flag by any translation of Q, ANDed with the associated "Release" signal or, by  $Q=00_{8}$ .

Once both Read Flags are set, it is necessary to send the functional unit its operands and to send a Go signal to the unit, allowing it to begin its calculation. The Go F.U. signal is sent as soon as both Read Flags are set. This signal starts the functional unit timing chain. At the same time, the source register selection codes are sent (by a Go Read signal) to Register Exit Control to gate the proper operands to the unit. These codes are obtained from the F designators associated with each unit. These are 3-bit designators which are used to remember the source and result operand register numbers. They also are set when the scoreboard is issuing an instruction. In the above example, once both Read Flags are set, the content of the Fj and Fk designators of the Add unit are sent to Register Exit Control and will allow X2 and X5 to be gated to the Add unit. The Read Flags are cleared during the minor cycle after both are set. Set Read Flags then, indicate that an operand is waiting to be read.

Thus, the general second-order conflict case delays the start of a functional unit until both source operands can be read. Some special cases exist, which are discussed in detail in the logic analysis sections of this manual. At this point, it is appropriate to understand the general case.

#### THIRD-ORDER CONFLICTS

The possibility of third-order conflicts occurs when a functional unit has generated a result and wishes to store in an operating register. If the desired result register is waiting to be read, the unit must wait to store until after the read has occurred.

Whether or not a register is waiting to read is determined by checking the Fj and Fk designators against the associated Read Flags in all the functional units. The result register of a unit is given by the Fi (and, in some cases, Fj) designator of that unit. When a unit requests to store a result, its result register number is checked against the Read Flags and F designators of all other units. If any Read Flag is set AND the associated Fj or Fk designator translation is the same as the Fi designator of the storing unit, a third-order conflict exists. The unit will therefore be prevented from storing until the conflicting unit's Read Flag is cleared. This, of course, occurs once a unit has set both of its Read Flags.

The general sequence in handling third-order conflicts is as follows. First, a unit desiring to store a result sends a Request Release signal to the scoreboard near the end of its calculate time. This signal is then ANDed with an All Clear signal to generate the Release gate, which allows storage of the result. The All Clear is the result of checking all Read Flags with the associated Fj and Fk designators and comparing with the Fi (or Fj) designator (for the result) of the unit requesting release. The Release signal accomplishes several necessary tasks in the scoreboard. It sends a transmit signal to the functional unit to gate the result to the data trunk. It also generates a Go store signal which gates the Fi (or Fj) designator to Register Entry Control to select the desired result register. Release also clears reservations in the scoreboard (i.e. XBA designators, Unit busy flip-flops, etc.) and checks all Q designator translations in the event that a unit is waiting to use this result as a source operand. The Release then, indicates final termination of an instruction, and in essence, removes that instruction from the scoreboard.

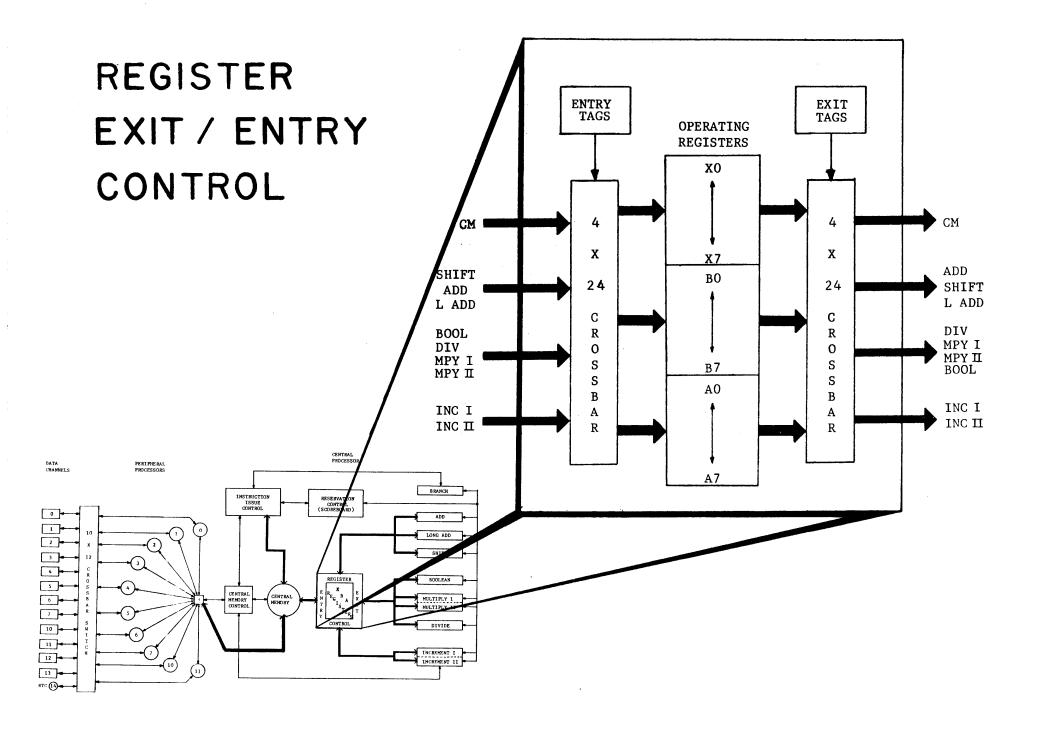

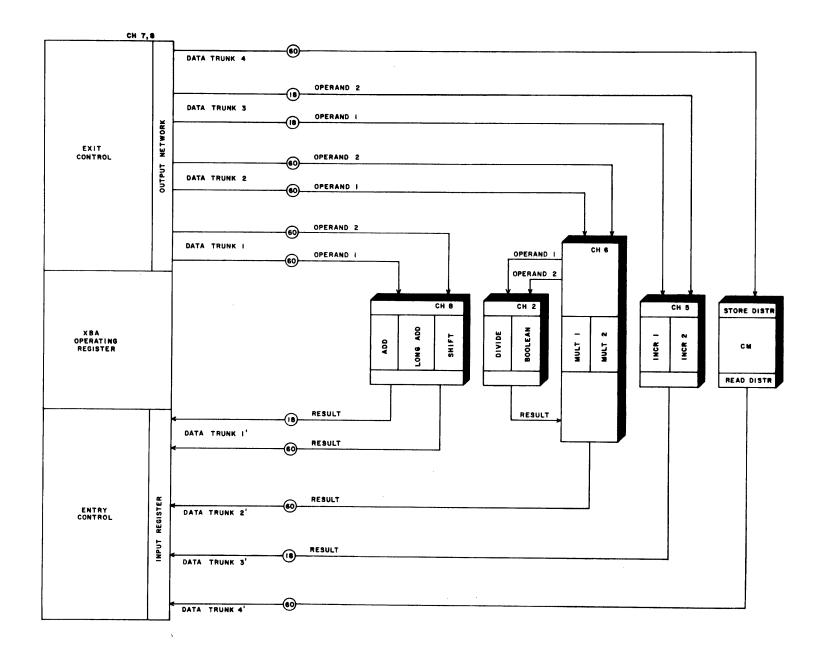

#### REGISTER EXIT/ENTRY CONTROL

As the name implies, Register Exit/Entry Control is the control logic used for gating data into and out of the 24 operating registers. It is in essence, a large translating network which decodes tags sent from the Stunt Box or Scoreboard to enable the transfer of data to and from central memory or the functional units. Figure 1-9 is a block diagram which should be used during the following discussion.

#### ENTRY CONTROL

Entry Control is shown on the left half of Figure 1-9. To the extreme left are the four general sources of information for the X, B and A registers:

- 1) Central Memory

- 2) Data Trunk #1 (Shift, Add and L. Add)

- 3) Data Trunk #2 (Boolean, Divide, Multiply 1 and Multiply 2)

- 4) Data Trunk #3 (Increment 1 and 2)

Data is entered into the operating registers from Central Memory during Exchange Jumps and during the central read operand instructions (5 X 1-5 X 5). Since memory references are involved, all of the gating tags are sent from the Stunt Box and are composed of the lower four bits ( $2^0-2^3$ ) of the Hopper Tag ANDed with the Accept signal for the associated address. In other words, when an Exchange Jump or a Read Operand address is accepted, the four-bit tag is sent from the tag timing chain to Entry Control where it enables the information from Central Memory to the proper X, B, or A register.

Notice that during Read Operand references, the 60-bit operand is first sent into the D register (1 - 5) associated with the X register (1 - 5) which will ultimately receive the information. This is enabled by the Mem  $\longrightarrow$  D signal which results from the simple translation: (tag 11 - 15) (Accept). The operand will be temporarily stored in D, until any third order conflict which may exist is resolved. (A Read Flag may be set for the X register which is to receive the operand from memory). Thus, when the All Clear signal occurs, the D—> X signal is generated and completes the transfer to X.

During Exchange Jumps, new information is entered into A, B and X registers by Hopper tags in the range, 60 - 77. Recall, that tags 60 - 67 enable the exchange of A and B registers, while tags 70 - 77 enable exchanging X registers. The Entry Control Tags, Exchange Jump A, Exchange Jump B and Exchange Jump X refer to the hopper tage 60 - 77 accepted.

A result generated by the Increment units may be entered into X, B or A registers, depending upon the instruction being processed (5X, 6X, or 7X). Thus, three Entry Control Tags are shown for the Increment Data trunk, namely, Go Store Ai, Go Store Bi and Go Store Xi. Recall that Go Store occurs after a functional unit has been released and enables the Fi designator content to Entry Control. Thus, the Go Store tags are generated by the Scoreboard at the completion of an instruction sequence. Note also, that Sign Extension occurs when storing an Increment result (18 bits) in an X register (60 bits).

Results generated by the Boolean, Divide, Multiply 1 or Multiply 2 units are always 60 bits in length and the result register of these functional units is always an X register. Therefore, one Entry Control Tag, namely Go Store Xi is shown for Data Trunk #2. The tag is also generated from the Fi designators of the units on this trunk when the unit is Released by the Scoreboard.

The units on Data Trunk #1, Shift, Add, and Long Add all generate a 60-bit result for X registers, but in addition, the Shift unit may generate an 18-bit result for a Bj register. (For example, during normalize or unpack operations.) Thus two Entry Control Tags are shown for this trunk: Go Store Xi and Go Store Bj. These are also generated by the Scoreboard when a unit releases from the Fi (or Fj in the special shift case) designators.

## EXIT CONTROL

Similar to Entry Control, Exit Control has four general destinations for data from the operating registers:

- 1) Central Memory

- 2) Data Trunk #1

- 3) Data Trunk #2

- 4) Data Trunk #3

The Exit Control Tags are also generated similarly, that is, from the Stunt Box or the Scoreboard.

The Stunt Box generates tags for information to be sent to central memory, specifically, during Exchange Jumps or Central Store Operand instructions (5 X 6 or 5 X 7). During these operations, the lower four bits of the Hopper Tag are sent to Exit Control when the associated address has been Accepted (is not in conflict). The data, which may be A and B register or X register contents, are sent on the memory trunk and will be stored during the write portion of the memory cycle.

For the Increment Data Trunk, four Exit Control Tags are shown in Figure 1-9 since the Increment units may specify an A, B or X register with the j octal and only a B register with the k octal. Thus the four tags, Go Read Xj, Go Read Bj, Go Read Aj, and Go Read Bk are used to gate operands on this trunk.

For Data Trunk #2, all functional units specify only X registers as source operands. Therefore, only Go Read Xj and "Go Read Xk" tags are required.

For Trunk #1, the Add, and L. Add units may specify an Xj or an Xk source register (or both) while the shift unit may specify an Xj or Bk register (or both). Thus the three tags, Go Read Xj , Go Read Bj and Go Read Xk are required for this data trunk.

All Go Read tags are generated by the Scoreboard when both Read Flags for a unit have been set. This enables the Fj or Fk designator to exit control and gates the proper register to the proper trunk.

# CHAPTER II

CENTRAL MEMORY ADDRESS CONTROL

#### CHAPTER II

# CENTRAL MEMORY ADDRESS CONTROL

#### INTRODUCTION

The basic concept of the 6600 computer is parallelism. In the central processor many parallel operations can be in progress, one of which may be accessing of central memory. Sometimes the peripheral processors will be attempting communications with central memory simultaneously with the central processor. This is a simplification of possibilities but points out that some method of orderly distribution of requests for central memory time must be available.

Central Memory is divided into 32 (or 16) independent banks that can be accessed sequentially in an overlapping fashion. This allows memory references every 100 nano-seconds. To make full use of central memory and also to fulfill the parallelism concept, an area of the central processor known as the STUNT BOX exists. It is to this circuitry that all references to central memory must first come. The job of the stunt box is to collect requests for central memory access and to distribute these requests in an orderly fashion.

The 6600 has ten peripheral processors that can request read or write operations in central memory. The peripheral processors can also execute an exchange jump which requires central memory access. The central processor can reference memory for an instruction word or to read and store operands.

Consequently the peripheral and central processors can send requests to the stunt box simultaneously. This presents the necessity for some means of priority within the stunt box and also some method of naming each of the memory requests in order that the data, once acquired, will be distributed correctly. Another factor that must be considered is a means of remembering addresses if the first attempted access is rejected because of a memory conflict.

In general, the stunt box:

- a) allows several simultaneous memory requests.

- b) establishes a priority for issuing addresses to central memory.

- c) issues the addresses to memory at a rate that will make maximum use of the 32 (or 16) independent banks.

- d) remembers addresses that have not been accepted by the memory and must be re-issued.

- e) adds a tag to the addresses to correctly distribute the data.

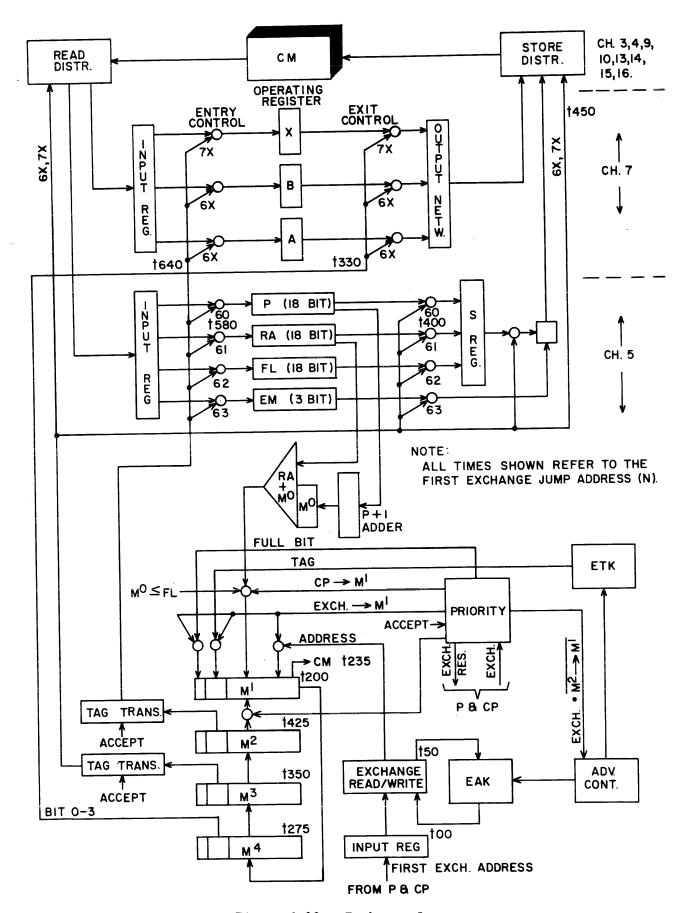

Figure 2-1. Stunt Box Block Diagram

#### STUNT BOX LOGIC ANALYSIS

#### DESCRIPTION

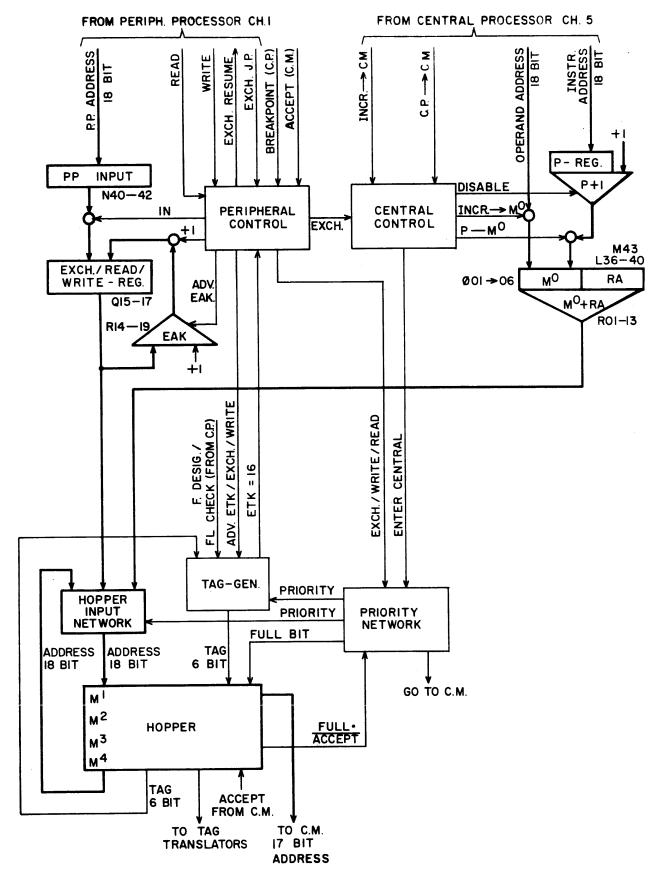

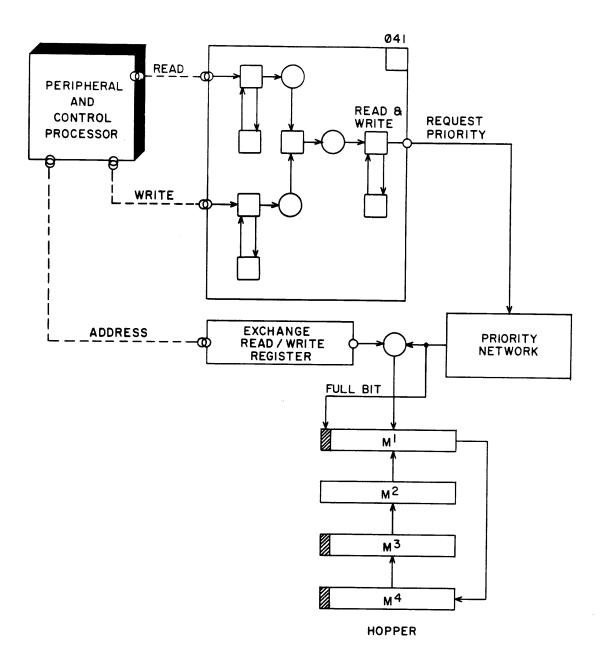

There are two main address flow paths to the hopper  $(M_1)$  and to Central Memory (CM): (Refer to Figure 2-1).

- 1) The PPs supply CM with the write and read addresses for the data-exchange between PPs and CP. The exchange jump addresses are also sent over this line.

- 2) The central processor supplies CM with either operand or instruction addresses. Addresses comming through this path are always added to the content of the Reference Address (RA) Register.

A priority network controls the entry into the hopper  $(M_1)$  from which the addresses are sent to CM. These addresses are also stored and circulated in the hopper, from which (in case of bank conflict) they are re-issued to CM after 300 nanoseconds.

## Peripheral Control

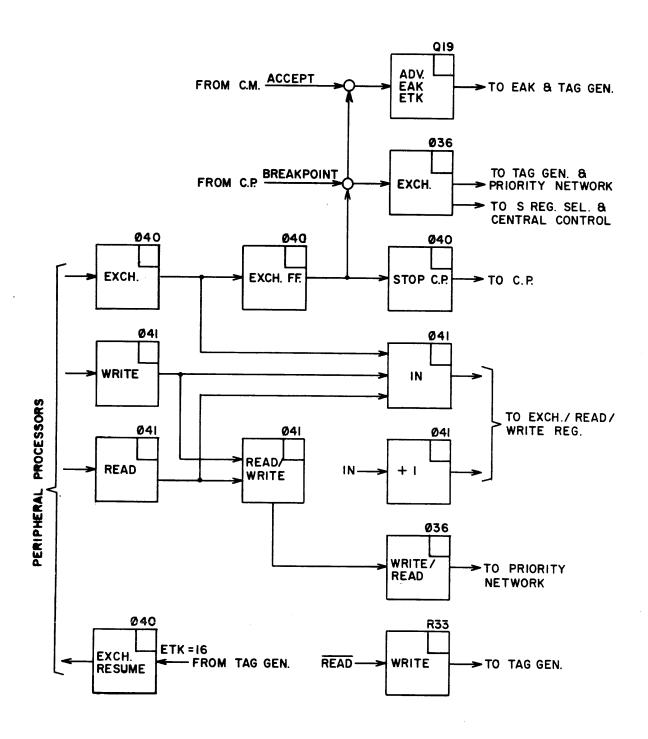

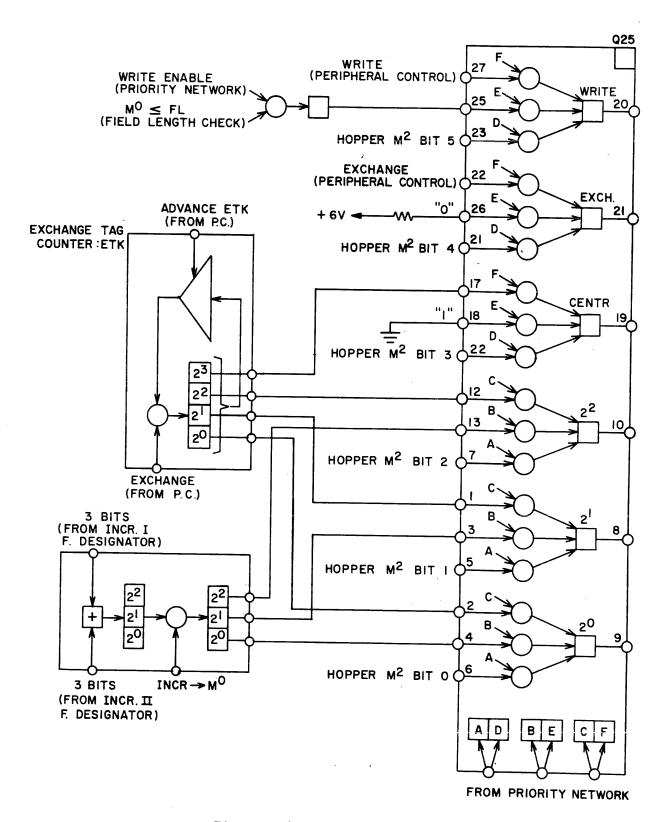

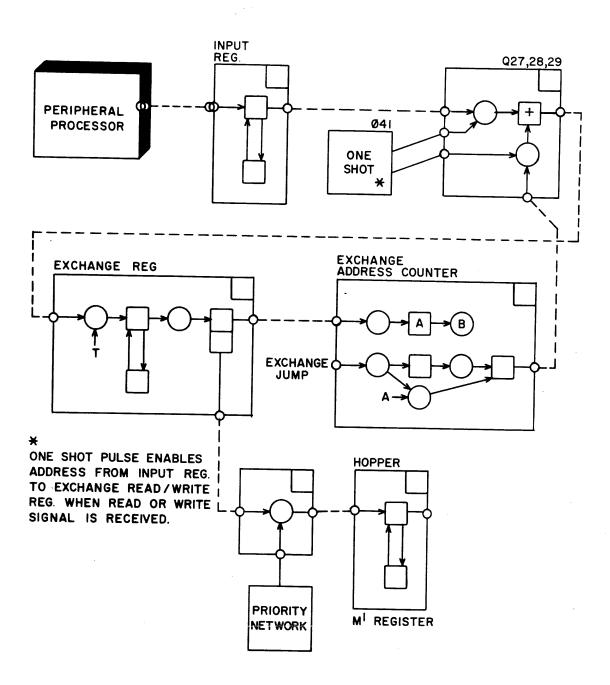

Peripheral Control, for the purposes of this discussion, is a term applied to that section of the central processor that handles addresses and signals from the peripheral processors requesting storage access. (Refer to the block diagram in Figure 2-2)

When the peripheral processors send an address to the stunt box, an accompanying signal informs Peripheral Control whether it is a Read, a Write or an Exchange Jump address. Peripheral Control (PC) then transfers this information to the tag generator to enable the IN-path to the EXCH/READ/WRITE Register. In an Exchange Jump, this signal also stops the central processor: When the :Breakin" signal indicates the central processor and central memory have stopped, it starts Exchange Address (EAK) and Exchange Tag Counters (ETK). The Exchange Address Counter then updates the address in the EXCH/READ/WRITE register for each step of the Exchange process upon receipt of the "accept" from central memory. When the Exchange Tag Counter = 16, Peripheral Control sends an Exchange Resume back to the peripheral processors (Write Resume is sent back from central memory chassis 2, and Read Resume from chassis 4).

# Central Control

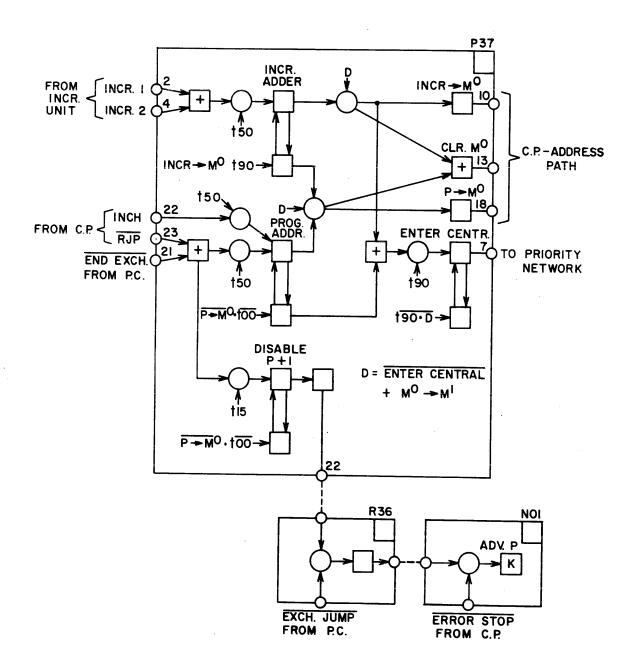

Central Control, for the purposes of this discussion, is a term applied to that section of the central processor that handles addresses from the central processor requesting access to central memory for instructions or operands. Central Control controls entry into MO and requests entry (via the priority network) into M1. Refer to

Figure 2-2. Peripheral Control Block Diagram

Figure 2-3. Simplified Central Control Network

## Figure 2-3)

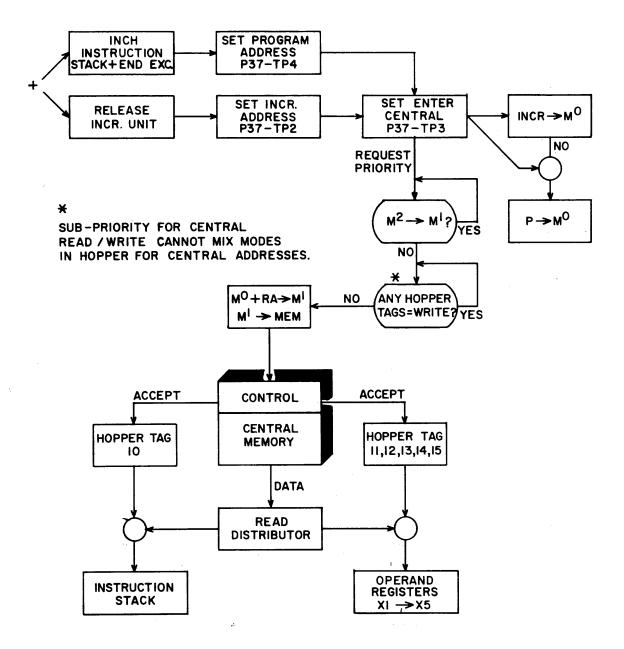

When an <u>operand address</u> is sent by one of the two increment units, the INCREMENT ADDRESS FF on P37 will set and the entry signal into M<sub>0</sub> is enabled as soon as M<sub>0</sub> is empty. Simultaneously, the ENTER CENTRAL FF sets indicating to the priority network that a central processor address is waiting to enter central memory.

When a program address is ready in P, the PROGRAM ADDRESS FF sets, enabling the P  $\longrightarrow$  M<sub>O</sub> signal if M<sub>O</sub> is empty and if no operand address is waiting. This signal also sets the ENTER CENTRAL FF.

If a Return Jump instruction or an End Exchange signal occurs, the DISABLE P+1 FF sets and the program address in P passes through the P-incrementor without being incremented. This does not affect the ADVANCE P gates on N37-N39.

## PRIORITY NETWORK

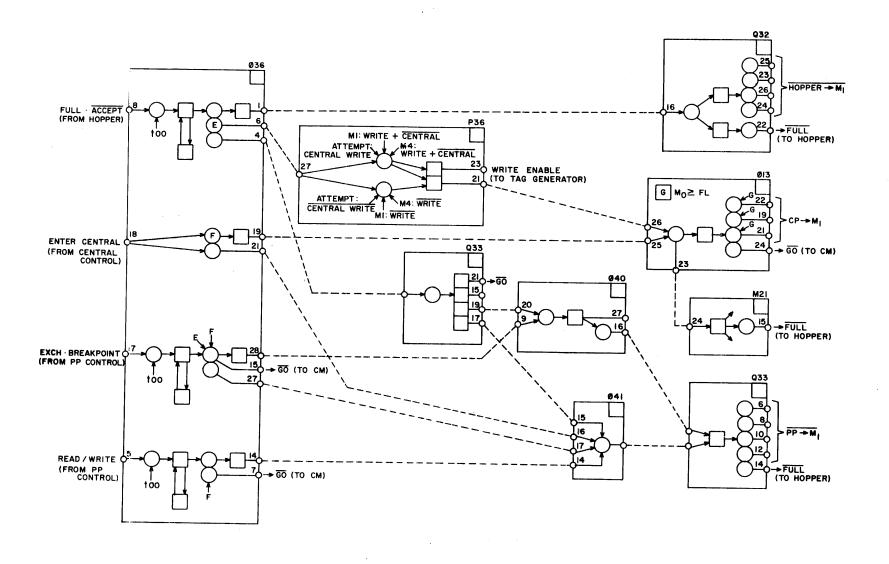

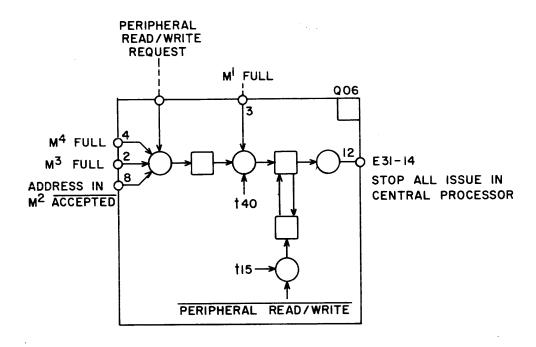

The priority network (Figure 2-4) controls inputs to the hopper by sequencing entry to the hopper when more than one address attempts to enter at the same time.

The fixed order of priority is as follows:

- 1) Address from Hopper

- 2) Addresses from the Central Processor

- 3) Addresses from the Peripheral Processors

An address from the hopper is given first priority since it is an un-accepted address resulting from a central memory bank conflict.

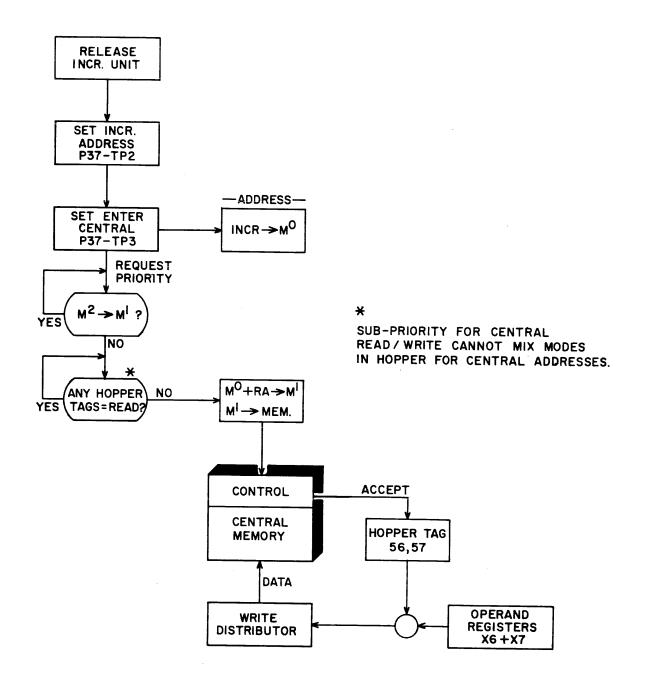

Addresses with second priority are from the central processor (i.e.,  $M^0$ ). Since, for the central processor, storage modes cannot be mixed in the hopper, the Read or Write tags are examined before priority is granted. In attempting a Read, no Write address is allowed in  $M^1$  or  $M^4$ . In attempting a Write, no Read address is allowed in  $M^1$  or  $M^4$ . If modes are mixed, priority is not granted and entry of the address into the hopper is delayed until central memory has accepted those addresses and modes are no longer mixed.

Addresses from the peripheral processors are assigned lowest priority. Thus, peripheral read and write operations from and to central memory may have to wait for hopper and central processor addresses. An important exception occurs during an Exchange Jump. An Exchange Jump a) stops the central processor, and b) inhibits communications between the peripheral processors and central memory. In this case, exchange jump addresses are the only addresses entering the hopper.

Figure 2-4. Priority Network

With each address sent to the hopper, a Full bit is generated, (to indicate the hopper register contains a usable address a tag and a Go signal is sent, along with the address, from  ${\tt M}^1$  to central memory.

The hopper input network is diagrammed in Figure 2-5. Three gates for each of the 18 address bits accommodate the three possible input paths to the hopper. Entry via these gates is controlled by the priority network.

Figure 2-5. Hopper Input Network

## TAG GENERATOR

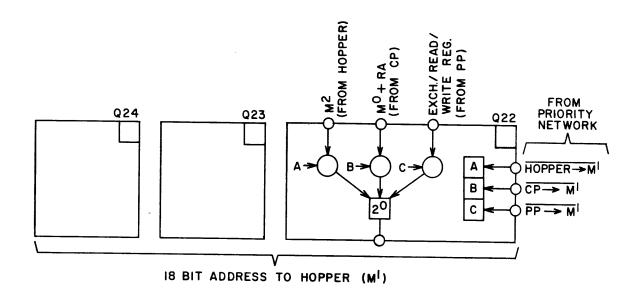

When an address enters the hopper, a six-bit tag is appended to control the address and data flow. Depending on the source of the addresses, these tags are generated from three sources: (Refer to Figure 2-6)

- An un-accepted address resulting from a bank conflict retains the tag that was generated when the address first entered the hopper.

- 2) An operand or instruction address from the central processor gets its tag from the translation of the F designators of the increment units or from the central processor (in case of exit mode stops or return jumps) and from the priority network.

Figure 2-6. Tag Generator

3) Addresses from the peripheral processors obtain their tags from Peripheral Control. The Exchange Tag Counter (ETK), which controls the execution of the exchange jump, generates the tags for all addresses of the exchange jump package.

#### HOPPER

The hopper consists of four registers ( $M^1$ ,  $M^2$ ,  $M^3$ , and  $M^4$ ) each capable of holding an 18-bit address, a 6-bit tag, and a single Full bit. ( $M^2$  is an exception and does not have a Full bit). (A block diagram of the hopper is shown in Figure 2-8)

An address is sent to central memory from hopper register  $M^1$ . Hopper registers  $M^2$  -  $M^4$  store the address in case it must be re-issued because of a bank conflict. If the address is accepted by central memory, it drops out of  $M^2$ .

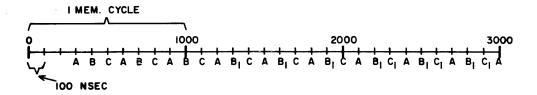

In the case of bank conflict, the priority network gates the un-accepted address from  $M^2$  back into  $M^1$  every 300 nanoseconds, until it is accepted by central memory. An address can be accepted only if the specified bank is free at the time the address is in  $M^1$ . Otherwise, it is possible for another address to request access to the same bank and tie it up for a memory cycle. Figure 2-7 shows possible waiting times in the hopper for worst cases of bank conflict.

The six tag bits travel through the hopper with each address. (The hopper serves as a delay line for the tag.) This line is extended by two additional registers (see Figure 2-8) In each step, the tag controls address and data flow.

Hopper registers  $M^1$ ,  $M^4$ , and  $M^3$  have Full bits associated with the address. The purpose of the Full bit is to indicate to the priority network that the address must be reissued to central memory if no accept is returned. Note that the Full bits also are sampled to stop the central processor (Figure 2-8) before intiating an exchange jump (Break IN).

Figure 2-7. Hopper Waiting Time for Bank Conflicts

Figure 2-8. Hopper

The Hopper can contain a maximum of 3 addresses. An address must be in M1 at the time the memory cycle for its bank finished so that it can be accepted by memory, otherwise a bank conflict occurs. The longest time an address will have to wait to be accepted in memory is when the address enters M1 300 ns after the memory cycle started.

Example: Assume that all 3 addresses in the Hopper need the same bank, then at t=1000, address B is accepted and a new address B<sub>1</sub> can enter the Hopper, at t=2000 address C and at t=3000 address A will be accepted. (See timing diagram.)

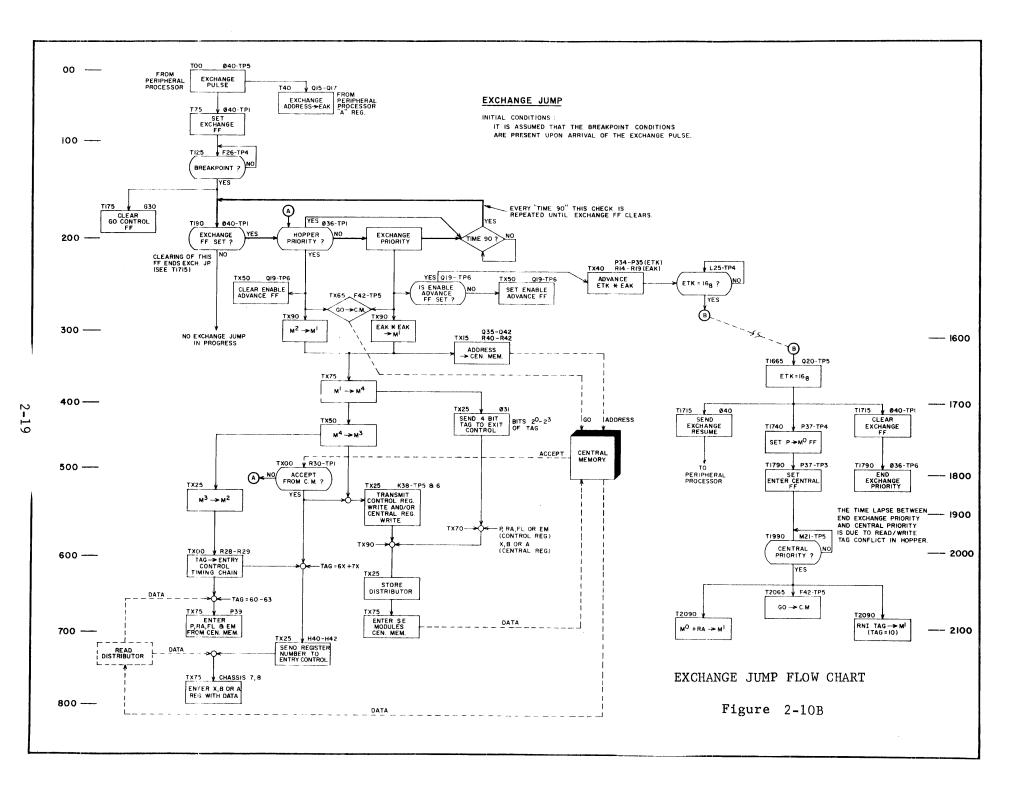

#### EXCHANGE JUMP

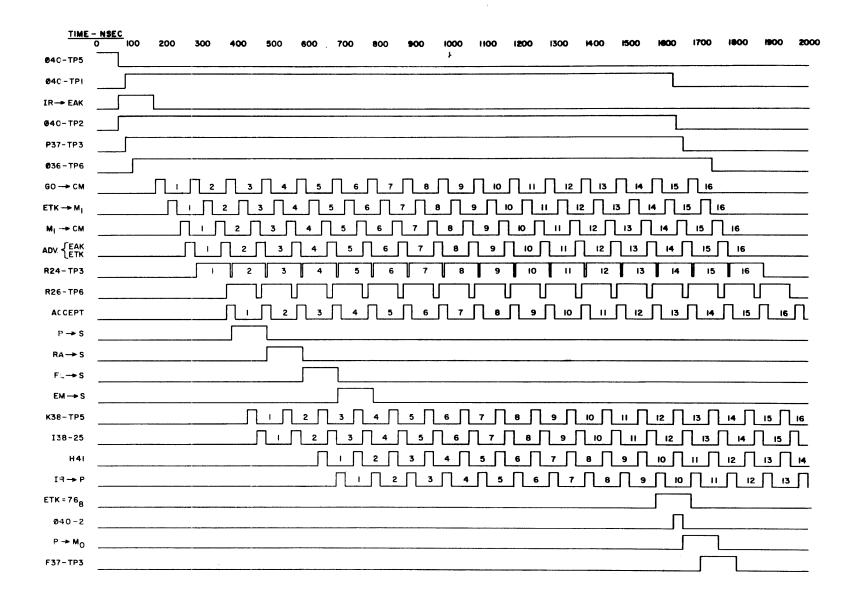

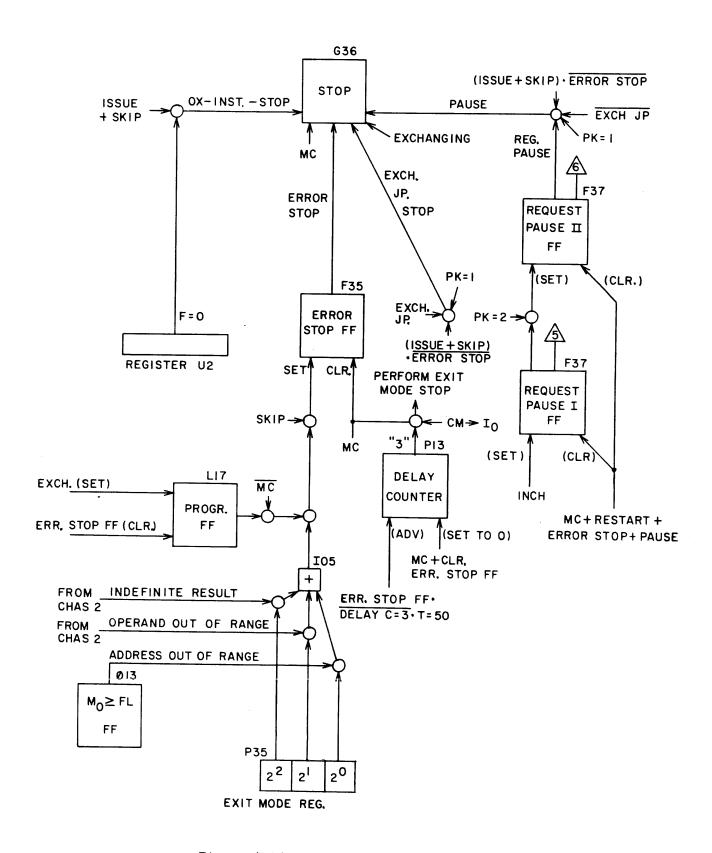

As an aid in following the somewhat detailed discussion which follows, refer to the central processor diagrams, the timing diagram in Figure 2-9 and the Exchange Jump diagram in Figure 2-10.

The following discussion assumes the Exchange Jump Package (see Reference Manual) is stored in Central Memory starting at address N. To start the Exchange Jump, a Peripheral & Control Processor will send an Exchange Jump pulse together with the 18 bit address N to the Stunt Box.