## OLD EDITION

SITE COPY: CONTROL DATA ENGINEERS

UNIVERSITY OF ADELAIDE

VOLUME II

PRELIMINARY EDITION

SECTION 7.2

SHIFT

Functional Units

| The statement of the st |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| range - 1 - 1 - 1 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The second secon |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| )<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### SHIFT FUNCTIONAL UNIT

### 7.2.1 INTRODUCTION

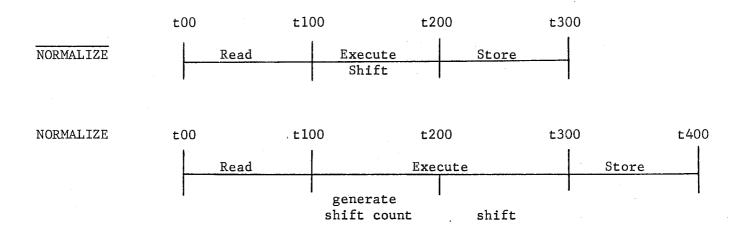

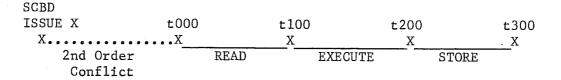

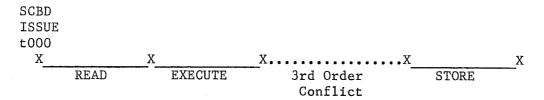

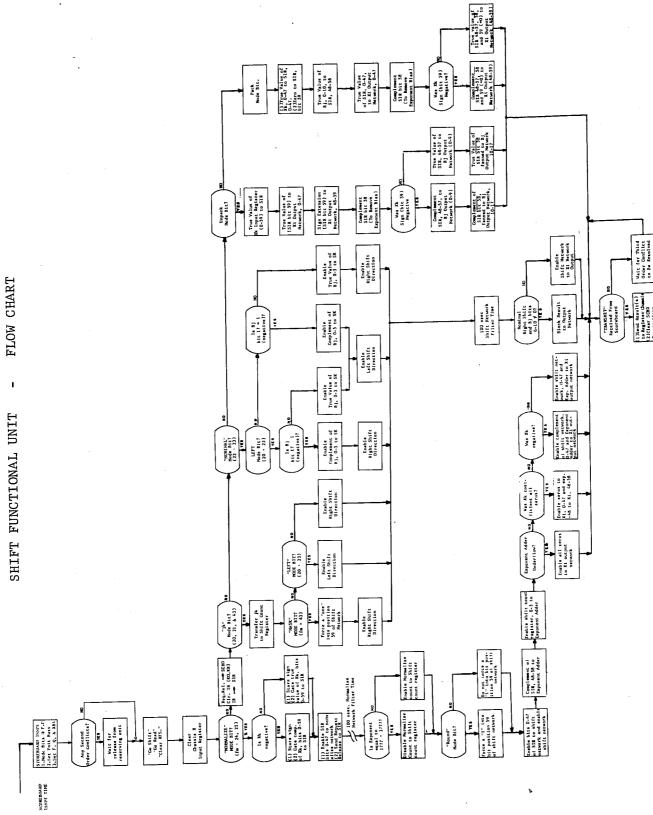

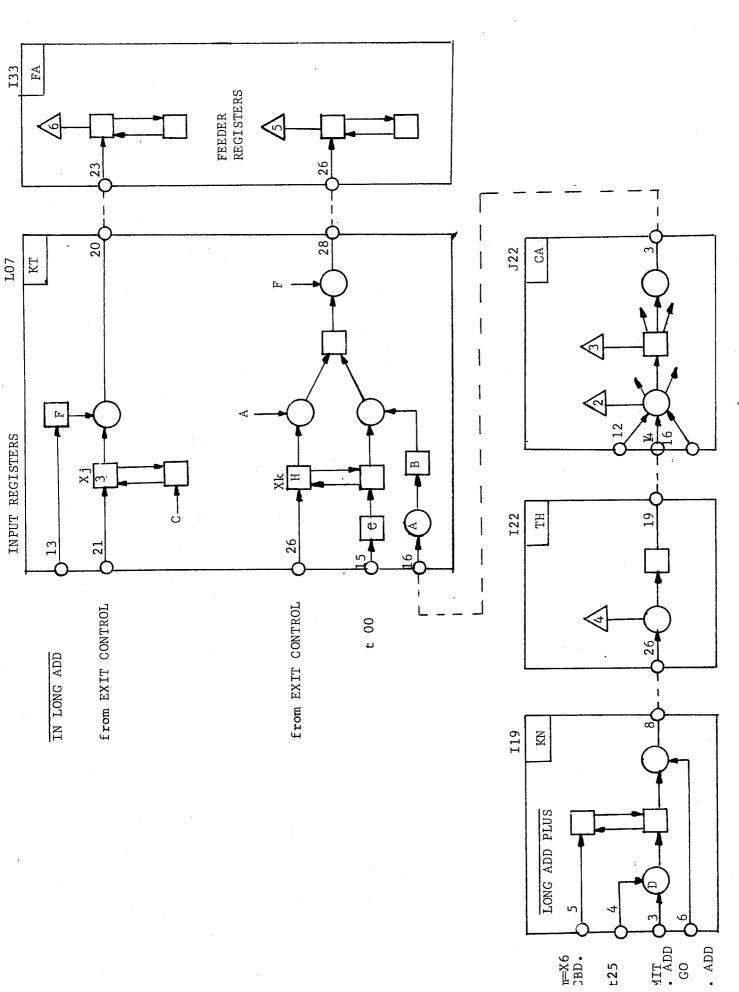

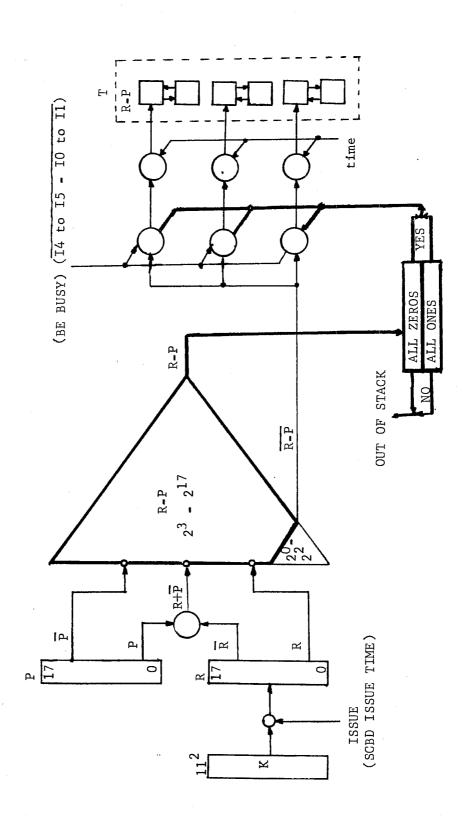

The Shift Functional Unit performs shift, normalize, round, pack, unpack, and mask operations as required by instructions 20 through 27 and 43. The functional unit time is 400 nanoseconds for the normalize instructions (24 and 25) and 300 nanoseconds for any of the other shift operations. The time difference arises because during normalize, a shift count must be generated by the Normalize Network before shifting of the coefficient takes place. The breakdown of the functional unit time into Read, Execute, and Store cycles will then differ as follows:

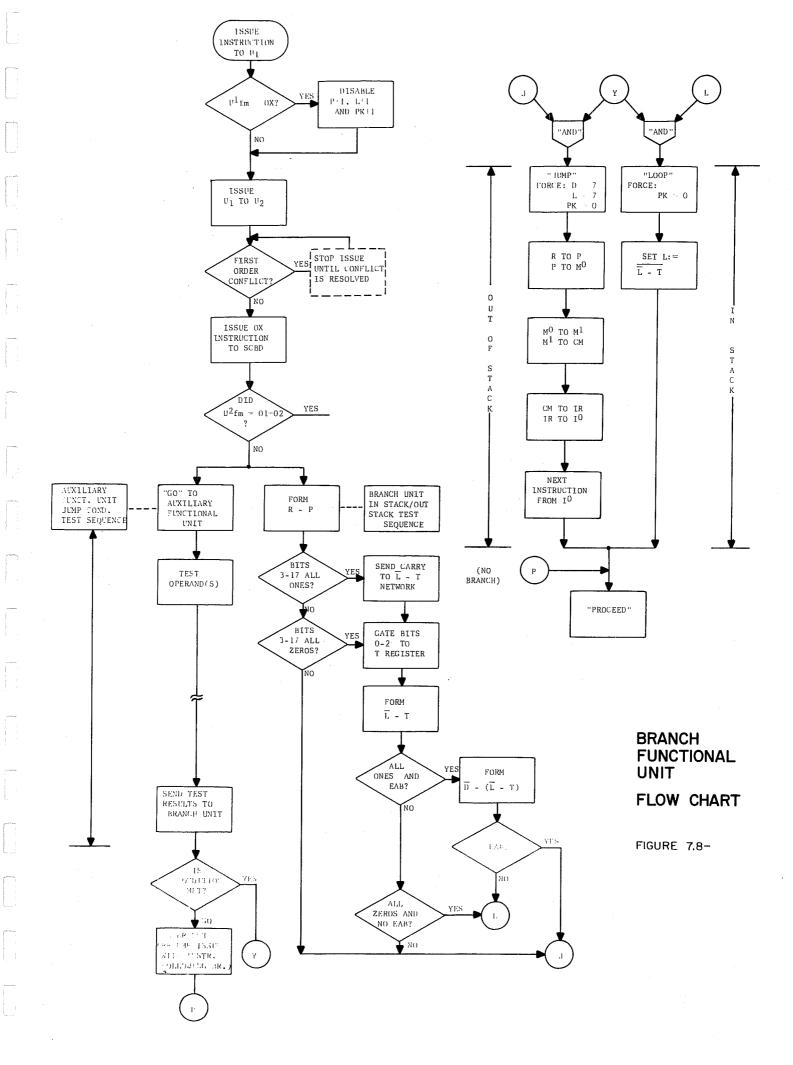

FIGURE 7.2.1

The Shift Unit shares data trunk number 1 with the Add and Long Add Units. It holds second priority on the Read Operand trunk and first priority on the Result trunk. The Unit may select operands from registers Xk, Xi, or Bj and may designate a result register of Xi and/or Bj. Also, the six bits, jk, may be used to specify a shift count - these bits are unconditionally sent to the Shift Unit each minor cycle and are used only if required by the instruction (used by instructions 20, 21, or 43).

The Shift Unit follows the functional unit principles discussed in the Boolean chapter (Section 7.1) in that it uses mode bits and a timing chain to select and sequence the required operations. In the standard manner, it is initiated with a "Go" signal from the scoreboard and terminates its operation (Clears its Busy flipflop and transmits its result(s))upon being released by the scoreboard. It is on the other hand, a somewhat more complex unit because more intricate and varied functions are defined by its instruction list.

The main component of the Shift Unit is of course the Shifting Network, which is a 60-bit, 6-rank shifter that operates in nearly the same manner as the Peripheral Processor shift network. The six ranks enable shifts of 1, 2, 4, 8, 16, or 32 places in either the left or right direction. Shift direction and magnitude are determined by two circuits, Shift Direction Control and the Shift Count Register (SK). Shift Direction Control will determine and enable shift direction (left or right) by checking the mode bits of the Shift Unit.

The Shift Count Register contains six-bits each of which conditions one rank of the shift network. (Bit  $2^5$  conditions the 32 place shift rank, bit  $2^4$  the 16 place rank, etc.) A rank is enabled if its corresponding bit in SK is set, and disabled if that bit is a zero. The maximum shift count is thus  $77_{(8)}$  or  $63_{(10)}$  places (when all bits of SK are set.).

The shift count may come from any one of three sources, depending upon the instruction being executed; from 1) the six bits, jk, 2) the lower six bits of Bj (during nominal shifts), or 3) the Normalize Network which generates the shift count required to normalize a given coefficient. Another component of the Shift Unit to be discussed is the Bj Ones Test Network. During Nominal Right shifts, this network looks for any "one" in bit positions 6 through 10 of

Bj. If a one if found, the result of the shift network is not enabled to the shift network; the result is thus an all zero coefficient. To understand the reason for this circuit, consider that if any one of bits 6 through 10 is set, a right shift should result in an all zero coefficient (right shifts are by nature "end-off" and the shift count is greater than 63<sub>10</sub>). If the network was absent, an erroneous, non-zero coefficient would be generated for all cases where Bj bits 0 through 5 gave a magnitude of less than 64<sub>8</sub> (since these six bits would unconditionally be used as the shift count). The Ones Test Network then guarantees an all zero coefficient for the case illustrated. The final component of the shift unit to be discussed is the Exponent Adder. It is used during Normalize to subtract the normalize shift count from the original operand (Xk) exponent. This insures that the normalized number is of the same value as the original. Further analysis of the components mentioned here will be found on the later pages of this section. First, the Shift Unit instructions and data flow are discussed.

### 7.2.2 INSTRUCTION LIST

Data paths for the following instructions may be seen by referring to Block

Diagram #1, Figure 7.2-2. The expressions in parenthesis following the instruction names are the ASCENT symbolic codes.

20 SHIFT Xi LEFT jk places (LXi jk)

DEFINITION: This instruction shifts the 60-bit word in X register i left circular jk places. The 6-bit shift count, jk, allows a complete circular left shift of X register i.

DATA FLOW: The X Input Register is transferred to the Shift Input Register (SIR) and the jk Input Register to the Shift Count Register (SK). The gates for the shift network are controlled by the SK register and the shift direction translation. The output of the shift network is gated directly to the chassis line drivers.

21 SHIFT Xi RIGHT jk places (AXi jk)

DEFINITION: This instruction shifts the 60-bit word in X register i right jk places. The shift is end-off with sign extension.

DATA FLOW: Same as the 20 instruction.

SHIFT FUNCTIONAL UNIT BLOCK DIAGRAM #1 (for instructions 20, 21, 22, 23, or 43)

FIGURE 7.2-2

- 22 SHIFT Xk NOMINALLY LEFT Bj places to Xi (LXi = Bj, Xk)

DEFINITION: This instruction shifts the 60-bit word in X register k

the number of places specified by the low-order six bits (0 5) of

B register j and places the result in X register i. If Bj sign

(bit 17) is positive, the shift is left circular; if Bj sign is

negative, the shift is right (end-off with sign extension).\*

DATA FLOW: The X Input Register is transferred to SIR and the lower

six-bits of Bj Input Register to SK (complemented if B register j

sign is negative). The gates for the shift network are controlled

by the SK register and the shift direction translation. The specified

shift direction is reversed if B register j sign is negative. The

output of the shift network is gated directly to the chassis line

drivers.

- 23 SHIFT Xk NOMINALLY RIGHT Bj places to Xi (AXi = Bj, Xk)

DEFINITION: This instruction shifts the 60-bit word in X register k

the number of places specified by the low-order six bits of B register

j and places the result in X register i. If Bj sign (bit 17) is

positive, the shift is right (end-off with sign extension);\* if Bj

sign is negative, the shift is left circular.

DATA FLOW: Same as the 22 instruction.

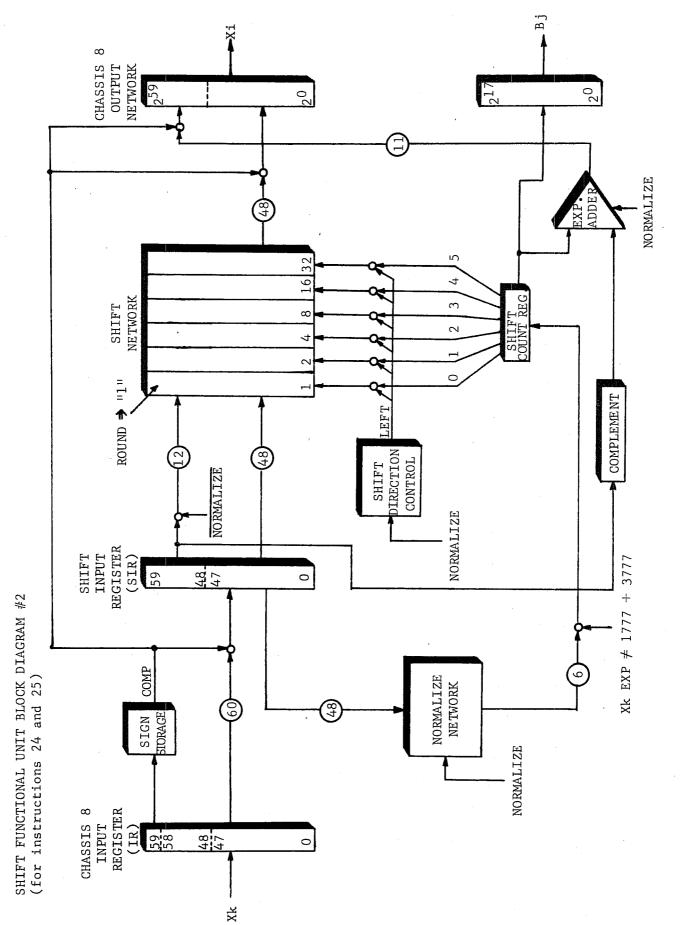

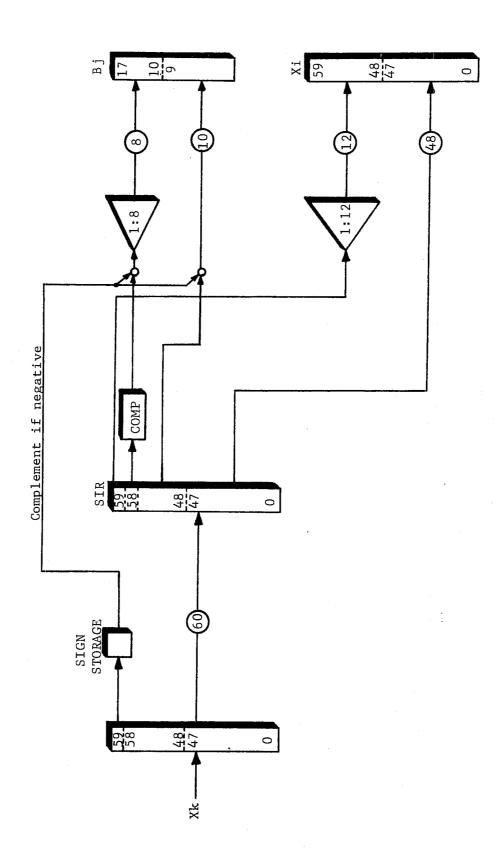

Data paths for the following instructions may be seen by referring to Block Diagram #2, Figure 7.2-3

<sup>\*</sup>The Bj Ones Test Network checks bits 6-10 of B register j during

22 and 23 instructions. If any bit is a one during nominal right

shifts, all zeros are sent to Xi.

FIGURE 7.2-3

DEFINITION: This instruction normalizes the floating-point quantity in X register k and places it in X register i. The number of shifts required to normalize the quantity is entered in B register j. A normalize operation may cause underflow, in which case both exponent and coefficient will be cleared; the normalize count is still entered in B register j. Normalizing a zero coefficient reduces the exponent by  $48_{10} \ (60_8)$ . If Xk is in infinite or indefinite form, it is sent out in tact and the normalize count is sent out as zero.

DATA FLOW: The X register sign bit is stored in a flip-flop to control data flow, and the X Input Register is transferred to SIR (complemented if Xk sign is negative). Bits 0 through 47 feed the normalize network which determines the number of zeros from bit 47 to the left-most "1" of the coefficient. The output of the normalize network (the normalize shift count) is gated to the SK register which, with the shift direction translation (always LEFT during normalize operations), controls the gates for the shift network. The transfer of the normalize network to SK is disabled if Xk exponent equals 1777 or 3777. The output of bits 0 through 47 of the shift network are gated (complemented if Xk sign was negative) to the chassis line drivers. The complement of the exponent portion of SIR and the true value of SK feed the exponent adder where the normalize shift count is subtracted from the exponent portion of SIR. The difference is the exponent portion of the normalized number and is gated directly to the chassis line drivers.

### 25 ROUND and NORMALIZE Xk in Xi and Bj (ZXi, Bj = Xk)

DEFINITION: This instruction performs the same operation as instruction 24 except that the quantity in X register k is rounded by  $\frac{1}{2}$  if that quantity is shifted. (It would not be shifted if the original quantity was already normalized.) A normalize operation may cause underflow in which case both exponent and coefficient will be cleared. Normalizing a zero coefficient places the round bit in bit 47 and reduces the exponent by  $48_{10}$  ( $60_8$ ). If Xk is in infinite or indefinite form, it is sent out in tact and the normalize count is sent out as zero.

DATA FLOW: Data paths are the same as the 24 instruction with the addition of the round operation. With "Round" specified, a one bit is forced in position 59 of the shift network. As in the 24 instruction, LEFT shift is specified. If the coefficient is shifted, the round bit will be pulled around below the least significant bit, thus adding a ½ round bit.

Data paths for the following instruction may be seen by referring to Block Diagram #3, Figure 7.2-4.

### 26 UNPACK Xk to Xi and Bj (UXi, Bj = Xk)

DEFINITION: This instruction unpacks the floating point quantity in X register k and sends the 48-bit coefficient with sign extended in the upper 12-bits to X register i. The 10-bit exponent (unbiased, sign extended, and represented in true one's complement) is sent to B register j.

DATA FLOW: The X register sign bit is stored in a flip-flop to control data flow and the X Input Register is transferred to SIR. Bits 0-47 are sent directly to Bits 0-47 of the Xi output network. The coefficient sign is extended to bits 48-59 through a fan-out. Bits 48-57 of SIR

FIGURE 7.2-4

are sent directly to bits 0-9 of the Bj output network - complemented if Xi sign (bit 59) is negative. To remove the exponent bias and provide proper sign extension, the complement of SIR bit 58 is fanned-out to bits 10-17 of the Bj output network. These 18 bits will be complemented at the Bj output network if Xk sign (bit 59) is negative.

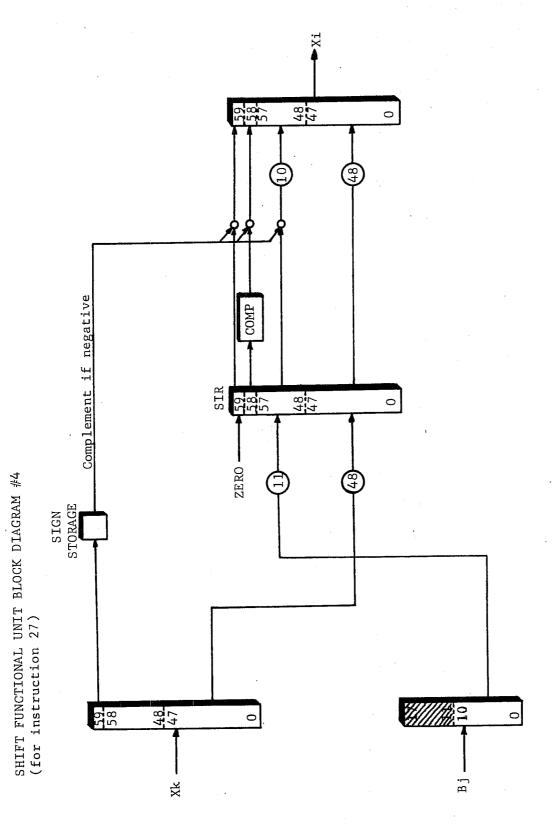

Data paths for the following instruction may be seen by referring to Block Diagram #4, Figure 7.2-5.

27 PACK Xi from Xk and Bj (PXi = Bj, Xk)

DEFINITION: This instruction packs a floating point quantity in X register i. The coefficient is obtained from the lower 48 bits of X register k and the exponent from the lower 10 bits of B register j. Bias is added to the exponent during the pack operation.

DATA FLOW: The X register sign bit is stored in a flip-flop to control data flow and bits 0-47 of the X input Register are transferred to bits 0-47 of SIR. Bits 0 through 10 of B register j are transferred to bits 48-58 of SIR. The setting of SIR bit 59 is disabled during PACK operations. The word now assembled in SIR is gated to the Xi data trunk. SIR bits 0-47 are transferred in true form. Bits 48-59 (bit 58 is complemented out of SIR to remove bias and bit 59 was made a "zero") are transferred in true form if Xk sign is positive; in complement form if Xk sign is negative.

Data paths for the following instruction may be seen by referring to the block diagram on page .

### 43 FORM jk MASK in Xi (MXi jk)

DEFINITION: This instruction forms a mask in X register i. The 6-bit quantity jk defines the number of ones in the mask as counted from the highest order bit in X register i. If jk equals zero, X register i will equal all zeros.

DATA FLOW: The SIR is cleared, the jk count is transferred to the SK register, and a right shift is translated. The mask mode will cause a negative sign to be extended during the right shift. The overall effect is that an all zero operand is right shifted jk places with ones forced as sign extension. Thus, a mask jk places long is formed at the output of the shift network. This output is gated to the Xi line drivers.

### 7.2.3 MODE BITS

The following chart, Figure 7.2-6, summarizes the nine instructions that use the Shift Unit.

| CODE | NAME SHIFT COUNT                       |                      | SOURCE    | RESULT    | TIME<br>(NSEC) |

|------|----------------------------------------|----------------------|-----------|-----------|----------------|

| 20   | Shift Left                             | jk                   | Xi        | Xi        | 300            |

| 21   | Shift Right                            | jk                   | Xi        | Xi        | 300            |

| 22   | Shift Left<br>Nominally                | Bj(bits 17, 5-0)     | Xk        | Xi        | 300            |

| 23   | Shift Right Bj(bits 17, 5-0) Nominally |                      | Xk        | Xi        | 300            |

| 24   | Normalize<br>Network                   |                      | Xk        | Xi and Bj | 400            |

| 25   | Round and<br>Normalize                 | Normalize<br>Network | Xk        | Xi and Bj | 400            |

| 26   | Unpack None                            |                      | Xk        | Xi and Bj | 300            |

| 27   | Pack                                   | None                 | Xk and Bj | Xi        | 300            |

| 43   | Mask                                   | jk                   | None      | Xi        | 300            |

FIGURE 7.2-6

Note that two instructions (20 & 21) specify Shift jk, two (20 & 22) specify Shift Left, two (21 & 23) specify Shift Right, two (22 & 23) are Nominal Shifts, two (24 & 25) are Normalize instructions, and there is one each of Mask (43), Round (25), Pack (27), and Unpack (26). With this information, the following list of Mode Bits used by the Shift Functional Unit can be derived.

| MODE BITS                                              | fm (INSTRUCTION)                                     |

|--------------------------------------------------------|------------------------------------------------------|

| Shift jk Shift Left Shift Nominal Mask Normalize Round | 20 & 21<br>20 & 22<br>22 & 23<br>43<br>24 & 25<br>25 |

| Pack<br>Unpack                                         | 27<br>26                                             |

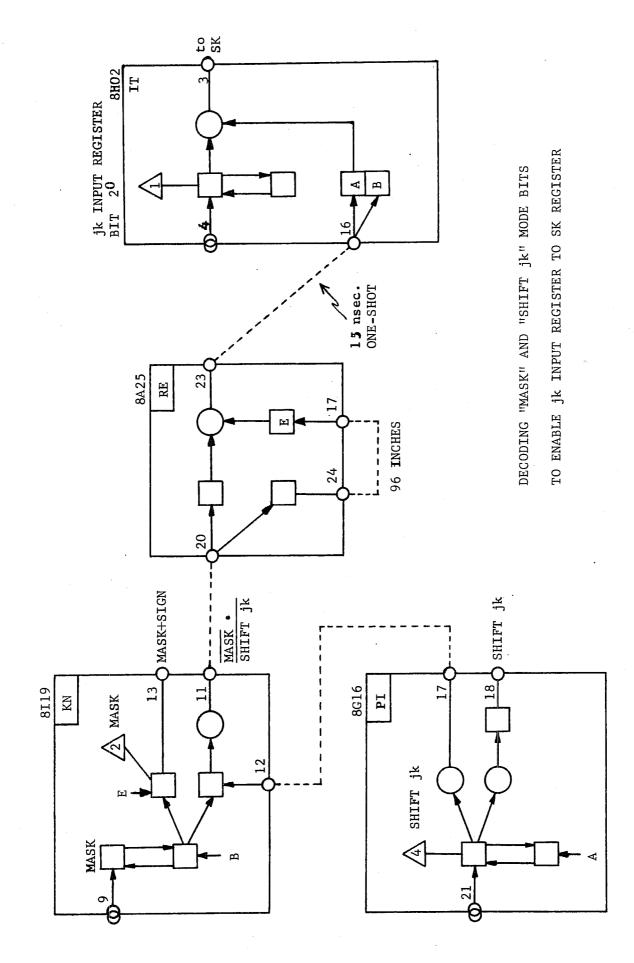

The Mode Bits are translated in the same manner as the Boolean mode bits were, that is, the bits are ANDed, ORed, and fanned out to enable the various operations required by each instruction. Figure 7.2-8, for example, shows the decoding of the "Mask" and "Shift jk" mode bits to enable the six bits, jk, to the Shift Count Register (SK) during instructions 20, 21, and 43. The Mode Bit translators, transmitters, and receivers are shown on sheet 110 of the Shift Functional Unit Customer Engineering Diagrams. Complete translations may be made by referring to the Chassis 8 Wiring Tabs. Figure 7.2-7 summarizes the Mode Bits and the associated instructions.

| Code | Name                     | Shift<br>jk | Left<br>Shift | Shift<br>Nom | Mask | Norm. | Rnd. | Pack | Unpack |

|------|--------------------------|-------------|---------------|--------------|------|-------|------|------|--------|

| 20   | Shift Left               | Х           | Х             |              |      |       |      |      | į      |

| 21   | Shift Right              | Х           |               |              |      |       |      |      |        |

| 22   | Shift Left<br>Nominally  |             | Х             | Х            |      |       |      |      |        |

| 23   | Shift Right<br>Nominally |             |               | X            |      |       |      |      |        |

| 24   | Normalize                |             |               |              |      | Х     |      |      |        |

| 25   | Round and<br>Normalize   |             |               |              |      | Х     | х    |      |        |

| 26   | Unpack                   | -           |               |              |      |       |      |      | Х      |

| 27   | Pack                     |             |               |              |      |       |      | Х    |        |

| 43   | Mask                     |             |               |              | Х    |       |      |      |        |

FIGURE 7.2-7

FIGURE 7.2-8

### 7.2.4 TIMING CHAIN

As was mentioned in the introduction to this section, (7.2.1) the Shift Unit time duration is 100 nanoseconds longer for Normalize than for Non-Normalize shift class instructions. This occurs because during Normalize, a Shift count must be generated by the Normalize Network of the Shift Unit while for other Shift instructions, the shift count is available at the same time as the operand.

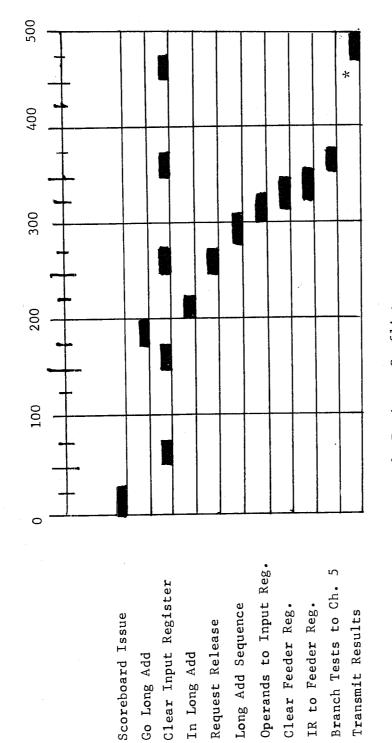

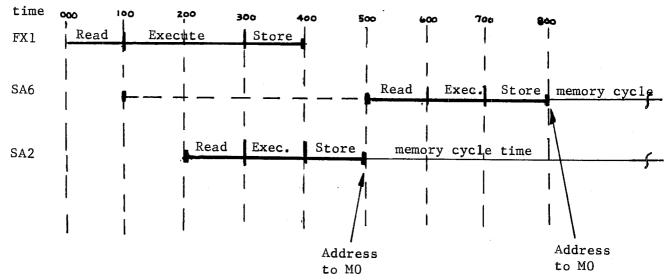

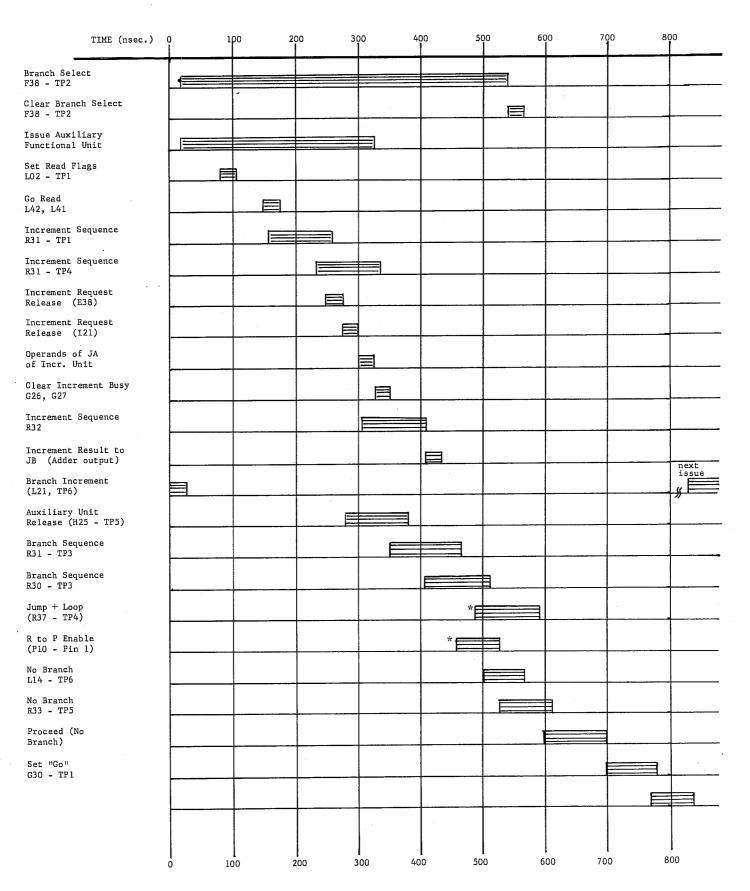

The timing sequence for the Shift unit is shown in Figure 7.2-9 and an explanation of the timing is found on the facing page. The timing sequence assumes that no second or third order conflicts occur. If a second order conflict does occur, the "Go Shift" pulse will be delayed for the duration of the conflict.

If a third order conflict should occur, gating of the result to the register chassis (Transmit Result) will be delayed for the length of the conflict.

Thus, 300 nanoseconds is the Functional Unit time for Non-Normalize instructions; 400 nanoseconds for the Normalize and the Round and Normalize instructions.

| 000                           | 100 2 | 200 30 | 300 40 | 400<br>j | 500 600 |

|-------------------------------|-------|--------|--------|----------|---------|

| SHIFT TIMING EXCEPT NORMALIZE |       |        |        |          | ·       |

| SCOREBOARD ISSUE              |       |        | ·      |          |         |

| "Go Shift"                    |       | 200    |        |          |         |

| "Request Release" (Normalize) |       |        |        |          |         |

| Clear Input Register          |       |        |        |          |         |

| Operands Received             |       |        |        |          |         |

| Clear SIR                     |       |        |        | ·        |         |

| Shift Direction Control       |       |        |        |          |         |

| IR <b>J</b> SIR               |       |        |        |          |         |

| Set SK Register               |       |        |        |          |         |

| Shift Count > Shift Network   |       |        |        |          |         |

| Clear SK                      |       |        |        |          |         |

| Transmit Result (s)           |       |        |        | *        |         |

|                               |       | ,      |        |          |         |

| NORMALIZE SPECIAL TIMING      |       |        |        |          | ·       |

| "Request Release" (Normalize) |       |        |        |          |         |

| Normalize Count >> SK         |       |        |        | 2002     |         |

| Shift Count >> Shift Network  |       |        |        |          |         |

| Transmit Results              |       |        |        |          | *       |

|                               |       |        |        | _        |         |

\* Earliest possible time - no result register conflict.

FIGURE 7.2 9

# SHIFT TIMING (EXCEPT NORMALIZE)

- t000 Issue of the Shift Instruction to the Scoreboard

- The jk portion of the current Shift instruction is received at the Shift Functional Unit. (jk is unconditionally sent to the shift unit every 100 nanoseconds, and is gated to SK upon receipt of a "Mask" or "Shift jk" mode bit) (See Figure 7.2-8)

- "Shift jk" or "Mask" mode bit was received, the jk catching register is transferred to the SK register. ##

- tl/5 The "Go Shift" pulse starts the Shift Unit timing chain

- Normalize mode is NOT specified. - The "Request Release" pulse is sent to the All Clear Network (SCBD) if the

- t300 Source operands are received at the Imput Registers of Chassis 8.

- The Shift Input Register (SIR) is cleared in preparation for the receipt of the operand.

- Shift Direction Control is enabled to the shift magnitude (SK) AND gates which will in turn enable the Shift Network. E330 £460)

- (2) Bj (if Nominal Mode) shift count is gated to the SK register. Sowrce operands are gated from the Input Registers to SIR. E340 - (I)

- Shift magnitude AND gates enable the Shift Network. Approximately 130 nanoseconds are allowed for filter time through the static shift metwork. E340) 在470

- "Transmit" pulse is received at the Shift Unit (assuming no third order conflicts exist) - The

- t450 The SK register is cleared as a result of the receipt of the "Transmit" pulse.

- "Transmit", and will be received at Entry Control at abour t500. t475 - The Shift Unit result is sent to the register chassis, gated by

## NORMALIZE SPECIAL TIMING

- "Request Release" pulse is sent to the All Clear Network if the Normalize mode is specified.

- t430 The coutput of the Normalize Network (normalize shift count) is gated to the SK register.

- t440 The Shift Magnitude AND gates enable the Shift Network. Approximately 130 nanoseconds are allowed for filter time through the static shift metwork. £570

- t500 The "Transmit" pulse is received at the Shift Unit.

- Shift Count Register is cleared due to the receipt of the "Transmit" pulse. - The

- t575 The Shift Umit result is sent to the register chassis, gated by "Transmit", and will be received at Entry Control at about t600

Reference is made to the Shift Functional Unit Customer Engineering

Diagrams, Sheet 111, where the logic associated with Shift timing can

be seen.

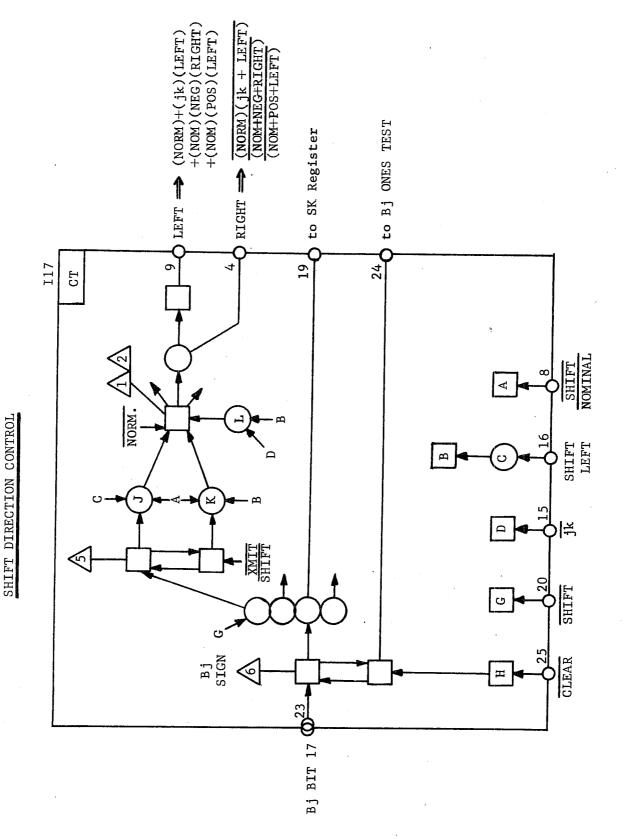

### 7.2.5 SHIFT DIRECTION CONTROL

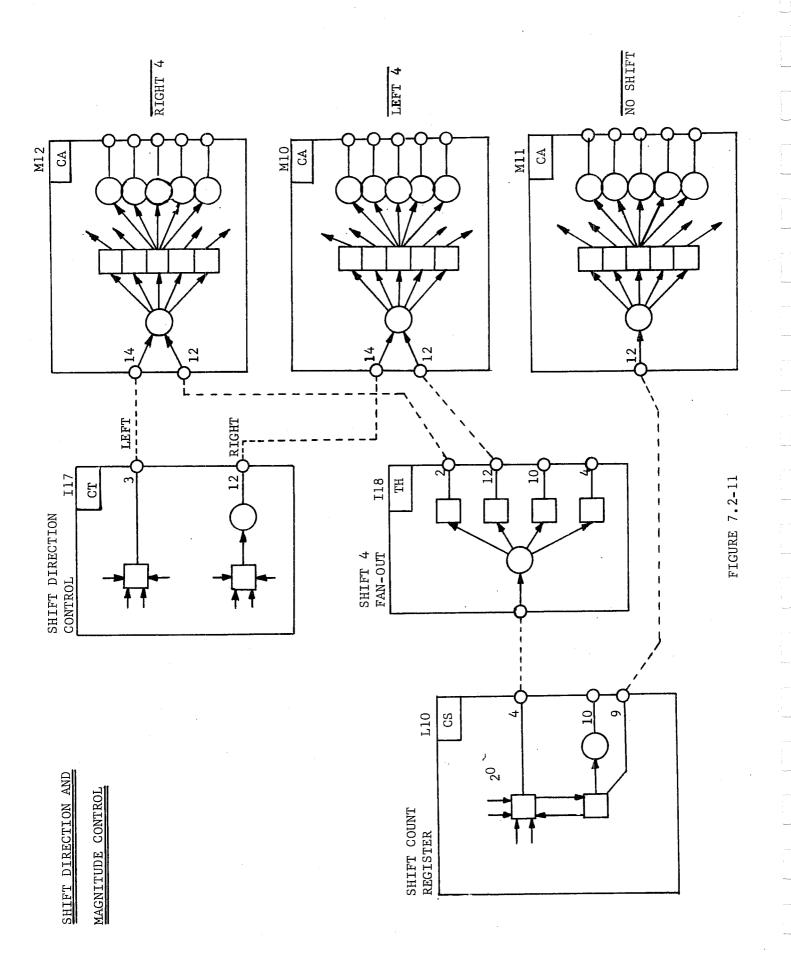

As is implied by the name, the function of Shift Direction Control is to determine the direction (left or right) of shift for the Shift class instructions. Mode bits and the negative or positive condition of Bj sign are logically combined on a CT module (I17) whose output will ultimately specify Left or Right direction. The direction is combined with bits from the Shift Count Register (SK) on CA modules which are then fanned out to enable the six ranks of the shift network. One of three possible enables will condition rank "X" of the Shift Network (where X = 1, 2, 4, 8, 16, or 32).

- 1. Shift Left "X" places (if Direction Control -> Left)

- 2. Shift Right "X" places (if Direction Control Right)

- 3. No Shift "X" places (if the SK bit for magnitude "X" = 0) During the following explanations, refer to Figure 7.2-10, a logic drawing of Direction Control.

Left shifts are possible only with the following instructions and conditions:

This instruction specifies an unconditional LEFT shift in the shift constant (jk) mode. Mode bits "Shift jk" and "Shift Left" are ANDed (II7, inverter L) and force a "one" out of test points one and two and pin 9.

- This instruction specifies a nominal LEFT shift if the sign at B register j is positive. (if Bj sign is negative, the shift direction will be right.) Mode bits "Nominal" and "Shift Left" and the condition "Bj is positive" are ANDed (117, inverter K) and force a "one" out of test points one and two and pin 9.

- 23 This instruction specifies a nominal right shift if the sign of B register j is positive. If Bj sign is negative, the shift direction will be LEFT. Mode bits "Nominal" and "NOT Left Shift" and the condition "Bj is Negative" are ANDed (I17, inverter J) and force a "one" out of test points one and two and pin 9.

- 24 and 25 Both of these instructions specify the Normalize mode of operation.

A LEFT shift is always required during Normalize; therefore, the

"Normalize" mode bit forces a "one" out of test points one and

two and pin 9 of module I17.

Right shifts are possible only with the following instructions and conditions.

A right shift will result in "zeros" at the outputs of test points one and two and a one out of pin 4 since all three AND gates (J, K, & L) and the Normalize condition will be "ones."

- 21 This instruction specifies an unconditional RIGHT shift in the shift constant (jk) mode.

- 22 This instruction specifies a nominal left shift if B register j sign is positive. If Bj sign is negative, the shift will be RIGHT.

- 23 This instruction specifies a nominal RIGHT shift if B register j sign is positive. (If Bj sign is negative, the shift will be left.)

- 43 This instruction forms a mask by RIGHT shifting a "one" from bit 59 the number of places specified by jk. Thus, RIGHT shift is always forced.

26 and 27 The Unpack and Pack instructions do not require shifting, but since all three AND gates (J, K and L) and the NORMALIZE condition will be "ones", a RIGHT shift signal is distributed to the shift network. But, these instructions do not gate the operands through the shift network and consequently, they are not shifted.

The outputs of Shift Direction Control are summarized with the following table:

| DIRECTION | PIN | BOOLEAN FORMULAS                                                                                                                                                                                                                    |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Left      | 9   | (NORM) + (jk) (LEFT) + (NOM) (NEG) (RIGHT) + (NOM) (POS) (LEFT)                                                                                                                                                                     |

| Right     | 4   | $(\overline{\text{NORM}})$ $(\overline{\text{jk}} + \overline{\text{LEFT}})$ $(\overline{\text{NOM}} + \overline{\text{NEG}} + \overline{\text{RIGHT}})$ $(\overline{\text{NOM}} + \overline{\text{POS}} + \overline{\text{LEFT}})$ |

Figure 7.2-11 shows how the shift direction and magnitude are combined to enable a given rank of the Shift Network. This example is for bit  $2^2$  or the Shift 4 places rank of the Network. The same method is used for the other ranks of the shift network.

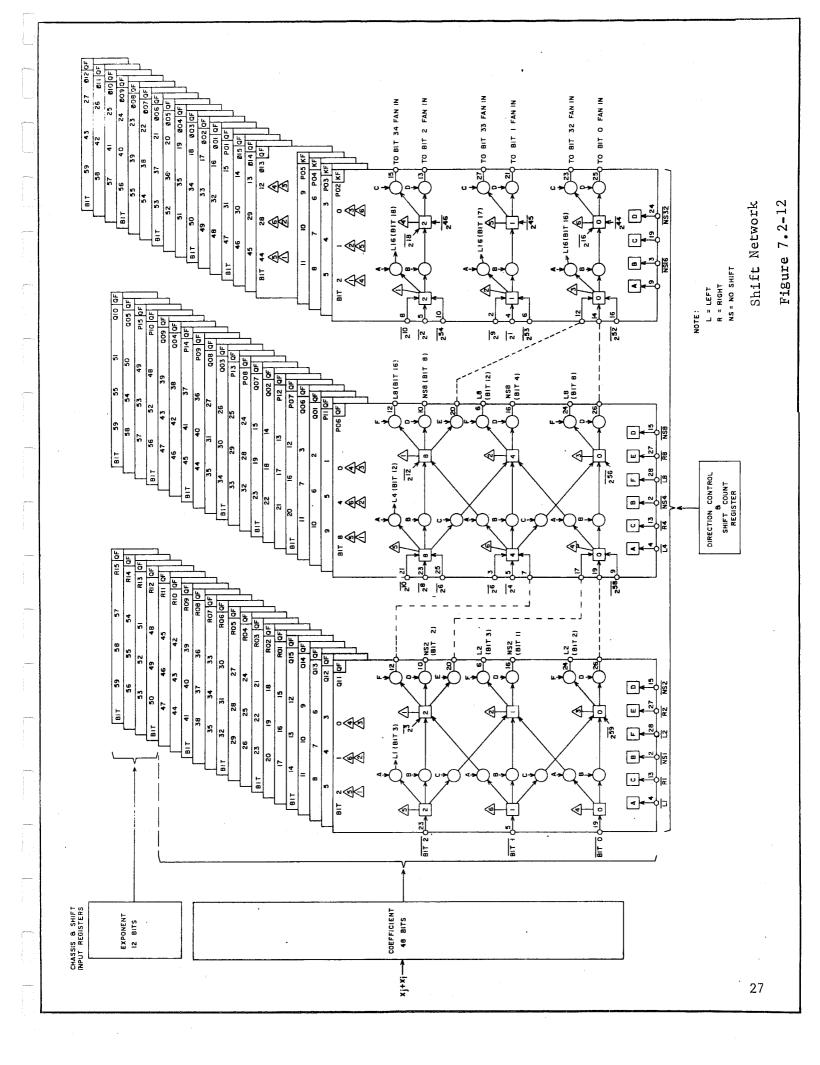

### 7.2.6 SHIFT NETWORK

The shift network shifts 60-bit quantities left or right on the basis of a 6-bit shift count in the shift count (SK) register. Left shifts are circular; right shifts are end-off with sign extension.

The quantity to be shifted is transferred from the chassis input register (IR) to the shift input register (SIR) whose slave outputs drive the 100 nsec static shift network. (See Figure 7.2-12) The network is organized in six shift paths or levels of 1, 2, 4, 8, 16, and 32 shifts progressing out from the input register. Each level corresponds to a

power of two and each "one" bit of the 6-bit shift count in SK gates a corresponding level of the network. A "zero" in any bit position of SK implies no shift (See Figure 7.2-11). Slave inverters on each bit of SK are gated by shift direction (left or right) according to instruction requirements. (Refer to Section 7.2.5, SHIFT DIRECTION CONTROL) The inverter outputs are fanned out to the proper level in the network and indicate a left, right or no shift for each of the six levels.

Each level of the shift network sends a bit to the next higher order shift level unshifted or shifted left or right the number of places assigned to the level. For left shifts, high order bits  $(2^{59})$  are wired to low order positions  $(2^{0})$  to provide a complete circular left shift. For right shifts, no connections are made on the right shift outputs of bit 0 or other bits in the network where a right shift would carry past bit 0.

For example, the right shift 16 output of the bit 9 circuit has no termination. This wiring produces the end-off feature of the right shift.

The sign (Bit 59) of the shifted quantity is extended on right shifts.

A "one" (negative quantity) or a "zero" (positive quantity) in this

position is extended to the right the number of positions the quantity

is shifted. During the formation of a Mask, a negative sign is forced.

The shift network treats zero extension automatically. Since any shift

will be at least one position, ones are extended beginning at the second

level and the first level is ignored. The sign extension slaves are thus

necessary only when the shift quantity is negative.

Figure 7.2-12 is a representative logic drawing of the Shift Network showing bits 0, 1 and 2. Notice the three enables (Left, Right, or No Shift) entering the first four stages of the Network. Note also, that on stages 16 and 32 only two enables enter each stage, Left and No Shift, since a right shift of 16 or 32 would produce an end off effect for these stages. The design of the network is like that of the Peripheral Processor Shift Network with the exception that this is a 60-bit, 6 stage network. The PPU shifter was an 18 bit, 5 stage network.

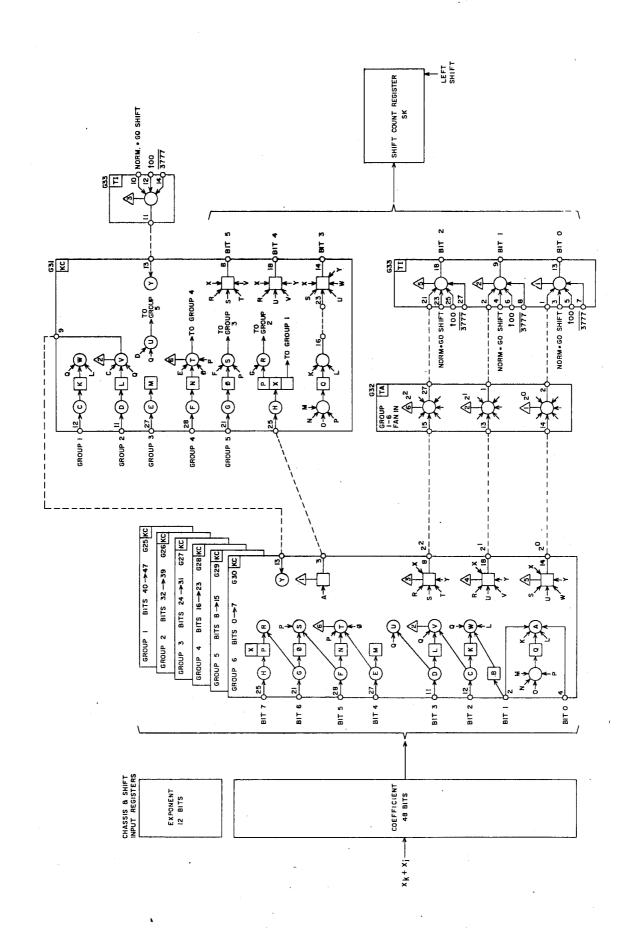

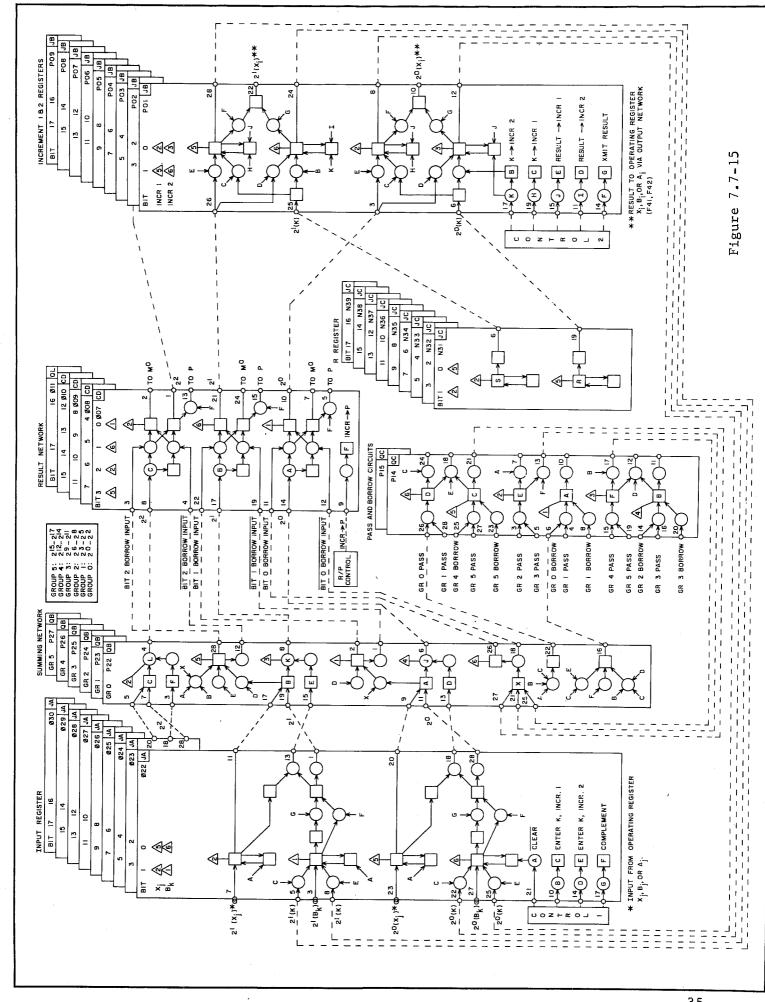

### 7.2.7 NORMALIZE NETWORK

The static normalize network forms a six-bit shift count, which defines the number of shifts necessary to normalize, and stores the count in the SK register. The shift network, under control of the SK register, is used to normalize the coefficient.

Initially, the coefficient is transferred from the chassis input register to the SIR (complemented if Xk is negative). Thus, the content of SIR is always positive during normalize operations. The normalize network organizes the low-order 48 bits of SIR into six 8-bit groups. It then:

- 1. Determines the highest order "one" in each group (a 1 of 8 selection).

- 2. Determines the highest order group with a "one" (a 1 of 6 selection).

- 3. Determines the number of zeros between the highest order "one" of the coefficient and bit  $2^{47}$ , and stores the quantity in the SK register.

Refer to Figure 7.2-13, during the following discussion.

Locating the highest order "one" in a group is a 1 of 8 selection which is accomplished by comparing a bit with all of the higher order bits in the group (modules G25-G30). In each of the six groups, this yields a three-bit "group count" which indicates the number of shifts necessary to move the bit to the most significant position in its group (test points 3, 4, and 5). The six group counts are combined in an OR circuit (TA module) which feeds the lower three bits of the SK register. The group count selected to enter SK corresponds to the group holding the highest order "one" in the coefficient.

Another circuit in each group tests the group for "All zeros" (modules

G25-G30, inverters A). The highest order group with a "one" is determined in the same manner as described above, i.e. each group is compared with all higher order groups through the all zeros circuits (module G31). Again, a three-bit quantity is formed in a count network but is sent to the upper half of the SK register. This quantity can be thought of as representing the number of sequential all zero groups beginning with the most significant (group 1).

Summary: Starting with the high-order bits of the coefficient, groups with all zeros are eliminated. When the first group containing a "one" is found, a count is sent to the three low-order bits of SK. This count is equal to the number of places required to shift the "one" to the highest-order bit of the group. The upper three bits of the SK register are loaded with the number of all zero groups to the left of the group containing the first one. Entry of all other groups into SK is blocked. Thus, a six-bit shift count ranging from 0 to 48 (60<sub>8</sub>) is formed in SK.

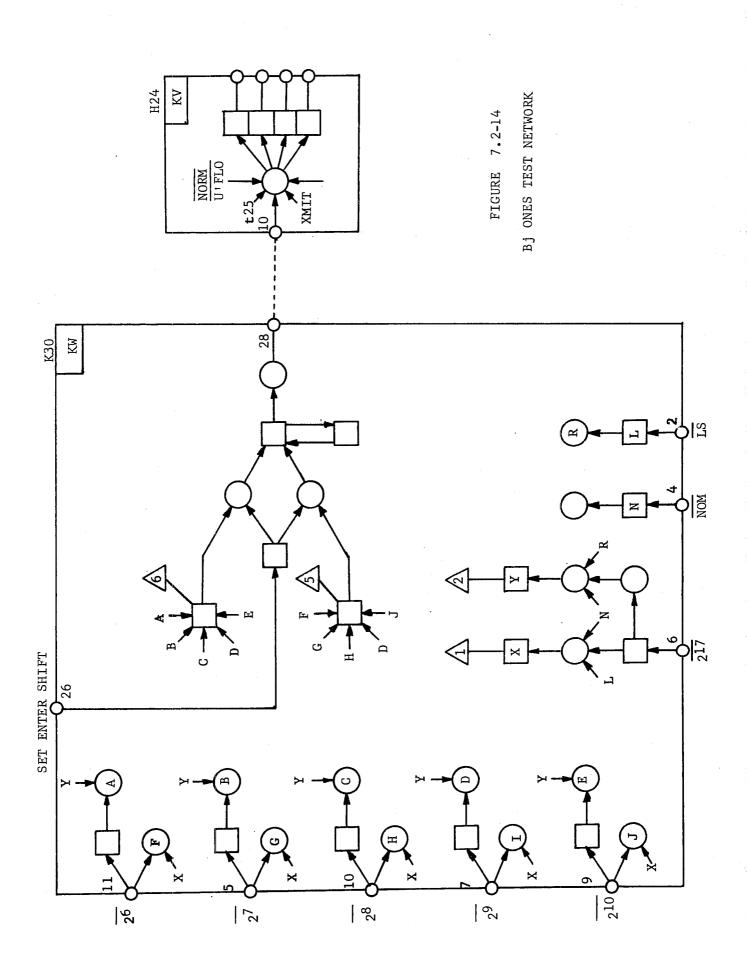

### 7.2.8 Bi ONES TEST NETWORK

The purpose of this test is to guarantee an all zero coefficient when the shift count contained in B register j exceeds 77(8) and a Nominal Right Shift is specified. For example, assume that Bj equals 000425(8) and a 23 (Shift Right Nominally) instruction is coded. The proper (all zero) coefficient should be obtained by shifting the coefficient 425(8) places to the right (since right shifts are by nature end-off). Since only six bits are contained in the Shift Count Register, the maximum shift possible is 77(8) places. In the case of a Nominal Shift, only the lower six bits of B register j are used, and thus if the Ones Test Network was not present, a Shift count of 25(8) would be used in this example. The result could obviously be erroneous since only 21(10) bits of the co-

efficient would be shifted to the right and end-off. The possibility of such an error occurring is eliminated by the Bj Ones Test Network.

This network is used to determine whether any one of Bj bits 6 through 10 is set during Nominal Right Shifts. The question arises: why are only bits 6 through 10 tested? The answer is found by considering that the Left Nominal (22) instruction is used during the conversion of Floating Point Numbers to Integers. The following example illustrates this process:

GIVEN:  $(X3) = 2006 \ 0 \longrightarrow 0527$

PROGRAM STEPS: 26423 (Unpack X3 to X4 and B2)

22624 (Left Shift X4 Nominally B2 places to X6)

RESULT: 1. The Unpack instruction will place 527 in X4 and 6 in B2.

- 2. The Shift Nominal instruction will shift X4 six places to the left and place the number 52700 in X6.

- 3. Thus, the floating point number  $527 \times 2^6$  is converted to the Integer 52700.

The point to be stressed from this example is that the Unpack instruction will not return to Bj, an exponent greater than 10 bits in magnitude.

Consequently, the Shift Nominal instruction, if used properly, should never find an exponent (Bj Register) greater in magnitude than 10 bits.

Figure 7.2.14 is a logic drawing of the Bj Ones Test Network. The test is a relatively simple matter of checking the state of bits 6 through 10 together with the sign (2<sup>17</sup>) of B register j. A "one" out of either test point 5 or 6 will disable the sending of the shifted coefficient to the output network since a "one" is required on pin 10 of H24. Thus, to enable the shifted result, the flip-flop on K30 must NOT be set. Test point 5 checks the Negative ("one") state of Bj against a

zero in each of bits 6 through 10 (terms "X" and "F", "G", "H", "I", and "J"). If Bj is negative, zeros are checked because the magnitude is in complement form. If any of these bits is a zero when Bj is negative, a zero is forced into test point 5 and when the "Set Enter Shift" is enabled, the flip-flop on K30 will be set. Test point 6 checks the Positive ("zero") state of Bj against a "one" in each of bits 6 through 10 (terms "Y" and "A", "B", "C", "D", and "E"). If any one of the bits is a "one" when Bj is Positive, a zero into test point 6 will allow the flip-flop to set when the "Set Enter Shift" gate arrives. Note that this circuit is used only during Nominal shifts when the Right direction is specified. The following Boolean formulas express the conditions required for terms "X" or "Y".

X = (NOMINAL) (LEFT) (2<sup>17</sup>) or, Nominal Left and Bj = Neg (Right Shift)

$Y=(NOMINAL\ (\overline{LEFT})\ (\overline{217})$  or, Nominal Right and Bj = Pos (Right Shift) Thus, during Nominal Right Shifts when there is a one present in any of bits 6 through 10 (true magnitude) the shifted result is not enabled to the coefficient bits of the transmitters. An all zero coefficient is then returned to Xi.

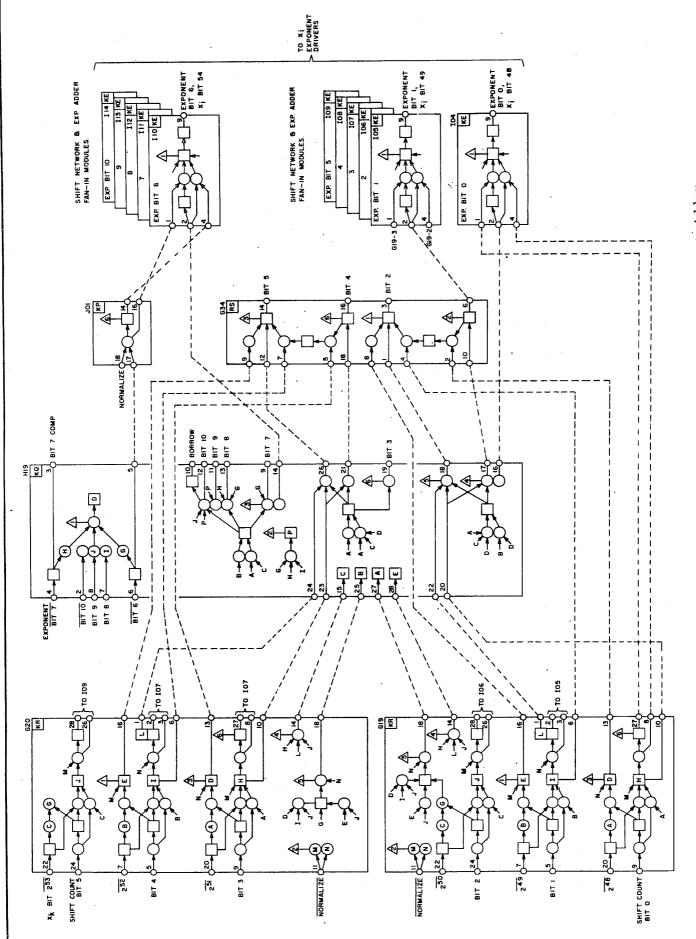

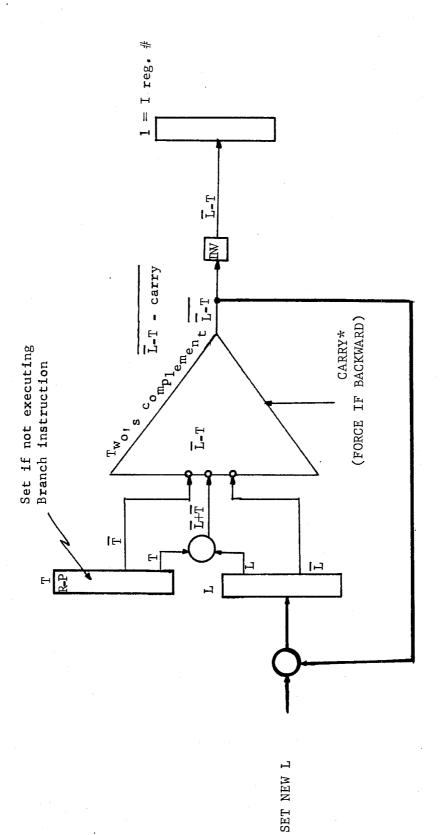

## 7.2.9 EXPONENT ADDER

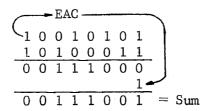

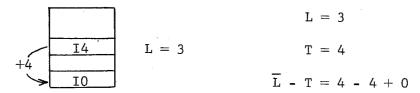

Since the coefficient of Xk is shifted left (increased) during the normalize process, the exponent of Xk must be decremented by an equivalent value. This is the function of the exponent adder - to subtract the shift count generated by the normalize network from the exponent of the source operand. The example in figure 7.2-15 illustrates the initial and final values of a normalize operation. In the example, a normalize

shift count of  $37_8$  is generated and sent to the SK register, which in turn conditions the shift network. The six bits of SK also feed the exponent adder along with the eleven bits  $(2^{48} - 2^{58})$  of the original exponent.

Before Normalizing:

$$(Xk) = 2135 0 - - - 0327715 (327715 X 2^{135})$$

After Normalizing:

$$(Xi) = 2076 6576320$$

$(657632 \times 2^{76})$

$$(Bj) = 0$$

----037 (Normalize Shift Count)

## Figure 7.2-15

Recall, that if the sign of the coefficient is negative during normalize operations, the complement of IR is sent to SIR. If the sign is positive, the true value of IR is sent to SIR. Thus, bits 48 - 58 of SIR will always contains the true form of the biased exponent and bit 59 will always be zero. The sign of the exponent can be determined with bit 58; the set condition indicated positive with the magnitude in true form (2000 - 3777) and the cleared condition indicates negative with the magnitude in complement form (0000 - 1777).

Also recall that underflow may occur during the normalize process, but only if the exponent is smaller (more negative) than negative 60<sub>8</sub> (since 60<sub>8</sub> is the largest shift count that can be generated by the normalize network).

For the purpose of explanation, the range of possible exponents is divided into four groups:

1) 0000 - 0057 (-1777 to -1720): A Negative exponent, and

under flow can occur if SK >  $_5$ EXP $_0$ . It is indicated by the presence of an End Around Borrow (EAB).

| UNDER                          | FLOW           | UNDERFLOW                |                        |  |

|--------------------------------|----------------|--------------------------|------------------------|--|

| EXP = 00 $SK = $ $RESULT = 11$ | <u>51 - 51</u> | $0053$ $\frac{15}{0036}$ | -1724<br>- 15<br>-1741 |  |

| EAB? Y                         | ES             | NO                       | )                      |  |

## 2) <u>0060 - 1777 (-1717 to -0000)</u>

Negative, but no underflow can occur (an End Around Borrow is not possible).

EXP. 0060 -1717 MAXIMUM (SK)

$$\frac{60}{0000}$$

$\frac{-60}{-1777}$

## 3) <u>2000 - 2057 (+0000 to +0057)</u>

Positive, and transition to negative might occur (if  $SK > 5EXP_0$ )

| Transition |                             |                   | No Transition      |                   |  |

|------------|-----------------------------|-------------------|--------------------|-------------------|--|

| EXP<br>SK  | 2050<br>52 (forced)<br>1775 | +50<br>-52<br>-02 | 2046<br>35<br>2011 | +46<br>-35<br>+11 |  |

# 4) <u>2060 - 3776 (+0060 to +1776)</u>

Positive, but transition to negative is not possible.

(SK) Maximum

$$\begin{array}{c} \text{EXP} & 2060 & +60 \\ \hline (SK) & \frac{60}{2000} & \frac{-60}{+00} \\ \end{array}$$

With this information in mind, a discussion of the adder logic follows. The terms "Generate", "Satisfy", and "Enable" are used during this explanation. They refer to the 1 and 0 combinations in each stage and are defined as follows:

Generate: requires (generates) a borrow from a higher stage.

Satisfy: will fill (satisfy) the borrow requirement of a lower stage and in doing so, will not generate a borrow.

Enable: in a sense, full-fills a borrow requirement, but in so doing, generates a borrow itself. It therefore passes-on (enables) a borrow to the next higher stage.

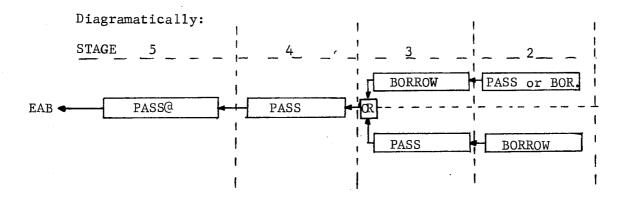

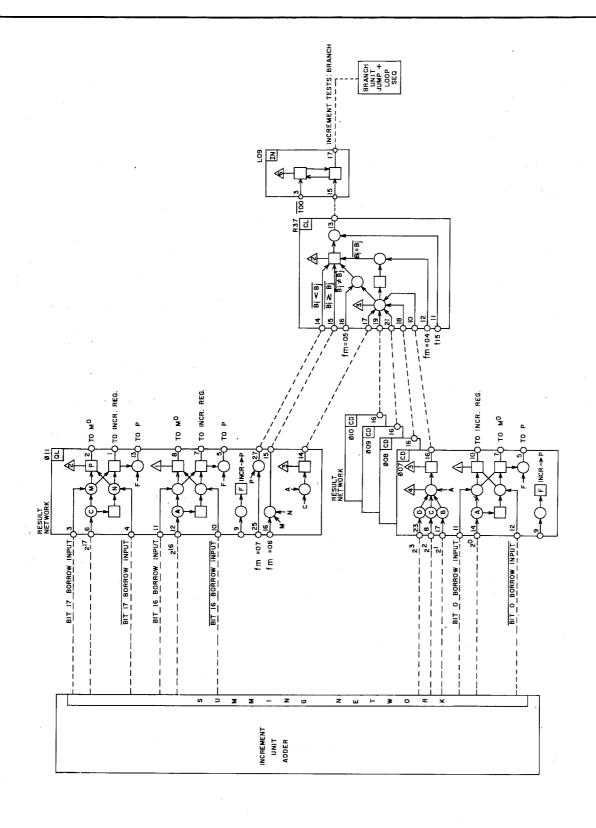

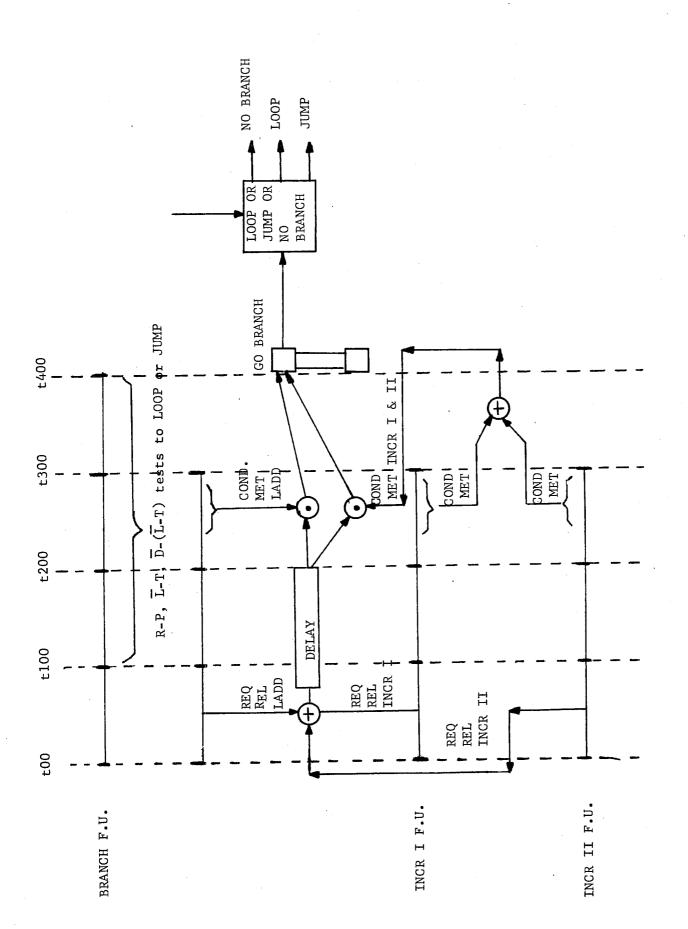

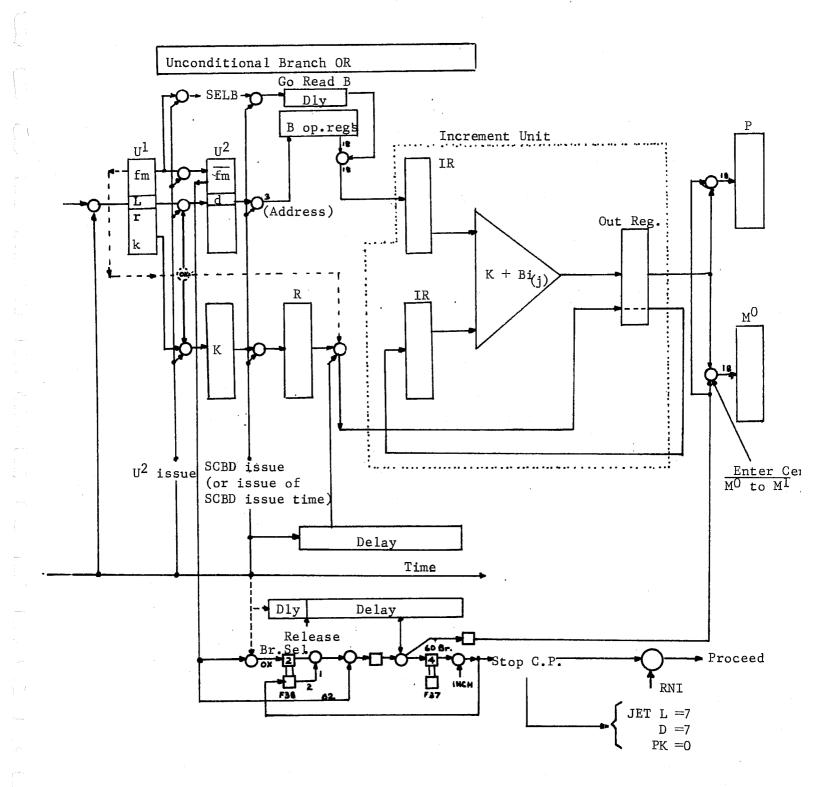

Figure 7.2-16 shows the subtraction of SK from the Xk exponent of our original example (FIGURE 7.2-15). Each stage is labeled as to its state; i.e. Generate, Satisfy, or Enable. Note that bits 6-10

FIGURE 7.2-16

of SK are not physically present and are therefore considered to be zeros. Consequently, a generate in stages six through ten is an impossibility. The zero/zero enable and satisfy are the only conditions possible in these stages. Thus, if a borrow is required by stage 5, it can be satisfied by a "one" in any of bits 6 - 9 of the Xk exponent. If no satisfy exists, all enables are assumed, each of bits 6-9 is toggled to a one, bit 10 is cleared, and an End Around Borrow is generated. Study the following example:

$$X_{k} = \begin{bmatrix} 2031 \\ 55 \\ 1754 \end{bmatrix} = \begin{bmatrix} 10 & 000 & 011 & 001 \\ 01 & 111 & 101 & 100 \\ \hline 1753 \end{bmatrix} = \begin{bmatrix} 431 \\ 01 & 111 & 101 & 100 \\ \hline 01 & 111 & 101 & 011 \end{bmatrix} = \begin{bmatrix} 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431 \\ 431$$

Exponent Adder Figure 7.2-17

Recall, that an EAB may also be generated if an exponent lies in the range, 0000 - 0057 (Group 1), but in this case, it indicates the Underflow condition. Thus, an EAB may occur in two cases, 1) with a positive exponent in the range 0-57 and 2) with a negative exponent in the range - 1777 - 1720. The adder logic differentiates between the two with the following conditions expressed in Boolean:

- 1. (EXP bit  $2^{10} = 1$ ) (EAB)  $\rightarrow$  Positive to Negative transition.

- 2. (EXP bit  $2^{10} \neq 0$ ) (EAB)  $\longrightarrow$  Underflow.

Figure 7.2-17 is a logic drawing of the exponent adder. To the left of the drawing, two KR modules (G19 and G20) determine the generate, satisfy, and enable condition for each of the low-order six stages. The outputs of inverters H, I, or J being a "one" indicate the enable (equivalence) condition for stages 0, 1, and 2 (G19) and 3, 4, and 5 (G20). Translations for the generate condition are also made on these modules (pins 13, 16, and 18 on both G19 and G20 indicate the generate condition).