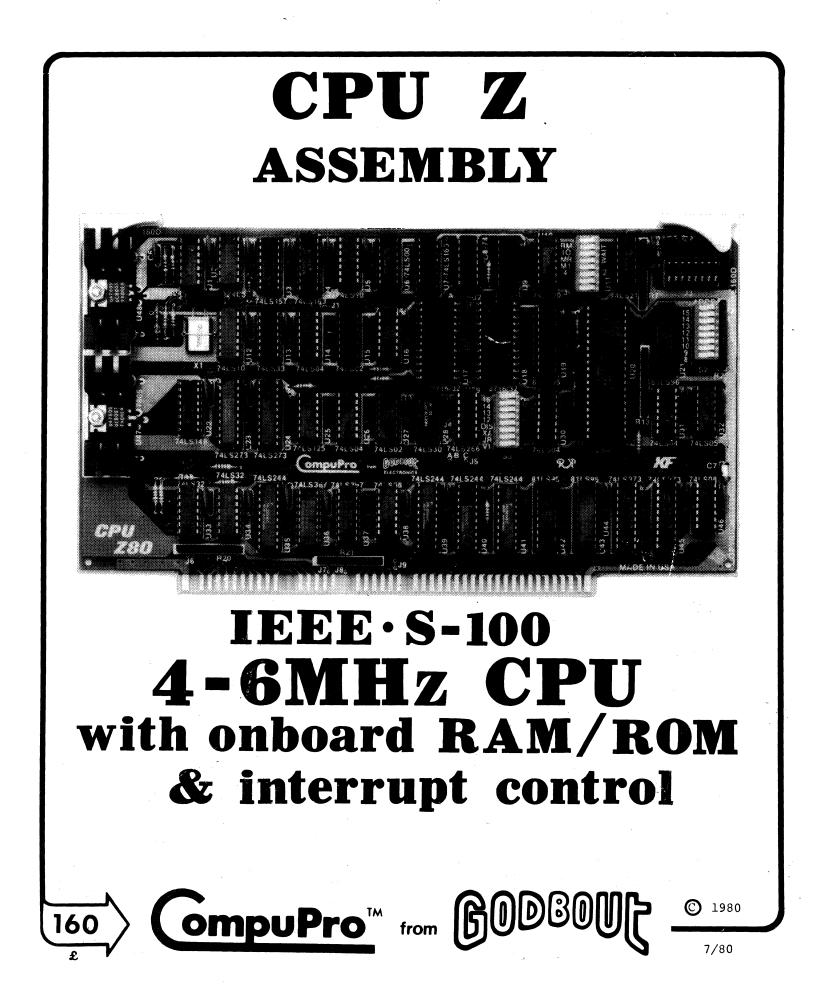

# CPU Z USER'S MANUAL

# IEEE·S-100 4-6MHz CPU with onboard RAM/ROM & interrupt control

CompuPro<sup>™</sup> from 600800

C 1980

#### PROCESSOR CARDS

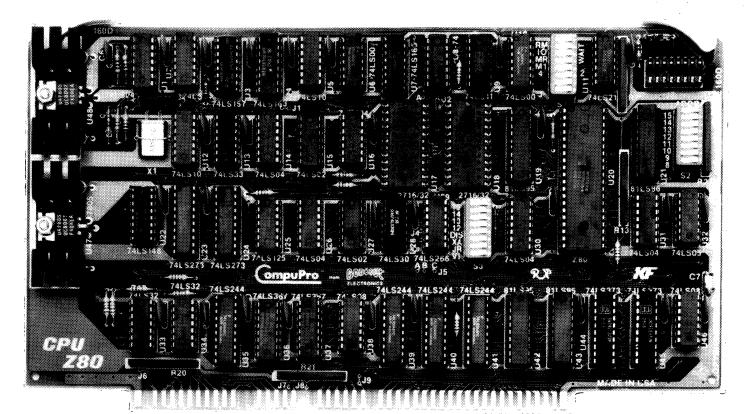

Congratulations on your decision to purchase the CPU Z80\*board, specifically designed for electrical and mechanical compatibility with the IEEE S-100 bus standard. The S-100 bus is the professional level choice for commercial, industrial, and scientific applications. This bus provides for ready expansion and modification as the state of the computing art improves. We believe this board, along with the rest of the S-100 portion of the CompuPro family, is one of the best boards available for that bus.

As amateur radio operators have contributed greatly to communication technology, so too the computer hobbyist has provided the microcomputer industry with many significant developments. In recognition of this fact, we also make this board available in "UNKIT" form for those who enjoy the challenge of assembling and testing a fine computer board.

As the first company to nationally offer memory kits to computer hobbyists, we again thank you for choosing a CompuPro CPU Z80 board...welcome to the club!

#### TECHNICAL OVERVIEW

The CPU Z80 was specifically designed to give the user one of the best Z80 CPU boards for the S-100 bus. The board features on-board PROM sockets, a power-on-jump circuit to any 255 byte boundary, a Memory Manager to extend the addressing range of the system from 64K-bytes to a maximum of 16M-bytes of system RAM, fully maskable vectored interrupts to speed up system throughput by eliminating polling loops, and wait state generation circuitry for all machine cycles.

Other features standard to all CompuPro boards include thorough bypassing of all supply lines to suppress transients, on board regulators, and low power Schottky TTL and MOS technology integrated circuits for reliable, cool operation. All this and sockets for all IC's go into a double sided, solder masked printed circuit board with a complete component legend.

#### USING THE VECTORED INTERRUPTS

The CPU chip recognizes 8 instructions as Restart0 - Restart7. These instructions will cause the program counter to jump to one of eight locations depending on the Restart instruction.

| RESTART | Program Counter(HEX) |

|---------|----------------------|

| 0       | 0                    |

| 1       | 8                    |

| 2       | 10                   |

| 3       | 13                   |

| 4       | 20                   |

| 5       | 28                   |

| 6       | 30                   |

| 7       | 38                   |

\* Z80 is a registered trademark of Zilog, Inc.

At these locations, jumps to interrupt driver routines can be placed into either RAM or PROM. Then when one of the VIO - VI7 lines goes low, the specific routine can instantly be started to service the interrupting device. Upon Power-on-Clear or reset (RESET\*) the interrupt mask is cleared, enabling all eight interrupt lines (NOTE: This does NOT mean that the Z30 has interrupts enabled.). Then (with the VI switch (SW3-8) turned ON) when any of the VI inputs goes low the Restart will be generated if the CPU has previously received an Enable Interrupts (FB(H)) command. To disable an individual interrupt line, or a group of lines, the mask must be set up by an output to Port FE(H) with the desired mask in the Accumulator. A "1" in the mask will disable the interrupt line, and a "0" will enable the interrupt line.

If it is desired to use this CPU Z80 board with the Z80 mode 2 interrupts, the on-board vector generation circuitry must be disabled. To do this switch SW3-8 should be turned OFF, and all 1's should be output to the interrupt mask port (Port FE(H)). This will prevent the CPU Z80 from responding to the V.I. lines, but it will still respond to the bus interrupt signal (bus pin 73).

|    | EXAMPL  | Ε       | (HEX) | (BINARY)   |

|----|---------|---------|-------|------------|

| to | disable | VI5-VI7 | EO    | (11100000) |

| to | disable | VI2     | 04    | (00000100) |

| to | disable | all     | FF -  | (11111111) |

Note that the VI lines are all open collector and more than one device can be connected to each VI line by using open collector gates.

It is recommended to put a "DEAD MEMORY" error recovery routine at location 38 (H), since this location will be jumped to in case the CPU encounters an FF (H) instruction, which corresponds to a restart 7. This is the instruction that will be read from a memory location for which there is no system memory. Location 38 is the most common launching pad for CPU flights into never-never land.

#### USING THE NONMASKABLE INTERRUPT

The S-100 BUS nas a NMI\* pin (bus pin 12) which is implemented on the CPU card for any function that the user desires. NMI\* is primarily used for a catastrophic system failure, such as loss of primary power. This interrupt enables the processor to execute a short program to save current system parameters on either a disc or some other nonvolatile memory before total power is lost (which usually takes milliseconds, lots of time for a computer). The NMI\* causes the CPU to jump to address 56(H), which should be initialized with a routine to control the interrupt.

#### EXTENDED ADDRESSING

Address lines Al6-A23 are driven through output port FD(H) and can be changed with a simple output instruction. Upon Power-on-Clear or reset (RESET\*) the extended address lines will be reset to 0, bringing the system up in base page. To access memory in other than base page requires an output to Port FD(H) with the desired page address in the Accumulator in order to set the extended address lines Al6-A23. These address lines are pin numbers 16, 17,15, 59, 61, 62, 63, & 64, for address lines Al6-A23 respectively.

Example shown below:

| ACCUMU | JLATOR DATA | TO ACCESS PAGE |

|--------|-------------|----------------|

| (HEX)  | (BINARY)    | (HEX)          |

| 40     | 0100000     | 40             |

| 2      | 0000010     | 2              |

| FO     | 11110000    | FO             |

Of course, to take advantage of this extended addressing feature requires memory boards which respond to extended address lines. If a board does not monitor the S-100 extended address lines, then only the normal 16 address lines will be decoded.

#### WAIT STATES

A single wait state may be added to any processor cycle by closing the corresponding dip switch on SWL. A wait may be added to:

| CYCLE       | SWITCH | POSITION |

|-------------|--------|----------|

| PROM        |        | 1        |

| 1/0         |        | 2        |

| MEMORY      |        | 3        |

| INSTRUCTION |        | 4        |

Due to critical timing requirements of the Z80 during an instruction fetch (M1), extra time may be required for marginally slow memory chips. When running at 4 MHZ some RAM chips may also need more time for each memory operation than is normally allowed. The on board PROM sockets may be used for many different speed PROM's, and when running at 4 MHZ a wait state may be needed for a fetch there also. The I/O wait should rarely be needed because of the fact that few I/O boards run slow and the Z80 automatically generates one I/O wait state, but the provision is made to the user.

#### ON-BOARD-MEMORY SOCKETS

The MEMORY sockets on this board are set up to take INTEL 2716, T.I. 2516 2Kx8 EPROMS, or any of the new 2Kx8 RAM chips which are

pin compatible (Hitachi HM5116 or equivalent). By cutting J2(A-B) on the solder side above U17, J4 on the solder side to the left of U29, an J5(A-C) on the component side below U29 and installing jumpers J2(A-C) and J5(A-B) the sockets can now be used for 2732 4Kx8 EPROMS. (NOTE: Extreme care must be used when soldering in the jumpers so as not to damage the board or any of the traces. A soldering iron of no more than 25 watts should be With 2732's SW3-4 is no longer used to address the used.) sockets. The on-board sockets will be totally disabled when switch SW3-5 is ON. With SW3-6 ON, the sockets are addressable anywhere in base page (A16-A23 are all 0) on a 4K boundry (8K for the 2732's). This feature allows the user to have MEMORY in base page only. With SW3-6 OFF, the sockets ignores address lines A16 - A23 and occupies every page of memory. A prime example of how to use the sockets in this "shadow" mode would be to use them with SW3-6 turned ON and the Power-on-jump set to the start of the PROM address, then when the system is initially turned on the program in the PROM will start and either initialize the system by booting in a disk program, or some other type of routine. Then the last thing the PROM will do is jump to the RAM address where the initialization routine was loaded. The first thing that program will do is an output to port FD(H) of anything except 0. This will set the extended page address to the page that was in the Accumulator, and the sockets will be disabled. RAM which was overlapped with the PROM can now be used and a complete memory map is available to the user. SW3 positions 1-4 are used for address lines A15-A12. The socket closest to the Z80 chip is the low address half PROM and the right socket the high half.Example:

|   | SWITC | H S3 |   | DESIRED START ADDRESS (HEX) |

|---|-------|------|---|-----------------------------|

| 1 | 2     | 3    | 4 | 2716 2732                   |

| 0 | 0     | 0    | 0 | 0000-0FFF 0000-1FFF         |

| 0 | 0     | 0    | 1 | 1000-1FFF                   |

| 0 | 0     | 1    | 0 | 2000-2FFF 2000-3FFF         |

| 0 | 0     | 1    | 1 | 3000-3FFF                   |

| : | :     | :    | : | : : : :                     |

| : | :     | :    | : | : : : :                     |

| 1 | 0     | 1    | 0 | A000-AFFF A000-BFFF         |

| : | :     | :    | : | : :                         |

| 1 | 1     | 1    | 1 | F000-FFFF                   |

ON = "0" OFF = "1"

To disable ROM completely, turn ON SW3-5

#### CLOCK

The clock for this system can be set to allow the CPU to run at either 2MHZ or 4MHZ. SWI-5 is used to select between these two speeds. When SWI-5 is ON the CPU will run at 2MHZ and bus pin 24 (O) will have a 2MHZ square wave on it. When SWI-5 is OFF, the system will run at 4MHZ and bus pin 24 will have a 4MHZ square wave on it. Bus pin 49 (CLK) will always have a 2MHZ signal on it.

#### POWER-ON-JUMP/JUMP-ON-RESET

Provisions have been made on this board to allow the processor to jump to any memory location on a 256 byte boundary on either a power-on only, or every reset also. To enable this feature, JMP ENABLE (SW1-8) should be turned ON and the jump address should be set on switch S2 according to the table below. To enable the jump on every reset also, SW3-7 should also be turned ON.

| SWITCH   | FUNCT  | ION   |     |   |     |

|----------|--------|-------|-----|---|-----|

| POSITION |        |       |     |   |     |

| 1A       | ADDRES | S A15 |     |   |     |

| 2        | 11     | A14   |     |   |     |

| 3        | . 11   | A13   |     |   |     |

| 4        | **     | A12   | ON  | = | "1" |

| 5        | 79     | A11   | OFF | = | "0" |

| 6        | 18     | A10   |     |   |     |

| 7        | 88     | A 9   |     |   |     |

| 8        | ADDRES | S A 3 |     |   |     |

EXAMPLE: To jump to E900 for a North Star floppy disc system, S2 positions 1-3,5, and 8 should be ON and S2 positions 4,6,and 7 should be OFF. JMP ENABLE (SW1-8) should be ON to enable this feature.

NOTE: Since the jump circuitry disables the input buffer, it is unnecessary to use the phantom line (S-100 pin 67) for proper operation.

#### MWRITE GENERATION

The CPU Z80 has circuitry on board for generating the MWRITE signal (bus pin 68) and a positive going strobe will be generated for each memory write operation. This circuitry looks at the bus and whenever the sOUT signal is low, and the pWR\* signal strobes low, a MWRITE strobe will be generated. This signal must be generated at only one source in each system. If there is a front panel in your system it also may be generating the MWRITE signal, and the signal from the CPU Z80 must be disabled. There are two ways to disable this signal: A) Cut jumper J7 on the solder side below U36 and R21; or B) Remove pin 9 of U36 from its socket and let the pin hang out, this makes it easier to reconnect the pin should you ever want MWRITE to be generated from the CPU Z80 board in the future. If MWRITE is generated in more than one place, memory boards that rely on MWRITE as their write strobe may not work properly.

#### IMSAI FRONT PANEL USAGE

Although we will soon be manufacturing a front panel that will be fully compatible with the IEEE standard, if you have an IMSAI type front panel this CPU will require minor modifications to work properly. The problems arise from the fact that the IMSAI front panel (which does not conform to the IEEE standard) requires some signals that are not on the S-100 bus. Jumper pads are provided to allow these lines to be used. J5, and J8 should be installed to connect bus pins 53, and 71 respectively to control the CPU from the front panel. When the system is set to run at 4MHZ, the front panel will force the CPU to run at 2MHZ when the RUN/STOP signal is in the STOP mode. This will allow for proper front panel operation which is speed dependent. Socket J3 in the upper right corner is for the front panel connector. The CPU MWRITE circuitry will also have to be disabled if the front panel is going to generate MWRITE (bus pin 68). Jumper J9 can be installed to have the CPU drive bus pin 27 (which was the WAIT line), but this is not necessary for proper system operation.

### CIRCUIT DESCRIPTION

#### Vectored Interrupts and Mask

Upon reset (RESET\*) U23 is cleared, and will output all lows to the Or-gates (U33 & U34). The VIO - VI7 inputs normally sit at a high level, and hence all inputs on U22 are high. This resting state makes the GS output high. Upon receiving a vectored interrupt when one of the VIO - VI7 inputs goes low, U22 will output a value corresponding to the highest priority interrupt on the lines. This value will go to U44 and when the CPU acknowledges the interrupt, the proper Restart command will go to the CPU. When a 1 has been written into the mask port FE(H), U23 will output a high to the associated Or-gate (U33 & U34). Then when an interrupt pulls the input low, U22 will still have a high input and will never detect interrupts that are being masked out.

#### EXTENDED ADDRESSING

When an OUT FD(H) instruction is executed, the data bits in the Accumulator are latched into U24 and output on bus lines Al6-A23. These address lines will be tri-stated along with the other 16 address lines when ADDR-DSABL (Bus pin 22) is driven low by an external device requesting control of the bus.

#### CPU STATUS LINES

The S-100 bus has eight status signals that all bus masters must provide, these signals come from U45. During either a read cycle or a write cycle these status signals are latched on the bus. A short time after the read or write signal goes away the status signals are allowed to toggle. The S-100 status signals are shown below, along with their associated bus pins. (A \* suffix means active low signal.)

| SIGNAL | BUS PIN |

|--------|---------|

| sWO*   | 97      |

| SMEMR  | 47      |

| SINTA  | 95      |

| sM1    | 44      |

| SINP   | 46      |

| SOUT   | 45      |

| SHLTA  | 48      |

| sXTRQ* | 58      |

These status bits are decoded from the seven control signals coming from the Z80 as shown below: (A \* suffix means active low signal)

#### STATUS SIGNALS

| CONTROL | SIGNAL |       | 10*    | SMEMR | SINTA | sMl | sINP | sout st | ILTA |

|---------|--------|-------|--------|-------|-------|-----|------|---------|------|

|         | 1      | (a) c | or (b) |       |       |     |      |         |      |

| RFSH*   | 1      | 1     | Х      | Х     | X     | Х   | Х    | Х       | Х    |

| MRQ*    | 1      | 0     | Х      | 0     | Х     | X   | X    | х       | X    |

| RD*     | 1      | 1     | х      | 0     | Х     | Х   | 0    | Х       | Х    |

| WR*     | 1      | Х     | 0      | Х     | Х     | Х   | Х    | 0       | Х    |

| IORQ*   | 1      | Х     | Х      | Х     | 0     | X   | 0    | 0       | Х    |

| M1 *    | 1      | Х     | х      | Х     | 0     | 0   | X    | Х       | Х    |

| HALT*   | 1      | х     | Х      | X     | Х     | х   | Х    | Х       | 0    |

An X means a don't care condition. The sXTRQ\* signal is permanently high since this is an 8 bit processor.

#### SYSTEM CLOCK

The system clock circuitry consists mainly of Ul, U3, and U4. The 15 MHZ square wave is fed into U4 which divides it down to the desired system clock speed. The multiplexer U3 will feed either 16 MHZ or 8 MHZ to the pSYNC and pSTVAL\* generation circuitry and 2MHZ or 4MHZ to the Z80 and bus for the system clock. If jumper J8 is used, then when the RUN LINE (bus pin 71) is low the input to U5 will be low and cause the system to run at 2 MHZ. This is the same circuitry that switch SW1-5 uses to determine the system speed. U4 also has a 2MHZ output that is fed through a buffer to bus pin 49.

7

# POWER-ON-JUMP(POJ)/JUMP-ON-RESET(JOR)

The jump circuitry consists of octal inverter U21 (81LS95), DIP switch SW2, SIP resistor R23, hex o.c. inverter U32 (74LS05), a "D" flip flop U2, the POJ enable switch SW1-8, and JOR enable switch SW3-7. With the POJ enable switch ON, upon receiving a power-on-clear, the "D" flip flop is cleared which disables input buffer U43, and enables jump buffer U21. This action starts a three byte sequence which will cause the CPU to jump to the proper starting location. The CPU is reset to address 0, and from the jump buffer a jump (C3H) instruction is put on the data At address 1 the low order address of zero is then put on bus. the data bus, then at address 2 the high order address coming from the jump switch setting is placed on the data bus. When address 2 is in the address buffer the "D" flip flop will then be clocked to the set state and disable the jump buffer while enabling the data input buffer. The "D" flip flop will not get cleared again until the next POC. This complete sequence also occurs for every RESET\*, if switch SW3-7 is turned ON. This option will allow the CPU to come up with a known jump on poweron and then later when a reset is recognized the CPU can either start again at O(H) or jump to the address in switch SW2.

#### WAIT STATES

The CPU wait line (Z80 pin 24) is driven by three main sources, causing the processor to give more time for certain devices or system states. The three sources are; a) The RDY (pin 72) bus signal, which will be driven by an external device which must have more time to respond to the CPU, b) The XRDY (pin 3) bus signal which is driven by the front panel (if the system has one), and c) On board selector to generate a wait state for four different states. The on-board wait state will come from the settings of SWl positions 1-4. Ml (SWl-4) will generate a wait state for every instruction cycle. The MRQ (SW1-3) will generate a wait state for every memory fetch cycle. The IORQ (SW1-2) will generate a wait state during every I/O operation. Finally, the ROM switch (SW1-1) will generate a wait state for every access of the on-board MEMORY. US will remain in the clear mode with Q\* high unless one of these switches (SW1 positions 1-4) is turned ON. Then when one of the selected inputs go low, U8 will be set and cause the wait input (on the CPU) to go low. These wait states can only start when pSYNC is high. When pSYNC goes low U8 will be clocked low with the next negative edge of the system clock.

# PARTS LIST for the CPU Z80

(1) CPU Z80 circuit board

INTEGRATED CIRCUITS (note: the following parts may have letters, suffixes and prefixes along with the key numbers given below.)

| (2) | 74LS00    | quad 2 input NAND                  | (U6, U10)       |

|-----|-----------|------------------------------------|-----------------|

| (2) |           | quad 2 input NOR                   |                 |

| (6) | 74LS04    | hex inverter                       | (Ul, Ul4, Ul6,  |

|     |           |                                    | U26, U30, U31)  |

| (1) | 74LS05    | hex inverter o.c.                  | (U32)           |

| (2) | 74LS08    | quad 2 input AND                   | (U38, U46)      |

| (2) | 74LS10    | triple 3 input NAND                | (U5, U12)       |

| (1) | 74LS11    | triple 3 input AND                 | (U9)            |

| (1) | 74LS21    | dual 4 input AND                   | (Ull)           |

|     | 74LS30    | 8 input NAND                       | (U28)           |

| (2) | 74LS32    | quad 2 input OR                    | (U33, U34)      |

| (1) | 74LS33    | quad 2 input NOR o.c.              | (U13)           |

| (2) | 74LS74    | dual "D" flip flop<br>quad buffers | (U2, U8)        |

| (1) | 74LS125   | quad buffers                       | (U25)           |

| (1) | 74LS148   | octal encoder                      | (U22)           |

| (1) | 74LS158   | quad 2-to-l mux.<br>4 bit counter  | (U3)            |

| (1) | 74LS163   | 4 bit counter                      | (U4)            |

| (1) | 74LS165   | 8 bit shift register               | (U7)            |

| (4) | 74LS244   | octal bus driver                   | (U35, U39-41)   |

| (1) | 74LS266   | quad 2 input XNOR                  | (U29)           |

| (2) | 74LS273   | octal latches                      | (U23, U24)      |

| (2) | 74 LS 367 | hex bus driver                     | (U36, U37)      |

|     | 74LS373   |                                    |                 |

| (3) | 81LS95    | octal bus driver                   | (U19, U42, U43) |

| (1) | 81LS96/98 | octal bus inverter                 | (U21)           |

| (1) | 280A      | Z80 microprocessor                 | (U20)           |

| (2) | 7805      | 5 volt regulator                   | (U47, U48)      |

|     |           |                                    |                 |

# OTHER ELECTRONIC COMPONENTS

| (5)  | SIP resistor packs          | (R7, R13, R20,<br>R21, R23)* |

|------|-----------------------------|------------------------------|

| (5)  | 39uf Tantalum Capacitors    | (C1-C5)                      |

| (29) | Ceramic bypass Capacitors * |                              |

| (1)  | 430 pico farad capacitor    | (C7)                         |

| (12) | 5.1K ohm resistor c.f.      | (R5, R3-10, R12, R14-        |

|      |                             | 19, R22)                     |

|      | lK ohm resistor c.f.        | (R1, R2, R4)                 |

| (1)  | 120 ohm resistor c.f.       | (R3)                         |

| (1)  | 4.7K ohm resistor c.f.      | (R5)                         |

| (1)  | 300 ohm resistor c.f.       | (R22)                        |

| (1)  | 330 ohm resistor c.f.       | (R11)                        |

|      | 16MHZ crystal               | (X1)                         |

| (2)  | glass signal diode          | (D1, D2)                     |

## MECHANICAL COMPONENTS

| (46) | Low | Profile | Sockets | * |

|------|-----|---------|---------|---|

|------|-----|---------|---------|---|

Dip Switch, 8 position (S1-S3)\* TO-220 Heat Sinks (3)

(2)

- (2) Sets 6-32 Hardware

(2) card extractors

- \* supplied already soldered on the board

# SWITCH SUMMARY

| S1<br>POSITION                       | FUNCTION                                                                                                                                                                                                                                                           |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | WAIT STATE FOR ROM<br>WAIT STATE FOR I/O<br>WAIT STATE FOR MEMORY<br>WAIT STATE FOR INSTRUCTION FETCH<br>SPEED SWITCH (OFF = 4 MHZ.)<br>NOT USED<br>NOT USED<br>POWER-ON-JUMP ENABLE                                                                               |

| S2<br>POSITION                       | FUNCTION                                                                                                                                                                                                                                                           |

| 2<br>3<br>4<br>5<br>6<br>7           | JUMP ADDRESS BIT A15<br>JUMP ADDRESS BIT A14<br>JUMP ADDRESS BIT A13 ON = "1"<br>JUMP ADDRESS BIT A12 OFF = "0"<br>JUMP ADDRESS BIT A11<br>JUMP ADDRESS BIT A10<br>JUMP ADDRESS BIT A9<br>JUMP ADDRESS BIT A8                                                      |

| POSITION                             | FUNCTION                                                                                                                                                                                                                                                           |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | SOCKET ADDRESS BIT A15 \<br>SOCKET ADDRESS BIT A14 \ ON = "0"<br>SOCKET ADDRESS BIT A13 / OFF = "1"<br>SOCKET ADDRESS BIT A12 /<br>SOCKET DISABLE (when ON)<br>SOCKET BASE PAGE ONLY (WHEN ON)<br>JUMP-ON-RESET ENABLE<br>INTERRUPT ENABLE FOR VECTORED INTERRUPTS |

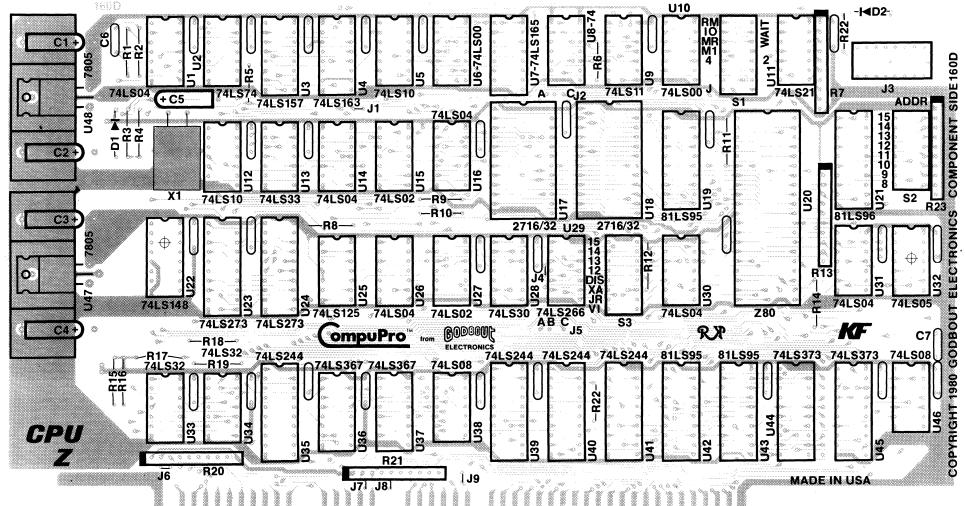

**COMPONENT SIDE**

#### ASSEMBLY PROCEDURES

Proper operation of your kit depends upon good soldering techniques, along with correct identification and handling of the various parts used during construction. Read this manual *thoroughly* before plugging in your soldering iron.

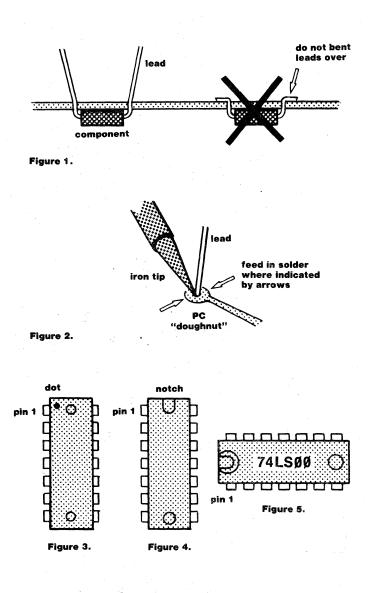

**SOLDERING TECHNIQUES.** CompuPro boards are solder-masked with a solder-resistant coating over the entire board, except where solder connections are made. This minimizes the chances of getting an unwanted solder bridge between adjacent traces.

Those who have not previously worked with a soldermasked board will find that it takes considerably less solder to make a good joint since the solder does not spread out across the solder pad. On this board, all soldering should be done on the *solder* side of the board (the back side or side opposite the component side). Use a low wattage iron (10-25 watts) with a small or "PENCIL" tip. Use a good quality *rosin-core* solder ("60/40 or 63/37 alloy").

Because of the close spacing of pads, we recommend keeping the component leads straight up while soldering (see Figure 1).

Bring the tip of the iron in at an angle, touching both the pad and the component lead, and feed a small amount of solder in at either side where the tip touches the pad and lead (see Figure 2).

Use only enough solder to fill the joint and make a very small "fillet" around the lead. Keep the soldering iron on the joint only long enough to make sure that the solder has "wetted" the lead and flowed smoothly into the joint; too little time may result in a poor joint and too much time may damage the component or the bond between the pad and the board.

Be especially careful when soldering DIP switches, since some internal parts are thermoplastic and are very heat sensitive. Clip any excess leads off fairly close to the board to keep them from bending over and touching anything. Use eye protection while soldering or clipping leads.

NOTE: The use of any type of solder other than a good quality rosin-core solder invalidates the warranty. Do not use any type of solder paste or corrosive flux under any conditions.

Any modification of this board not approved in advance by Godbout Electronics may void your warranty.

**IDENTIFICATION OF PARTS.** There are many ICs used in this kit; each one must be oriented correctly for proper operation. Most ICs have a dot near one corner that indicates pin 1 (see Figure 3). Sometimes this dot appears in conjunction with a deeply cut notch or circle. Other types indicate the pin 1 end of the IC by a deep notch or a notch within a shallow circle (see Figure 4). In case of doubt, place the IC in front of you so that any identifying numbers read from left to right; pin 1 is almost always in the lower left-hand corner (Figure 5).

NOTE: If there is a recognizable mark for pin 1, always go by that rather than the printing.

HANDLING OF PARTS. All integrated circuits may be damaged by static electricity; however, MOS ICs - such as memory ICs - are more vulnerable than most. You can easily accumulate a static charge on your body in the thousands-of-Volts range by merely walking across a rug or sliding into a chair on a dry day. If you then touch the pins of an IC, this charge can flow through the IC and damage its internal structure. Most static discharges destroy the IC immediately, but it is possible for a low energy static discharge to puncture the gate oxide in such a manner that the IC functions properly for a while but fails some time later as metal migrates into the puncture and finally causes an internal short-circuit. To prevent this, leave the ICs in their protective foil until needed. Then, before plugging in each IC, touch an exposed trace on the board (pin 1 or 2 on the edge connector, for instance) to equalize any residual charge. This will force any charge to flow through your body instead of through the pins of the IC. Also, avoid wearing clothing which has a tendency to generate static charges (such as sweaters, almost all synthetic fabrics, and so on). (Industrial IC users recommend wearing a grounded wrist strap and working on a conductive surface which is grounded to the same point. Almost the same protection can be achieved by working on a sheet of aluminum foil which is electrically connected to the wrist with a flexible wire attached to a metal watch band or loop of bare wire around the wrist. If the aluminum foil can be conveniently grounded it will offer even more protection.)

COMPUPRO PRODUCT FROM GODBOUT ELECTRONICS · BLDG. 725, OAKLAND AIRPORT, CA 94614

#### **CONSTRUCTION - GENERAL PROCEDURES**

#### Refer to back page for specific assembly details.

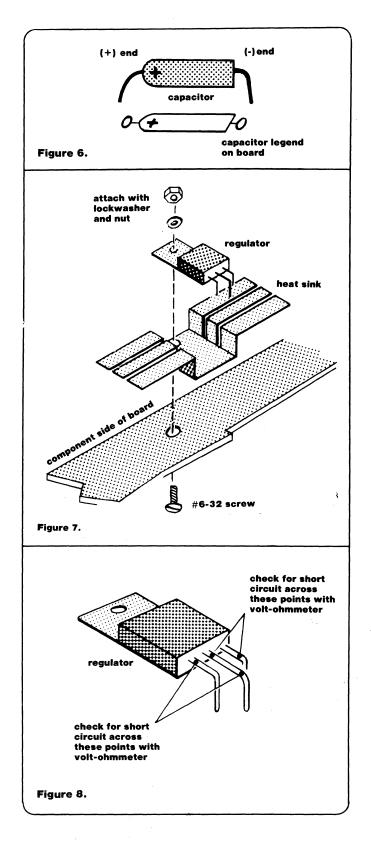

1. Bend leads, mount, and solder the tantalum capacitors in place, as indicated, carefully observing orientation of the (+) end, refer to figure **6**.

2. Mount each regulator and the regulator heat sink in place, referring to figure 7. Observe that the heat sinks mount on top of the board and then the regulators mount on top of the heat sinks. If desired, a small dab of heat sink compound may be added between the regulator cases and the heat sinks to improve thermal transfer from regulator to sink.

Again, referring to figure 7, bend all regulator leads as shown, then bolt the heat sink and regulator assemblies into place using the nuts, bolts, and lock washers provided.

After these assemblies are in place, solder the regulator leads on the solder side of the board.

3. Before proceeding, check your work thus far by testing the board for shorts between supply lines and ground. Refer to figure 7. Use an ohm meter to test for a shorted condition at the test points indicated on the regulator. Perform this test on all regulators. If you find a short circuit at any of these points, carefully check over your board for the cause of the short. If all readings are satisfactory, proceed with assembly.

NOTE: All DIP switches should be in the OFF position when these readings are taken.

4. A common problem with boards returned for repair is improper installation of an IC. Sometimes a pin will bend under an IC instead of going into the proper socket contact. We recommend inserting each IC halfway and verifying visually that all pins are started into the socket; then push the IC in the rest of the way.

Keeping this in mind, insert all ICs.

5. Check the board over carefully for errors in construction. If all appears correct, assembly of your board is complete.

HAPPY COMPUTING!

As amateur radio operators have contributed greatly to communication technology, so has the computer hobbyist provided the microcomputer industry with many significant developments. In recognition of this fact, we also make this professional quality board available in kit form for those who enjoy the challenge of assembling and testing a fine computer board. Also it saves you a pile of hard earned bucks.

#### CONSTRUCTION

1. Bend leads, mount, and solder the tantalum capacitors (Cl-C4) in place, as indicated, carefully observing the orientation of the (+) end, refer to figure 6 inside.

2. Mount and solder the regulator assemblies as described in section 2 of the previous page, referring to figure 7 observe that the heat sink mounts on the board and that the regulator mounts on top of the heat sink.

3. Carefully mount and solder crystal X1 in place and secure it with a piece of double stick tape or foam if desired.

4. Carefully solder in SIP resistor R13 to the board next to the Z80 socket. The writing on the SIP should be facing the Z80 socket. (This step may have already been done)

5. At this point, it is time to power up the board (without chips) and verify that you have the proper voltages. With power applied to the board, you should measure:

+5 volts at pin 3 of U47 (7805) +5 volts at pin 3 of U48 (7805)

If all readings are satisfactory, proceed with step 4. inside.

ERATTA: The parts list in the User's Manual lists U3 as a 74LS158 when it should be 74LS157. You should change your User's Manual to show this correction.

GODBOUT ELECTRONICS BOX 2355, OAKLAND AIRPORT, CA 94614