ompuPro

# Technical Training Manual

FOR USE BY AUTHORIZED SYSTEMS CENTERS, DEALERS AND OEMS ONLY.

ALL INSTALLATION AND SERVICE MUST BE PERFORMED BY QUALIFIED PERSONNEL.

#### INTRODUCTION

This Training Manual is designed to aid technicians in the repair of COMPUPRO products. It is intended for use by technicians having completed the COMPUPRO TECHNICAL TRAINING. It was designed as an instructional aid and for use as an easy reference in the lab.

There are three sections to this manual. The material covers system packages, individual boards, and BIOS and operating system basics.

## CONTENTS

SYSTEMS SECTION

CompuPro Systems Packages

Description of each system Standard switch and jumper settings Troubleshooting chart Floppy Disk Drive Alignment procedures

BOARD PRODUCTS SECTION

Technical summary of each board Diagnostic documentation Troubleshooting chart Diagnostic tests list

SOFTWARE SECTION

CP/M 2.2 CP/M 86 CP/M 8-16 MP/M 8-16 CP/M 68K

APPENDIX

Recommended equipment for System Center Labs Logic Diagram - Jade Bus Probe

Also included in the manual is a floppy diskette containing diagnostic software useful in the repair of COMPUPRO products, as well as a list of recommended equipment for the SYSTEM CENTER labs. Technical manuals on the operating systems are contained in the software section. TECHNICAL TRAINING MANUAL Copyright ~1984 CompuPro Hayward, CA 94545

Document #17200

First Printing: April 1983 Second Printing: July 1983 Third printing: July 1984

Contents of this document were proofread with the aid of SpellGuard~ a product from SORCIM Inc. Santa Clara, CA.

DISCLAIMER - CompuPro makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, CompuPro reserves the right to revise this publication and to make any changes from time to time in the content hereof without obligation of CompuPro to notify any person of such revision or changes.

Registered trademarks: CompuPro; CompuPro: CP/M; Digital Research. Trademarks: SYSTEM 8-16A, SYSTEM 8-16B, SYSTEM 8-16C, SYSTEM 8-16D, SYSTEM E/68K, RAM 16, RAM 17, RAM 21, RAM 22, SYSTEM SUPPORT 1, INTERFACER 3, INTERFACER 4, DISK 1, DISK 2, and SELECTOR CHANNEL, DISK 3, ENCLOSURE 2, M-DRIVE/H; W.J. Godbout: CP/M 80; CP/M-86; MP/M-86 and Digital Research; Digital Research.

All rights reserved. No part of this publication may be reproducted or transmitted in any form, or by any means, without the written permission of CompuPro. Printed and assembled in the United States of America. SYSTEMS SECTION

#### COMPUPRO SYSTEMS PACKAGES

This section of the manual covers the COMPUPRO SYSTEMS. Contained is all material necessary to set up any system from start to finish. The make up of each system is discussed. Material is included on standard switch settings and jumpers for each system. Also included is a troubleshooting chart, covering common problems and possible remedies for the systems as a whole.

- Description of the COMPUPRO SYSTEMS as a general product. A detailed description of each individual system is given, including the contents, features, possible applications, and advantages of each system.

- 2. Standard switch and jumper settings for the systems. Each board is covered individually. Required modifications for upgrading boards to run MP/M are included.

- 3. A troubleshcoting chart for the systems. This chart covers board level troubleshooting.

This section was designed for the purpose of getting systems up and running as quickly and easily as possible. Problems with individual boards are discussed in the next section of the manual.

# 2. STANDARD SWITCH SETTINGS AND CABLE CONNECTIONS

SYSTEM 8-16 A SYSTEM 8-16 B SYSTEM 8-16 C SYSTEM 8-16 D SYSTEM 8-16 E (68K)

-

3. TROUBLESHOOTING CHART

COMMON SYSTEM PROBLEMS

-

|                                       | COMMON SYSTEM PROBLEMS                                    |                                                                  |

|---------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|

| SYMPTOM                               | : PROBABLE CAUSE                                          | : REMEDY                                                         |

| Won´t boot at all                     | :<br>: No or incorrect voltage<br>:                       | :<br>: Check voltage on<br>: motherboard                         |

|                                       | :<br>: No clock signal<br>: on bus pin 24                 | :<br>Check for clock signal<br>:                                 |

|                                       | :<br>: Bad or incorrectly<br>: hooked up cables           | :<br>Check cables and<br>replace as needed                       |

|                                       | :<br>Bad DISK 1/1A                                        | :<br>: Swap DISK 1/1A                                            |

| Lights on both<br>drives lit          | :<br>: Cables to drives<br>: connected backwards<br>:     | :<br>: Turn over 50 pin cable<br>: on one end and reconnect<br>: |

| Runs CP/M 80 will<br>not boot CP/M 86 | :<br>: Bad or missing 'Go 86'<br>: EPROM or 6116 RAM chip | :<br>: Check or replace EPROM<br>: or RAM chip                   |

|                                       | : Bad diskette                                            | : Try another diskette                                           |

|                                       | : Bad DISK 1/1A                                           | : Swap DISK 1/1A                                                 |

|                                       | : RAM addressed<br>: incorrectly                          | : Check switch settings<br>:                                     |

|                                       | :<br>Bad RAM board at<br>extended address                 | :<br>: Swap RAM boards<br>:                                      |

|                                       | :<br>Bad SYSTEM SUPPORT                                   | :<br>Swap SYSTEM SUPPORT                                         |

|                                       | :<br>: 8085/88 CPU not<br>: swapping processors<br>:      | :<br>: Check CPU board<br>:<br>:                                 |

| Head loads once<br>then locks up      | :<br>: Bad memory Board<br>:                              | :<br>: Check memory in<br>: page one                             |

|                                       | : Bad DISK 1/1A<br>:                                      | : Swap DISK 1/1A<br>:                                            |

| Head loads over<br>and over           | :<br>: Bad DISK 1/1A<br>:                                 | :<br>: Swap DISK 1/1A<br>:                                       |

|                                       | : Bad cables<br>:                                         | : Check cables and<br>: replace as needed                        |

| SYMPTOM                           | : PROBABLE CAUSE                                       | : REMEDY                                     |  |  |

|-----------------------------------|--------------------------------------------------------|----------------------------------------------|--|--|

| Won´t format disk                 | :<br>: Bad DISK 1/1A<br>:<br>: Bad drive               | Swap DISK 1/1A<br>Swap drives                |  |  |

|                                   | : Bad cable<br>:                                       | : Change cable<br>:                          |  |  |

| Nothing on the screen but sounds  | :<br>: Bad serial I/O<br>:                             | :<br>: Check console board<br>:              |  |  |

| as if it's booting                | : Bad or incorrectly<br>: hooked up cable              | : Check cables<br>:                          |  |  |

|                                   | : Terminal set wrong<br>:                              | : Check terminal setup<br>:                  |  |  |

|                                   | : DISK 1/1A set for wrong<br>: serial board<br>:       | : Check DISK 1/1A<br>: paddles<br>:          |  |  |

| Garbage on screen                 | :<br>: Bad serial I/O<br>:<br>:                        | :<br>: Check console board<br>:<br>:         |  |  |

| : Terminal not set<br>: correctly |                                                        | : Check switch settings<br>: on the terminal |  |  |

|                                   | : Bad terminal<br>:                                    | : Swap with a good one<br>:                  |  |  |

| Won't boot MP/M                   | :<br>: Interrupt jumpers on<br>: I/O board not correct | :<br>: Check jumpers<br>:                    |  |  |

|                                   | : Bad CPU<br>:                                         | : Check X2 on CPU 8085/88                    |  |  |

|                                   | :                                                      | : Swap CPU<br>:                              |  |  |

| Some users won't                  | :<br>: Bad I/O board                                   | :<br>: Swap I/O board                        |  |  |

| work under MP/M                   | :<br>: Interrupt jumpers wrong<br>: on I/O board<br>:  | : Check jumpers<br>:<br>:                    |  |  |

.

,

.

| SYMPTOM                                                                            | : PROBABLE CAUSE                                                                                      | : REMEDY                                                                                                              |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| System lock up when<br>one user logs out                                           | :<br>: Bad I/O 3 board<br>:<br>:                                                                      | :<br>: Swap I/O 3 board<br>:<br>:                                                                                     |

| Panic! Trap<br>Uninitialized<br>Interrupt message                                  | :<br>: All terminals not<br>: turned on<br>:<br>:<br>: Interrupt jumpers<br>: wrong on I/O board<br>: | :<br>: Turn on all terminals<br>: or disconnect terminals<br>: not in use<br>:<br>: Check interrupt jumpers<br>:<br>: |

| System 816 D<br>Won't boot MP/M<br>and gives message<br>Uninitialized<br>interrupt | :<br>Modification not done<br>on SYSTEM SUPPORT board<br>:<br>:<br>:                                  | :<br>: Pull out pin 4 on U28<br>:<br>: Check for dip shunt<br>: in J8<br>:                                            |

| When all else fails                                                                | :<br>Bad motherboard<br>:<br>:                                                                        | :<br>: Turn enclosure upside<br>: down and pound on it<br>:<br>: Change enclosure<br>:                                |

#### COMPUPRO

#### FLOPPY DISK ALIGNMENT PROCEEDURE FOR QUME 842 DRIVES

### 7/26/84

#### INTRODUCTION

This document describes the equipment and proceedures required to align a QUME 842 floppy disk drive. This document is intended for the use of CompuPro System Centers, Dealers and OEMs. This is not intended for use by the end user.

#### REQUIREMENTS

To perform this procedure correctly, you will need the following items.

- 1) A working 816 letter series machine running CP/M 80.

- 2) A second DISK 1 or 1A addressed at AO hex.

- 3) A DYMEK alignment diskette.

- 4) The CompuPro alignment routine called "ALIGN.COM" and its associated files.

- 5) An Oscilloscope with trigger input and two probes.

- 6) A QumeTrak 842 Maintenance manual is suggested.

- 7) A drive to align with cable and power supply.

#### PROCEDURE

1) Set the switches on the DISK 1 or 1A board so that it is addressed at AO hex and the BOOT EPROM is inhibited. Install this in the 816 system and connect the floppy drive to be aligned to it with a 50 pin cable.

- 2) Connect the Oscilloscope to the drive as follows:

- A. Connect the channel input to test point "1A".

- B. Connect the external trigger input to test point "3"

- C. Connect the ground clips of both probes to ground.

3) Set the Oscilloscope as follows:

- A. Set your channel input to 200 mV./div., AC coupled, with a sweep rate of 20 mS./div.

- B. Set your trigger controls to external, DC coupled, normal triggering.

4) Power up the system and BOOT CP/M 80. Execute the program "ALIGN.COM". Insert the alignment diskette into the drive to be aligned.

5) After the routine signs on, type a <CR> and it should answer back "OK". Now type "SHOW" (All commands must be in capitol letters only!!!) and strike <CR>. The program will respond with the menu of commands. When executing a command, always follow it with a <CR>.

| SHOW      | - LIST COMMAND OPTIONS                            |

|-----------|---------------------------------------------------|

| INIT      | - INITIALIZE DISK1 ALIGNING DRIVES                |

| S 0 0     | - HOME TO TRACK O                                 |

| S 3 8     | - MOVE TO TRACK 38                                |

| S40       | - MOVE TO TRACK 40                                |

| S76       | - MOVE TO TRACK 76                                |

| TR        | <ul> <li>PERFORM CONTINUOUS TRACK READ</li> </ul> |

| S 0 2     | - SEEK BETWEEN TRACKS 0 & 2 CONTINUOUSLY          |

|           | (HIT ANY KEY TO TERMINATE)                        |

| DRA,B,C,D | - SELECT DRIVE FOR ALIGNMENT                      |

| BYE       | - EXIT TEST ROUTINE BACK TO CP/M                  |

Two additional commands not listed are:

| НО | - | SELECT | HEAD | 0 | (THIS | ΙS | THE | DEFAULT) |

|----|---|--------|------|---|-------|----|-----|----------|

| H1 | - | SELECT | HEAD | 1 |       |    |     |          |

6) Type "INIT" to initialize the controller. Then type "SOO" to recalibrate the drive to track 0. Next type "S40" to seek to track 40. Type "TR" to load the heads on the drive.

#### RADIAL ALIGNMENT

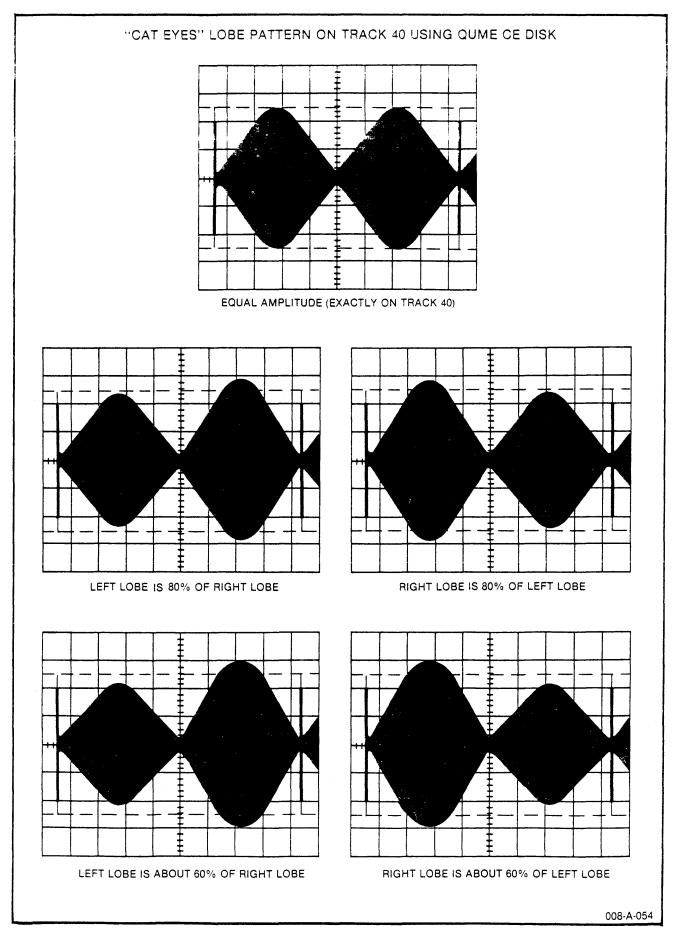

7) At this point you should see the "cats eye" lobe pattern on the oscilloscope. See figure 43., page 49 of the QUME manual. The lobes should be of the same amplitude as shown. Now select head 1 by striking any key to unload the heads, type "H1" to select head 1, and type "TR" to load the heads again. You can go back to head 0 by typing the same procedure above by substituting "H0" for "H1".

If the lobes are not within 80% of each other, loosen the two screws on the PCB side of the main frame which secure the stepper motor. Rotate the stepper motor very slowly and carefully until the lobes are of equal amplitude.

Select the opposite head and verify that the lobes are approximately identical and equal on both heads.

Carefully tighten the stepper motor screws and re-verify the alignment.

## READ/WRITE HEAD AZIMUTH CHECK

8) Type "S76" to seek to track 76. Type "H0" to select head 0, and type "TR" to load the heads.

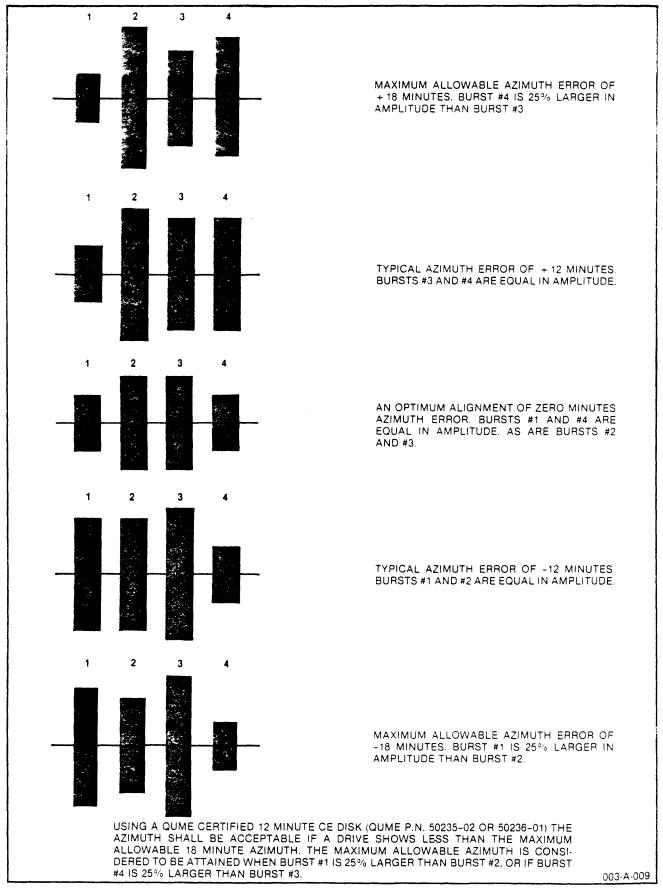

Set the vertical deflection to 100 mV. and the time base to 0.5 mS./div. You should now see the azumith check pattern shown on figure 21. and page 27 of the QUME manual.

Compare the wave form displayed to the Azumith Check illistration in figure 21. If the displayed wave form is not within + and - 18 minutes, the head/carriage assembly needs to be replaced.

Select head 1 and check the Azumith for that head. It also should be within + or - 18 minutes.

There is no adjustment for Azumith.

INDEX SENSOR ALIGNMENT

9) With the exact setup above, you should be able to see the index marker approximately 1/2 division in from the left edge of the screen. The Azumith pattern should be starting at 1 division from the left. Select head 0, set the time base to 50 uS. per division, and see the index marker approximately 4 divisions or 200 uS. in from the left. If it is not ~200 uS. from the left, you must adjust it.

Adjust the index sensor by loosening the phillips head screw by the base of the door solenoid. There is a large washer under this screw. Carefully slide this assembly until the index marker is at 200 uS. + or - 50 uS. Carefully tighten the screw and verify that it is still in alignment.

This completes the alignment procedures for the QumeTrak 842 drive.

Figure 43. R/W Head Radial Alignment

#### MAINTENANCE

Figure 21. Azimuth Check

#### BOARD PRODUCTS SECTION

#### INDIVIDUAL BOARDS

This section of the manual focuses on the individual boards that make up the system packages. First, a technical summary of the boards is given and the basic operation of the board is explained. Next, documentation for the diagnostic software used in house is described and explained. These tests include both those used in production and those used in the labs for repairs on the boards.

The final part of the material on each board is a troubleshooting chart. This chart covers problems likely to be encountered in the field. Probable causes and possible remedies for these problems are also discussed.

The purpose of this section is to give technicians the knowledge and tools necessary to repair hardware problems with COMPUPRO boards.

CONTENTS MEMORY BOARDS **RAM 16 RAM 17** RAM 21 **RAM 22** CPU BOARDS CPU 8085/88 CPU 8086/87 CPU 68K CPU 286 SYSTEM SUPPORT 1 **INTERFACER** 3 INTERFACER 4 DISK 1 AND 1A DISK 2 and SELECTOR CHANNEL DISK 3 **COMPUTER ENCLOSURE 2** M-DRIVE/H BOARDS DIAGNOSTIC TEST GLOSSARY

#### COMPUPRO MEMORY BOARDS

COMPUPRO has several memory boards, four of which are used in the system packages. All four of these boards are static RAM with at least 64K of memory on the board. Three of these boards are capable of both 8 and 16 bit operations. RAM 16, 21 and 22 will respond to SXTRQ\* with SIXTN\*, indicating that a 16 bit transfer can be done.

#### **RAM** 16

The RAM 16 features 64K bytes or 32K words of static RAM, using 2K byte by 8 bit, 6116 CMOS chips. This RAM is addressable on any 64K byte boundary in the 16 megabyte address space as specified by the IEEE 696 standard.

The RAM 16 dynamically switches between byte-wide and word-wide modes per the state of the sXTRQ\* signal on the S-100 bus. A PAL element selects the proper memory chip or chips. The memory array is designed in such a way that when doing 8 bit operations, bytes that are odd (i.e. ending with a 1) are stored in one chip while the even bytes are stored in another. This makes it possible to do 16 bit operations using the two chips at one time. This board was designed to work with 8086/88 type processors at speeds to 10 MHz.

#### RAM 17

The RAM 17 features 64K bytes of static RAM, using the 6116 CMOS chip. The RAM is addressable at any 64K byte boundary in a 16 megabyte space. Four 16 kilobyte segments may be individually disabled through an on-board DIP switch. The highest 8K block is further divided into four 2K blocks which can be individually disabled. The RAM 17 is the easiest to troubleshoot since each 2 kilobyte chunk of memory directly corresponds to one RAM chip.

The windowing capabilities of the board allow its use with memorymapped devices, or with operating systems that require a portion of memory to be global.

#### RAM 21

The RAM 21 features 128K bytes or 64K words of static RAM, using 16K by 1 MOS chips. The RAM 21 is addressable on any 128K boundary in a 16 megabyte address space. The board is dynamically switched between 8 and 16 bit modes by the SXTRQ\* signal. A PAL is used to control the switching and to select the proper memory chips.

#### RAM 22

The RAM 22 features 256K bytes or 128K words of static RAM, using 8K by 8 CMOS chips. The RAM 22 is addressable on any 256K boundary in a 16 megabyte address space. The board is dynamically switched between 8 and 16 bit modes by the SXTRQ\* signal. Two PALs are used to control the switching and to select the proper memory chips.

#### PRODUCTION TESTS - RAM BOARDS

There is one test for all of the RAM boards. This tests has several parts, and tests both the memory and the support circuitry.

- MEMTEST: The first part of this test is the BIT STUCK HIGH OR LOW test. This test sends out OOHex and FFHex to all memory locations and then reads it back. If anything other than OO or FF comes back, an error message is given, stating the nature of the problem and the address of the error.

- The ADJACENT BIT SHORTED test and the ODD EVEN BIT test are next. These tests fill the memory with 55 and AAhex to see if any data lines are shorted together. Again the error message gives the location and the nature of the problem.

- Then the BIT SHIFT LEFT and the BIT SHIFT RIGHT tests send a single bit of data through one data line. The bit is then shifted to the next data line and sent through the board on that line.

- The ADDRESS LINE test is similar to the BIT SHIFT tests. Each address line is tested individually by sending a bit through on each address line then shifting it to the next.

- Finally, the RANDOM NUMBER test is used to detect pattern sensitivity of the board. A set of random numbers is stored in the memory and duplicated until the board is full. The data is checked when it is read back out. This test is repeated several times. As with the other portions of the test the error messages states the location and nature of the problem.

These tests work essentially as follows:

- 1. The board is filled with a certain byte ( 00,FF,AA,55)

- 2. One byte gets a different pattern (FF,00,55,AA)

- 3. The rest of the board is checked to make sure the original byte remains

- The next byte is given the complementary pattern and the process repeats

One troubleshooting technique that is useful for all the boards but for the RAM boards in particular, is the visual inspection. Although boards shipped from COMPUPRO should have no problems like bent pins or missing or damaged parts, strange things have been known to happen in the field. Customers will often attempt to change a chip or add a feature to the board that was not designed into it. Take a very close look at all the boards before running the tests.

| SYMPTOM                                 | : PROBABLE CAUSE                                                              | : REMEDY                                                                                                                     |

|-----------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Board does not exist                    | :<br>Board not selected<br>:<br>:<br>:<br>: Bad voltages on board<br>:<br>:   | :<br>: Check output of<br>: extended address<br>: decoder<br>:<br>: Check inputs and<br>: outputs of voltage<br>: regulators |

|                                         | :                                                                             | :                                                                                                                            |

| Fails whole block of memory             | :<br>: Bad address buffer<br>:<br>:                                           | :<br>: Check address buffer<br>:<br>:                                                                                        |

| Fails at even 1K<br>sectors (1000,2000) | :<br>: No chip select<br>:<br>:                                               | :<br>: Check chip select on<br>: memory chip<br>:                                                                            |

| Fails at address OOH                    | :<br>: Problem in support<br>: circuitry<br>:<br>:                            | :<br>: Check address buffers<br>:<br>: Check data buffers<br>:                                                               |

| Fails different<br>locations            | :<br>: Bad ground connection on<br>: memory chip<br>:                         | :<br>: Check ground to all<br>: chips<br>:                                                                                   |

| Intermittent failure                    | :<br>: Dirty edge connector<br>:<br>: Bad ground connection<br>: on chip<br>: | :<br>: Clean edge connector<br>:<br>: Check ground on all<br>: chips<br>:                                                    |

## COMMON MEMORY BOARD PROBLEMS

#### SYSTEM SUPPORT 1

The System Support 1 is a multi-function board, consisting of a real time clock with battery back-up, a RS-232 serial channel, 15 levels of interrupt control, space for 4K of RAM or EPROM with battery back-up for 2K, provision for a high speed math processor, 3 independent interval timers, and PWRFAIL generation.

The system support board takes up a block of 16 I/O ports and is addressable on any 16 port boundary. These ports are used to program the various devices; 2651 USART, clock, etc. The standard port block begins at 50 hex, and all COMPUPRO software assumes that the board is addressed there.

#### **PRODUCTION TESTS**

There are several tests to check the various parts of the board. All tests assume a 64K system with either a CPU-Z or 8085/88 CPU, J13 of the system support must be jumpered accordingly. There must be a 4K window in memory from 8000 to 8fff hex (A RAM I7 or RAM 20 is useful for windows). The switches should be set as follows: S1 paddles 4 and 5 on, the rest are off, S2 paddles 1,2,3,4 on, the rest are off, S3 paddles 5 and 7 on, the rest are off. There should be 6116 RAMs in positions U16 and U17, either a 9511, 9512, or equivalent in U13, and special headers in J7 and J8 jumpered as shown below.

| J7 |   | •••••         |   |    | J 8 |   | •••••         |    |

|----|---|---------------|---|----|-----|---|---------------|----|

|    | 1 | •             | • | 16 | 1   | • | •             | 16 |

|    | 2 | •             | • | 15 | 2   | • | •             | 15 |

|    | 3 | •             | • | 14 | 3   | • | •             | 14 |

|    | 4 | •             | • | 13 | 4   | ٠ | •             | 13 |

|    | 5 | •             | • | 12 | 5   | • | •             | 12 |

|    | 6 | •             | • | 11 | 6   | • | •             | 11 |

|    | 7 | •             | • | 10 | 7   | • | •             | 10 |

|    | 8 | •             | • | 9  | 8   | • | •             | 9  |

|    |   | • • • • • • • | • |    |     | • | • • • • • • • |    |

The first test is the serial port. If the system will boot and display on the terminal, and is able to do a DIR command then it is assumed to be reading and writing correctly.

The second test is CLOCK. This routine allows you to set the time and date of the 5832 clock chip and read it back again. You must use 24 hour format and two digits to designate hours, minutes, day, etc. (this test is self-prompting on data entry format). Once everything is set and the battery hooked up the system can be turned off. The time should be correct when CLOCK is run again and displayed. If the time is off few seconds it can be adjusted by turning Cl2.

The test for the math processor is either 9511 or 9512 depending on the chip. Both tests initialize the math processor, multiply two numbers, and check the result with a known answer. If "OK" appears, everything is probably working correctly. If "PERMANENT ERROR" appears it means that the routine has tried twice to get the correct respose and failed.

The two ROM sockets are tested with a standard memory test called MEMTEST. It can be set to test any block, but we have already set the switches to our standard location of 8000 to 8fff hex. The routine will go through several different tests, if there are no errors listed when it starts to repeat then all the support circuitry is good.

The last test is for the interrupt controller and is called 8259A. When it is running "!!!!" will appear over the terminal screen. Make sure your terminal is set for wraparound. The program is waiting for a low on the vectored interrupt lines. Ground a jumper and touch the other side to each of the interrupt lines VIO to VI7. The corresponding number should be displayed. If more than one pin is touched at the same time the lowest one will be displayed, as it has the highest priority. The 8259A test also tests the timer circuitry, however it can be tested separately with the TIMER routine.

This can be very handy in troubleshooting. If you use the FIRE command, one of the timers will output a low to the VI lines it's connected to; this will be determined by J7. A RESET will output a high on the same lines. The best way to see what's happening is with a JADE BUS PROBE.

• .

| SYMPTOM                                               | : PROBABLE CAUSE                                      | : REMEDY                                                         |

|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|

| No output to<br>terminal or no<br>input from terminal | :<br>: Wrong voltages<br>:<br>:                       | :<br>: Check inputs and<br>: outputs of voltage<br>: regulators  |

|                                                       | :<br>: Bad Serial I/O                                 | :<br>: Check chips U3 and U4                                     |

|                                                       | :<br>:<br>:                                           | :<br>: Replace USART<br>:                                        |

| Garbage on screen                                     | :<br>: Wrong baud rate<br>:<br>:                      | :<br>: Check U45 and X1<br>(COMPUPRO baud is<br>: normally 9600) |

|                                                       | :<br>: Bad serial I/O<br>:<br>:                       | :<br>: Change USART and<br>: U3 and U4<br>:                      |

| Clock inaccurate                                      | : Frequency off                                       | : Adjust Cl2                                                     |

| Can`t set time/date                                   | :<br>: Bad voltage to U41<br>: at chip select and Vcc | : Check for 5V at D1<br>:                                        |

|                                                       | :<br>: Old CLOCK.CMD program                          | :<br>: Get an update                                             |

|                                                       | :<br>: X3 off freq.                                   | :<br>Replace X3                                                  |

|                                                       | :<br>: Bad clock chip                                 | :<br>Replace U41                                                 |

| Sets wrong time                                       | :<br>Wrong data to U41<br>:                           | :<br>: Check all data buffers<br>:                               |

| Won`t boot CP/M 86*                                   | :<br>No output from Ul6                               | :<br>Replace GO 86 EPROM                                         |

|                                                       | :                                                     | :<br>: Run MEMTEST to check<br>: addressing                      |

|                                                       | ;<br>;<br>;                                           | :<br>: Check chip enable on<br>: EPROM                           |

|                                                       | •                                                     | •                                                                |

COMMON SYSTEM SUPPORT 1 PROBLEMS

| SYMPTOM              | : PROBABLE CAUSE                                                              | : REMEDY                                                                                                    |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

|                      | :<br>: See "Won`t boot CP/M 86"<br>: above<br>:<br>: Interrupts bad<br>:<br>: | :<br>:<br>:<br>: Check for J8<br>:<br>: Check U14, U15,timers<br>:<br>: Check 2 MHz clock<br>: on 8253<br>: |

| Math processor fails | :<br>: Bad 9511/9512<br>:<br>: Bad clock<br>:<br>: Chip not initialized<br>:  | :<br>Replace math chip<br>Check J5 frequency<br>Check chip select                                           |

•

, .

#### INTERFACER 3

The INTERFACER 3 board features 8 fully programmable asynchronous serial channels. Two of these ports are capable of high speed synchronous transmission. Five RS-232 handshaking lines are available on each channel as well as two distinct interrupts.

The INTERFACER 3 was designed for operation in interrupt driven/multiuser systems. A total of sixteen interrupts are brought out for jumpering by the user to the eight vectored interrupt lines on the S-100 bus.

A five bit register is used as a user select register to activate the required serial channel. This feature minimizes the number of I/O ports necessary for running a multi-user system. Up to 32 users (four boards) can use the same 8 port addresses.

#### **PRODUCTION TESTS FOR THE INTERFACER 3**

There are two tests for the INTERFACER 3 boards. The test used in production is called TI3. The test used for repairs is called I3TEST.

#### TEST - TI3:

This test requires construction of test hardware. A 'master' INTERFACER 3 is used along with an INTERFACER 2. Also needed is a wire wrapped board designed for communication between the INTERFACER 2 and the board under test.

The first portion of TI3 tests the serial ports on the INTERFACER 3. Special cables are used to make it possible for the master board and the board under test to 'talk' to each other using the RS-232 handshaking lines. The handshaking lines are tested to see if they are sending or receiving signals as expected. Then the data lines are tested. What actually happens is that, while one board is sending the data the other board is receiving the data. This tests the ability to send and receive data. Each port is tested separately in this manner.

The second portion of TI3 tests the interrupt circuitry on the board. Cables run from the interrupt jumper sockets on the INTERFACER 3 to sockets on the wire wrapped board, which connect the board to an INTERFACER 2 parallel port. Again the master board and the board under test talk to each other. This time the INTERFACER 2 checks the interrupt registers on the board under test to see if it is responding to data sent to it by generating a receive interrupt. It also checks to see if it generates a transmit interrupt when it sends data out.

#### TEST - I3TEST:

This test is less complex than TI3. Each serial port is checked for a character, one after another. One port is selected at a time by a hardware jig. This jig has eight inputs and one output. The eight inputs are connected to the eight serial channels on the INTERFACER 3. (If a jig is not available, the user can either hook up multiple terminals or move the serial cable from one channel to the next.) One channel is selected at a time and hooked up to the terminal. This makes it possible to select any user, type a character and see it echoed on the screen. It also allows for examination of the handshaking lines by means of LEDs on the jig or on an RS-232 breakout box.

Interrupts are checked manually with an oscilloscope. The scope probe is placed at the point where each interrupt is brought out for jumpering to the vectored interrupt lines on the S-100 bus. When a character is generated on a port by the keyboard, an interrupt can be seen at the interrupt jumper socket.

TI3 can be stopped and stepped through one byte at a time. It is then possible to check a port at any stage of the cycle to see if it is being selected properly and if it is actually getting the data sent to it.

| SYMPTOM                                       | : PROBABLE CAUSE                                           | : REMEDY                                                                                                                         |

|-----------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Won't run at all                              | :<br>: On board supply<br>: voltages not<br>: correct<br>: | :<br>: Check voltages at the<br>: inputs and outputs of<br>: the voltage regulators<br>:                                         |

| Runs CP/M*, will<br>not run MP/M*             | :<br>: Interrupt jumpers<br>: not correct.<br>:            | :<br>: Check jumpers and<br>: replace if needed.<br>:                                                                            |

|                                               | :<br>: Interrupts not being<br>: generated properly<br>:   | :<br>: Use TI3 to check for<br>: interrupts at the<br>: jumpers                                                                  |

| Garbageonthe<br>screen                        | :<br>: Bad baud clock<br>:<br>:<br>:<br>:<br>:             | :<br>: Checkclockgenerator<br>: output<br>:<br>: Check clock inputs to<br>: the USART's<br>:                                     |

| One channel<br>does not work                  | :<br>Channel not<br>: selected<br>:<br>:<br>Bad USART<br>: | :<br>Use TI3 to check if<br>channel is being<br>selected<br>:<br>Use TI3 to check<br>handshaking lines,<br>and to see if correct |

|                                               | :<br>:<br>: Bad RS-232 driver<br>: or receiver<br>:        | <ul> <li>data is echoed on to</li> <li>the screen.</li> <li>Check handshaking</li> <li>lines with TI3.</li> </ul>                |

| Printer will<br>not work with<br>INTERFACER 3 | :<br>: Bad RS-232 driver<br>: or receiver<br>:             | :<br>: Check handshaking<br>: lines with TI3.<br>:                                                                               |

## COMMON INTERFACER 3 PROBLEMS

~

#### INTERFACER 4

The INTERFACER 4 board features 3 fully programmable asynchronous serial channels, two of which are capable of high speed synchronous transmission and one capable of current loop operation. Each channel has five RS-232 handshaking lines, two distinct transmit and receive interrupts and bi-directional clock drivers. Also featured on the board is a pin compatible CENTRONICS parallel interface port with handshaking lines, and a universal parallel port with 16 data, and 3 handshaking lines.

The INTERFACER 4 was designed for operation in interrupt driven/multiuser systems as well as single user systems. A user select register is used to activate the required port. This feature minimizes the number of I/O ports necessary for using several INTERFACER 3 or 4 boards.

#### PRODUCTION TESTS FOR THE INTERFACER 4

There is one test for the INTERFACER 4 in production. This is the I4A test. This test is broken down into several different tests for the purpose of repairs. These are, I4TEST, CTEST, I4PTST, DIPTST and I4INT.

I4A: This test requires construction if test hardware. A master INTERFACER 4 is used along with an INTERFACER 2. A wire wrapped board interfaces an INTERFACER 2 to the board under test. A printer with a CENTRONICS interface is also used.

The first portion of I4A tests the serial ports on the INTERFACER 4. Special cables are used to make it possible for the master board and the board under test to talk to each other using the RS-232 lines with handshaking. The handshaking lines are tested to see if they are sending or receiving signals as expected. Then the data lines are tested. What actually happens is that while one board is sending the data the other board is receiving the data. Each serial port is tested in this manner.

- Next the CENTRONICS port is tested. This part of the test simply sends data to the printer using the handshaking lines. This tests the data lines and the handshaking lines as well as the status buffer on the board.

- The universal parallel port is then tested. The port is connected to a parallel port on the INTERFACER 2 through the wire wrapped board. All combinations of data are transmitted by the board under test and received by the INTERFACER 2. Then, as in the serial part of the test, the data is sent to the board under test. This tests the ability of the port to send and receive data correctly.

- The next part of the test checks to see if the DIP switch Sl works correctly. This test expects to see a logical 1 come through when the switch is off and a logical 0 when the switch is on. First the program looks for all 1s one S1 3-10 then looks for all 0s on S1 3-10. If anything else is present an error message will be displayed and the test will be terminated.

- Finally, the interrupt circuitry is tested. Cables run from the interrupt jumper sockets on the INTERFACER 4 to sockets on the wire wrapped board, which connect the board to an INTERFACER 2 parallel port. The master board and the board under test talk to each other. The INTERFACER 2 checks the interrupt registers on the board under test to see if it is responding to data sent to it by generating a receive interrupt. It also checks to see if it generates a transmit interrupt when it sends data out.

#### **REPAIR TESTS**

There are several different tests used in the repair of the INTERFACER 4. They are designed to test each portion of the board independently. They also allow for more control on the part of the technician.

I4TEST tests the serial ports on the board. One channel is selected at a time and hooked up to the terminal. This makes it possible to select any user, type a character and see it echoed on the screen. It also allows for examination of the handshaking lines by means of LEDs. Three inputs to a hardware jig are connected to the three serial channels on the INTERFACER 4. Each port is checked character by character. Moving the terminal cable is acceptable if the jig is not available.

Interrupts are also tested with I4TEST. Interrupts are checked manually with an oscilloscope. The scope probe is placed at the point where each interrupt is brought out for jumpering to the vectored interrupt lines on the S-100 bus. When a character is generated on a port by the keyboard, an interrupt can be seen at the interrupt jumper socket.

- CTEST tests the CENTRONICS port on the INTERFACER 4. Data is simply sent to a printer through the CENTRONICS port, making use of the handshaking lines. The results are checked by examining the message printed by the printer. A <SPACE> will end the test.

- I4PTST tests the parallel port on the INTERFACER 4. This test works like the test for the serial ports. All combinations of data are sent to the parallel port on the INTERFACER 4 from the INTERFACER 2 through the wire wrapped board. The data is then sent from the INTERFACER 4 to the INTERFACER 2.

DIPTST test the dip switch on the INTERFACER 4. A hardware box containing a set of switches is connected to the parallel port connector. LEDs are used to indicate the logic level of each paddle of the dip switch Sl on the INTERFACER 4. When one of the paddles is switched the logic level will change and should be indicated by the LEDs.

## COMMON INTERFACER 4 PROBLEMS

| Symptom                                       | : PROBABLE CAUSE                                                                                     | : REMEDY                                                                                                                                                                 |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Won´t run at all                              | :<br>: On board voltages not<br>: correct<br>:<br>:                                                  | :<br>: Check voltages at the<br>: inputs and outputs of<br>: voltage regulators<br>:                                                                                     |

| Runs CP/M, will<br>not run MP/M               | :<br>: Interrupt jumpers not<br>: correct<br>:<br>: Interruptsnot being<br>: generated properly<br>: | :<br>: Check jumpers and<br>: replace as needed<br>:<br>: Use I4TEST to trace<br>: interrupts at jumpers<br>:                                                            |

| Garbage on screen                             | :<br>Bad baud clock<br>:<br>:<br>:                                                                   | :<br>: Check clock generator<br>: output<br>:<br>: Check clock inputs to<br>: the USART's<br>:                                                                           |

| One serial channel<br>does not work           | :<br>Channel not selected<br>:<br>Bad USART<br>or<br>Bad RS-232 driver<br>: or receiver<br>:         | :<br>Use I4TEST to check if<br>channel is being selected<br>Use I4TEST to check hand-<br>shaking lines, and to see<br>if correct data is echoed<br>on to the screen<br>: |

| Printer will not<br>work on serial<br>channel | :<br>: Bad RS-232 line driver<br>: or receiver<br>:<br>:                                             | :<br>: Check data and<br>: handshaking lines<br>: with I4TEST<br>:                                                                                                       |

| SYMPTOM                                                | : PROB               | ABLE CAUSE | : | REMEDY                                                                       |

|--------------------------------------------------------|----------------------|------------|---|------------------------------------------------------------------------------|

| CENTRONICS port<br>not printing                        | :<br>: No strob<br>: | e signal   |   | Check strobe output at<br>U9 pin ll using CTEST                              |

|                                                        | : Bad data<br>:<br>: | buffer     | : | Check outputs and enable<br>of data buffer Ull using<br>CTEST                |

|                                                        | : Incorrec<br>:<br>: | t status   | : | Check outputs of status<br>buffer U12 (should be<br>C5 Hex when SRD* is low) |

| CENTRONICS port<br>printing garbage                    | :<br>: Incorrec<br>: | t status   | : | Check outputs of status<br>buffer U12 using CTEST                            |

|                                                        | : Bad data<br>:<br>: | buffer     | : | Check outputs and enable<br>of data buffer Ull using<br>CTEST                |

| Printer on<br>UNIVERSAL parallel<br>port prints garbag | :                    | buffer     | : | Check outputs of data<br>buffers U6 and U7 using<br>I4PTST                   |

.

#### DISK 1

The DISK 1 controller board is usually responsible for booting the system and handling the transfer of all data between the floppy disk sub system and the main memory in the enclosure. In order to perform this task the CPU issues the necessary commands to the DISK 1 controller chip, the 3272. Some versions may have the equivalent 765 chip. Commands may be from one to nine bytes in length. There are 15 seperate commands for the controller chip. These commands are listed on page 32 of the DISK 1 manual.

A command is issued by the CPU one byte at a time. After the 8272 receives a command byte, the CPU must poll the status register of the 8272 to see if the 8272 is ready to receive the next command byte. After the complete command has been received the 8272 may request a DMA cycle. If the system is functioning properly, and no other board is requesting the bus, the CPU will grant control of the bus to the DISK 1. At this point the DISK 1 will generate all control and status strobes for the system. It will also have access to the system memory and will either read from or write to the floppy disk drives. The DISK 1 transfers one byte of data per DMA request rather than multiple byte hog or burst mode.

#### PRODUCTION TESTS

DSKTST: This is a combination of individual tests that check the DISK I's ability to seek, read, write, and select drives. DSKTST treats all diskettes as single-sided. Any screening operation should also use a program that knows about double-sided diskettes, such as FORMAT. The following is the menu of commands available with DSKTST:

#### DSKTST

- 0 CONFIDENCE TEST

- 1 SEEK TEST

- 2 READ/DISPLAY TRACK, SECTOR

- 3 READ TEST

- 4 WRITE VERIFY READ TEST

- 5 RANDOM SEEK, READ/WRITE

- \* DISPLAY ALL CONTROLLED STATUS BYTES

- D SELECT DRIVE

- E DISPLAY AND CLEAR ERROR COUNT

- F FORMAT A DISKETTE

- H HELP ME

- R RESTART TEST

- S SET MODE OF DISK (SINGLE, DOUBLE)

- X EXIT BACK TO CP/M\*

SPECIFY DRIVE (A:-D:)

- 0 THE CONFIDENCE TEST: This test is a combination of tests 1,3,4, and and 5.

- 1 SEEK TEST: This test has the drive seek between tracks. There are a variety of patterns, e.g. trk 0, trk 1, trk 0, trk 2, trk 0, trk 3, etc.

- 2 READ/DISPLAY TRACK SECTOR: This test dumps out data from the diskette. It gives the operator the choice of which track and sector he wishes to view. This is useful for dumping a specific sector's data from the diskette.

- 3 READ TEST: This test reads data from the diskette starting at track 0 and sequentially reads each sector and track. Each sector is checked for errors.

- 4 WRITE VERIFY, READ TEST: This test writes sectors of F0 hex out to the diskette and reads them back again. F0 is thought to be the most difficult byte to successfully write and read.

- 5 RANDOM SEEK READ/WRITE: This test selects a random track, goes out and reads its headers, and confirms that it is on the proper track. It writes data to a sector and confirms that the data is correct. Then it steps to a new track and repeats the process.

- \* DISPLAY ALL CONTROLLER STATUS BYTES: If this key is pressed and any of the DSKTST selections are run, the first byte will be displayed each time a command is given to the 8272.

- D SELECT DRIVE: this gives the operator a choice of drives A D.

- E DISPLAY AND CLEAR ERROR COUNT: There are four memory locations that hold the error count for,

READ ERRORS: WRITE ERRORS: SEEK ERRORS: SOFT ERRORS:

This command reads these memory locations and then clears them. When a hard error occurs, DSKTST displays what command was given and the resulting status bytes. This is a read error:

```

ERROR, Func=46 Status bytes=40 01 00 08 00 01 03

```

Read 2d command Status 0,1,2,trk,head,sector,density

An explanation of the 8272's commands and status bytes begins on page 34 of the DISK 1 manual.

F - FORMAT A DISKETTE: This command calls up the format routine. It formats only one side of the diskette.

- H HELP ME: This or any other undefined letter calls up the DSKTST menu.

- R RESTART TEST: This command also calls the DSKTST menu.

- S SET MODE OF DISK: This command allows the user the ability to inform the program at what density the diskette is formatted.

- X EXIT BACK TO CP/M: This command returns the user back to the operating system.

In house testing of the DISK 1 consists of booting up the system, adjusting the data separator (phase lock loop), formatting single and double sided diskettes at both single (128 bytes per sector) and double (1024 bps) density. Then the TMA arbitration circuit is tested while DSKTEST option 0 is running.

BOOTING THE SYSTEM: The EPROM on board the DISK 1 contains the necessary code to boot the system. 8080 code is provided for 8085 and Z-80 processors. 8086 code is provided for the 8088, 8086, and the 286 CPUs. 68000 code is provided for the 68000 processor.

This EPROM contains the instructions the 8272 needs to begin loading the CP/M operating system off the diskette into the system memory. Requirements for booting are a CPU, enough static RAM for your CP/M (usually 64K), a DISK 1, at least one floppy disk drive and a COMPUPRO CP/M diskette matching the processor.

ADJUSTING THE DATA SEPARATOR: Place a scope probe on the right side of R9, adjust your scope to approximately .5 volts/division and 1 ms per division. Run DSKTST and select the appropriate drive and select test option #3 (read data). The 8272 will begin to read data off the drive. The signal on the scope will appear as a wide band, with a narrower band in the center. The narrow band will arch up or down as the trimpot R35 is adjusted with a screw driver. The desired result is for the narrow band to have no arch at all and to be centered in the broad band. With the signal in this position, the phase lock loop is properly adjusted.

FORMATTING A DISKETTE: Place a double sided diskette in drive B: and call up the FORMAT routine. Format the disk twice, once at 128 bytes per sector (single density) and once at 1024 byte per sector (double density).

On the screen an  $\mathcal{F}$  will appear as each track is formatted. Then the format will be verified. If a  $\mathcal{V}$  appears for each sector, all is well. If an  $\mathcal{S}$  appears for any track a soft error has been detected. These errors indicate that the phase lock loop had some trouble in reading the data during verification. If an  $\mathcal{E}$  appears a hard error has been detected. These errors indicate that the DISK l could not read the data and the data was not received by the system. The severity of the problem is shown by the number of errors present when the verification is complete.

#### TESTING THE T.M.A. ARBITRATION CIRCUIT:

DMATST: This test is designed to test the DMA assertion of the DISK 1. The test simply utilizes the MPX to assert its priority, which is lower than the DISK 1, and make sure the DISK 1 still gains control of the bus.

To run this test two additions must be made to the standard system: a MPX-1 board and a 64K RAM board. The Ram board is necessary because the mode in which the MPX-1 asserts its priority is by accessing system memory, at extended page 1. If DMATST is run and there is no MPX, the message will state 'loading MPX' and the system will crash. This is because the test received no information back form the MPX-1. If there is an MPX 1, but no RAM, the message will state that the MPX-1 was loaded with a program, but when it went to search for system memory, it found none.

To terminate the MPX, the program DMAEND is invoked. This will tell the MPX to stop searching, and also print out whether there have been any memory errors while it was running.

| Parameters: | Standard COMPUPRO serial configurations |  |  |

|-------------|-----------------------------------------|--|--|

|             | MPX DMA priority is OEH                 |  |  |

|             | RAM is from 10000H to 1FFFFH            |  |  |

|             | MPX attention port is OFH               |  |  |

Switch Settings:

| MPX | S1     | S2     | RAM 17 S1 | S2        |

|-----|--------|--------|-----------|-----------|

|     | off on | off on | off       | on off on |

|     | 1 x    | x 1    | x 1       | x 1       |

|     | x 2    | x 2    | 2         | x 2 x     |

|     | x 3    | x 3    | 3         | x 3 x     |

|     | x 4    | x 4    | 4         | x 4 x     |

|     | x 5    | 5 x    | 5         | x 5 x     |

|     | 6 x    | 6 x    | 6         | x 6 x     |

|     | 7 x    | 7 x    | 7         | x 7 x     |

|     | x 8    | x 8    | 8         | x 8 x     |

|     |        |        | 9         | x x 9     |

|     |        |        | 10        | x 10 x    |

SINGLE STEPPING TECHNIQUE: A useful technique for troubleshooting the DISK 1 is single stepping through the EPROM boot program. A listing of the PROM is available on the master CP/M 2.2 diskette in the file named GBROM.ASM.

This method of troubleshooting is particularly helpful when the system will not boot up. The address and data lines can be examined easily as well as control signals. The DATA INT signal can be examined to see if it is being received by the CPU. DATA INT is fed through U9 (port C2) to become data bit 7. It is sent to the CPU on the data bus. It indicates that the 8272 completed the previous instruction.

There are two locations in the boot PROM where data bit 7 is polled by the CPU. The first is RCAL2: this is located after the recalibrate drive command. The second is located after the read command. It is labeled READ2.

A word of caution- the single stepping device e.g. the Jade bus probe or the front panel, may show that data bit 7 is being generated when in reality it is floating. This should be checked with a scope or logic probe.

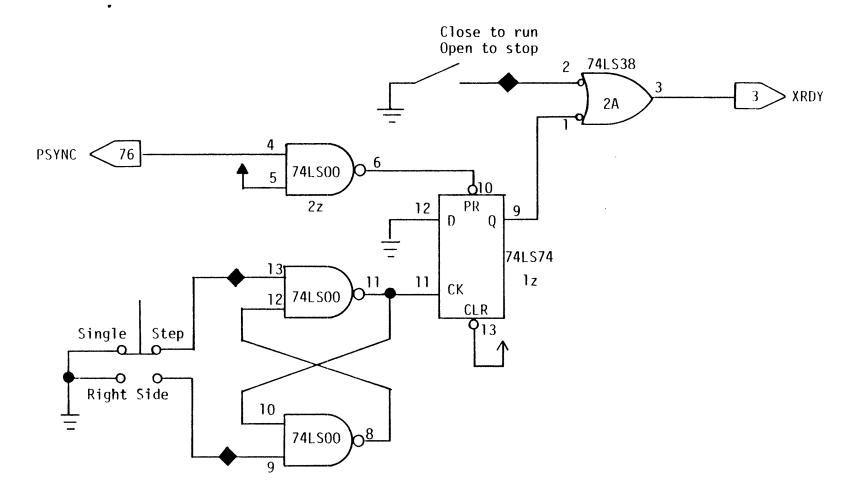

Single stepping through the DMA cycle can also be helpful. In order to do this XRDY and RDY should be shorted together and held low to stop the system. Then open the doors on the drives and lift pin 1 of U8. Using a logic probe short the lifted pin 1 to its respective socket pin. The probe should show a low. While holding the probe in place reset the system. Wait a moment then stop the system and remove the logic probe. Then single step once. The address bus should show 00 01 00 hex, the TMA and disable lines should be asserted. The purpose of this procedure is to make sure the DISK 1 is initializing the DMA address properly.

| SYMPTOM                          | PROBABLE CAUSE                                      | : REMEDY                                                                                                                          |

|----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| System won't boot                | :<br>Bad voltages on board<br>:<br>:                | :<br>: Check voltages at<br>: inputs and output of<br>: voltage regulators                                                        |

|                                  | :<br>: Bad clock to controller<br>: chip            | :<br>Check clock on U14<br>:                                                                                                      |

|                                  | :<br>: No board select<br>:                         | :<br>Check BDSEL* on U40                                                                                                          |

|                                  | : Bad address buffer<br>:                           | Check U41 and U19                                                                                                                 |

|                                  | : Bad disk drive or<br>: diskette                   | : Swap with known<br>: good ones                                                                                                  |

| Head loads once<br>then crashes  | :<br>: Incorrect DMA address<br>:<br>:<br>:<br>:    | :<br>: Check data buffers<br>: U44 and U5<br>: DMA counters U12<br>: U13,U25,U26,U29,&U30<br>: Address buffers<br>: U43, U42, U39 |

|                                  | : Bad or wrong diskette<br>:                        | : Try another disk<br>:                                                                                                           |

| Clicking sound over<br>andover : | :<br>: EPROM not disabled<br>:<br>:                 | :<br>: Check U24a for<br>: SER OUT STB* to<br>: produceBOOT DIS*<br>: that negates BOOT<br>:                                      |

| Head loads over<br>and over      | :<br>: Phase lock loop out<br>: of adjustment       | :<br>: Adjust R35<br>:                                                                                                            |

|                                  | :<br>P.L.L. defective<br>:<br>:                     | :<br>: Check P.L.L circuit<br>: shown on pg. 50<br>: of DISK 1 manual<br>:                                                        |

|                                  | :<br>: DISK 1 is not scanning<br>: drives<br>:<br>: | :<br>: Check U31 inputs<br>: and outputs<br>:                                                                                     |

COMMON DISK 1 PROBLEMS

~

| SYMPTOM                                              | : PROBABLE CAUSE                                                                                                              | : REMEDY                                                                                                                                                                                   |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Soft errors on<br>format                             | :<br>Phase lock loop out<br>of adj.<br>:<br>:                                                                                 | :<br>Adjust R35<br>:<br>:<br>: Swap U5 and/or U19<br>:                                                                                                                                     |

| Lights on both<br>drives brightly lit                | :<br>: 50 pin cable connected<br>: backwards<br>:                                                                             | :<br>: Turn cable around<br>: on one end<br>:                                                                                                                                              |

| Hard errors on<br>format between<br>tracks 41 and 76 | :<br>Bad resistor at R27<br>Bad pulse on U34 pin 6<br>:<br>:                                                                  | :<br>: Check R27 for<br>: correct value<br>:<br>: Check U34 for<br>: COMPWRITE*, should<br>: change pulse width<br>: at track 41 from<br>: 1.6us to 1.3us, 1.5<br>: on double density<br>: |

| -                                                    | :<br>P.L.L. circuitry is not<br>going to double density<br>mode<br>:<br>DATA pulse from U19a not<br>dropping from lus to .5us | : chip<br>:<br>: Check to see MFM<br>: line is grounded<br>:                                                                                                                               |

#### DISK 1A

The DISK 1A controller board is essentially identical to the DISK 1 board except it has the ability to run both 8" and 5 1/4" drives at the same time. Additional features include the ability to have a larger EPROM with more routines, digital instead of analog data separation and write pulse generation, and alternate drive select and head load capability with motor timeout. The only feature missing from the DISK 1A is the software serial port. Since the DISK 1A uses the same controller chip and has all same port addressing that the DISK 1 had, it is software compatible. All the new features of the DISK 1A were added to the unused ports and bit positions of the DISK 1.

#### **PRODUCTION TESTS**

The production tests are almost identical to the DISK 1 production tests, and we refer you at this time to the DISK 1 section for an explanation of the first tests for the DISK 1A.

DSKTST: See DISK 1 section.

In house testing of the DISK 1A consists of booting up the system, formatting double sided diskettes at both single (128 bytes per sector) and double (1024 bps) density in both 8" and 5 1/4" drives. Then the TMA arbitration circuit is tested while DSKTEST option 0 is running. Finally a PIP test is run to verify that data can be passed between the 8" and 5 1/4" floppies.

BOOTING THE SYSTEM: The EPROM on board the DISK 1A contains the necessary code to boot the system. 8080 code is provided for 8085 and 2-80 processors. 8086 code is provided for the 8088, 8086, and the 286 CPUs. 68000 code is provided for the 68000 processor.

This EPROM contains the instructions the 8272 needs to begin loading the CP/M operating system off the diskette into the system memory. Requirements for booting are a CPU, enough static RAM for your CP/M (usually 64K), a DISK 1A, two floppy disk drives and a COMPUPRO CP/M diskette matching the processor.

ADJUSTING THE DATA SEPARATOR: Since the data separator is entirely digital and contained in the one 8 pin IC (U 10), no adjustment is neccesary.

FORMATTING A DISKETTE: Place a double sided diskette in drive B: and call up the FORMAT routine. Format the disk twice, once at 128 bytes per sector (single density) and once at 1024 byte per sector (double density).

On the screen an  $\mathcal{F}$  will appear as each track is formatted. Then the format will be verified. If a  $\mathcal{V}$  appears for each sector, all is

well. If an '3' appears for any track a soft error has been detected. These errors indicate that the phase lock loop had some trouble in reading the data during verification. If an 'E' appears a hard error has been detected. These errors indicate that the DISK IA could not read the data and the data was not received by the system. The severity of the problem is shown by the number of errors present when the verification is complete.

#### TESTING THE T.M.A. ARBITRATION CIRCUIT:

DMATST: This test is identical to that of the DISK 1, and we refer you to this section under DISK 1.

SINGLE STEPPING TECHNIQUE: A useful technique for troubleshooting the DISK 1A is single stepping through the EPROM boot program. A listing of the PROM is available on the master CP/M 2.2 diskette in the file named GBROM.ASM.

This method of troubleshooting is particularly helpful when the system will not boot up. The address and data lines can be examined easily as well as control signals. The CINT signal can be examined to see if it is being received by the CPU. CINT is fed through U9 (port C2) to become data bit 7. It is sent to the CPU on the data bus. It indicates that the 8272 completed the previous instruction.

There are two locations in the boot PROM where data bit 7 is polled by the CPU. The first is RCAL2: this is located after the recalibrate drive command. The second is located after the read command. It is labeled READ2.

A word of caution- the single stepping device e.g. the Jade bus probe or the front panel, may show that data bit 7 is being generated when in reality it is floating. This should be checked with a scope or logic probe.

Single stepping through the DMA cycle can also be helpful. In order to do this XRDY and RDY should be shorted together and held low to stop the system (this allows the bus probe to stop the DMA cycle). Then open the doors on the drives and lift pin 2 of U2. Using a logic probe short the lifted pin 2 to its respective socket pin. The probe should show a low. While holding the probe in place reset the system. Wait a moment then stop the system and remove the logic probe. Then single step once. The address bus should show 00 01 00 hex, the TMA and disable lines should be asserted. The purpose of this procedure is to make sure the DISK 1A is initializing the DMA address properly.

Board Products Section

.

.

| S YMPTOM                         | : PROBABLE CAUSE                                     | : REMEDY                                                                                                          |

|----------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| System won't boot                | :<br>: Bad voltages on board<br>:<br>:               | :<br>: Check voltages at<br>: inputs and output of<br>: voltage regulators                                        |

|                                  | :<br>Bad clock to controller<br>chip                 | :<br>: Check clock on Ul4<br>: pins 19 and 21                                                                     |

|                                  | : No board select                                    | : Check BDSEL* on U45                                                                                             |

|                                  | : Bad address buffer                                 | : Check U46 and U33                                                                                               |

|                                  | : Bad disk drive or<br>: diskette                    | : Swap with known<br>: good ones                                                                                  |

| Head loads once<br>then crashes  | :<br>Incorrect DMA address<br>:<br>:<br>:<br>:       | :<br>: Check data buffers<br>: U50 and U51<br>: DMA counters U22-24,<br>: U35-37<br>: Address buffers<br>: U47-49 |

|                                  | : Bad or wrong diskette<br>:                         | : Try another disk<br>:                                                                                           |

| Clicking sound over<br>and over  | :<br>: EPROM not disabled<br>:<br>:<br>:             | :<br>: Check U56a for<br>: MTR STB* to<br>: produce <not> BOOT<br/>: that negates PROM<br/>: EN*</not>            |

| Head loads over<br>and over      | :<br>: Data on diskette bad<br>:                     | :<br>: Use good diskette<br>:                                                                                     |

|                                  | :<br>P.L.L. defective<br>:<br>:                      | :<br>: Check P.L.L circuit<br>: for required<br>: signals<br>:                                                    |

| Lights on drives<br>do not blink | :<br>: DISK 1A is not scanning<br>: drives<br>:<br>: | :<br>: Check U5 inputs<br>: and outputs, and<br>: J1-4 for proper<br>: drive size                                 |

COMMON DISK 1A PROBLEMS

| SYMPTOM                               | : PROBABLE CAUSE                                                                   | : REMEDY                                                          |

|---------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Soft errors on<br>Sormat, or read     | :<br>: Drive bad or out of<br>: alignment<br>:<br>: Data separator bad<br>:        | :<br>: Replace with known<br>: good drive<br>:<br>: Swap U10<br>: |

| Lights on both<br>drives brightly lit | :<br>: 50 pin cable connected<br>: backwards<br>:                                  | :<br>: Turn cable around<br>: on one end<br>:                     |

| -                                     | :<br>P.L.L. circuitry is not<br>: going to double density<br>: mode<br>:<br>:<br>: | •                                                                 |

# DISK2 and SELECTOR CHANNEL

The DISK2 and SELECTOR CHANNEL are a two-board set designed to control Winchester hard disk drives of the Shugart SA4000 type interface. Such drives include the Shugart SA4000 series as well as the Fujitsu 2300 series. Software drivers which support one drive (not multiple drives) are currently available for the Fujitsu 2301 (10 Mbyte) and 2302 (20 Mbyte) drives. Shugart drives are not currently supported in software. Software drivers for other hard disk drives may be available from CompuPro or CompuPro system centers in the future. It should be noted that Memorex 101 series drives of 1982 vintage or later are actually relabelled Fujitsu 2300 series drives and are supported in CompuPro software.

The DISK2 board has the hardware to perform reads, writes and seeks on the disk drives, and to request, arbitrate and accept control of the system bus. The SELECTOR CHANNEL hardware drives the address, control and status lines on the system bus during DMA cycles. The DISK2 cannot function without a companion SELECTOR CHANNEL. The SELECTOR CHANNEL could serve as companion to other DMA devices that are designed to use it, though no such devices have been produced.

The heart of the DISK2 is a finite state machine; essential ly a CPU implemented in a prom sequencer. Address bits serve as instruction input and data output serves as control signals. Three of the address bit inputs to the finite state machine are driven by a command register, while the other address input bits are fed back from the machine's latched outputs. Macroinstructions are loaded in from the command register and clocked through their micro-steps by a counter. The micro-instructions can either hang waiting for a condition to come true or continue until the macro-instruction is completed. Such a design technique was chosen because it affords high-speed, low-cost controller circuitry.

The rest of the DISK2 circuitry is summarized as follows:

1. disk drive interface circuitry including:

a) a universal shift register and related circuitry for conversion from parallel to serial (write) and serial to parallel (read)

b) cyclic redundancy check (CRC) circuitry for confirming that data transfer was performed without error for both header fields and data fields (the CRC circuitry actually compares header fields as they are read off the disk to header fields stored in buffers and notifies control circuitry when a desired header has been found). 2. S100 bus interface circuitry including:

a) DMA arbitration circuitry

b) registers which hold command and status bytes, and track, head and sector header information

The SELECTOR CHANNEL hardware can be divided into three blocks:

a) system address, control and status line buffer/drivers and timing circuitry for DMA transfers

b) registers which hold command and status bytes

c) hard disk boot prom circuitry

## PRODUCTION TESTS

The production tests for the DISK1 and SELECTOR CHANNEL are the same except that there is an additional test for the SELECTOR CHANNEL which confirms proper operation of its boot circuitry.

Part of the test simply involves accessing the hard disk under the CP/M operating system. The more demanding part of the test is a program written in the Forth programming language which exercises the read, write and format circuitry of ther DISK 2. (Some component routines of the FORTH language test program have changed since the last release of this training manual.)

Here are the steps of the production test.

1. Type "DIR X:". This test simply uses the CP/M command DIR X:, where X = a logical drive on the hard disk which has files on it. Successful execution of this command confirms that the controller set can actually talk to the disk under control of CP/M. Error messages such as "BDOS ERROR on DRIVE X" indicate a failure of the test.

2. Type "PD2". This loads an exhaustive Forth language test that can manipulate the controller hardware with a series of very simple commands.

3. Type "PROT". This runs a series of routines which accomplish the following sequence of actions:

a) read a given sector to synchronize the Johnson counter,

b) format the first 16 cylinders,

c) write data to sectors just formatted,

d) write data to sectors at the outer, middle and inner cylinders of the disk,

e) read and check data just written,

f) repeat steps d & e with a complimentary data patter,

g) and finally, destroy some of the newly formatted headers to make sure that the next controller tested will have to format its own headers in order to pass the test

The above test assures that the controller can read from, write to, and format the disk drive without error. When the test

detects a failure, it suspends operation and displays the DISK2 status byte and sector number for the error detected. Also, while the test is running, a transistor which inhibits writing to the hard disk on power down is tested. The transistor emitter node voltage is examined with a scope probe ensuring that it dips below 0.5 volts on writes and rises above +2.0 volts when not writing, thus ensuring that the write gate is turning on and off.