# CONTENTS

|                                                                                                                                                                                                      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 1                                                                                                                                                                                            | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1<br>1.1.1<br>1.1.2<br>1.1.2.1<br>1.1.2.2<br>1.1.2.3<br>1.1.2.4<br>1.1.2.5<br>1.1.3<br>1.1.4<br>1.1.4.1<br>1.1.4.2<br>1.1.4.3<br>1.1.4.3<br>1.1.4.4<br>1.1.4.5<br>1.2.3<br>1.3.1<br>1.3.2<br>1.3.3 | GENERAL DESCRIPTION. 1-1  Key Features. 1-1  Physical Components. 1-1  MF20 Logic Assembly. 1-1  KW20 Master Oscillator. 1-4  Power Supply. 1-4  KL10 CPU Modifications. 1-4  Miscellaneous Components. 1-4  Configurations. 1-5  Technical Overview. 1-7  Timing and Control. 1-7  Configuration and Patching. 1-7  Error Detection and Correction. 1-8  Fault Isolation. 1-8  Summary. 1-8  MF20 SYSTEM SPECIFICATIONS. 1-8  REFERENCES. 1-10  Drawings. 1-10  Hardware Documentation. 1-10  Software Documentation. 1-11 |

| CHAPTER 2                                                                                                                                                                                            | SITE PREPARATION AND PLANNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.3.1<br>2.3.1.2<br>2.3.2<br>2.3.3<br>2.4                                                                                                                     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 3                                                                                                                                                                                            | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.4<br>3.4.1<br>3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.4.2.3                                                                                                        | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 3.4.2.4<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5                                                                                               | MF20-LK/LL  INSTALLATION OVERVIEW  Installing an MF20-LA/LB.  Installing an MF20-LC/LD.  Installing an MF20-LH/LJ.  Installing an MF20-LK/LL.  Installing an MF20-E.                                                                                                                                                                                              | .3-10<br>.3-10<br>.3-11<br>.3-12                                                        |

| CHAPTER 4                                                                                                                                                 | OPERATION/PROGRAMMING                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 4.1<br>4.1.1<br>4.1.2<br>4.2.1<br>4.2.2<br>4.3.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.5<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8<br>4.3.9<br>4.3.10<br>4.3.11     | OPERATOR CONTROLS AND INDICATORS Controls                                                                                                                                                                                                                                                                                                                         | .4-1<br>.4-1<br>.4-2<br>.4-6<br>.4-8<br>.4-13<br>.4-16<br>.4-16<br>.4-20                |

| CHAPTER 5                                                                                                                                                 | TECHNICAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

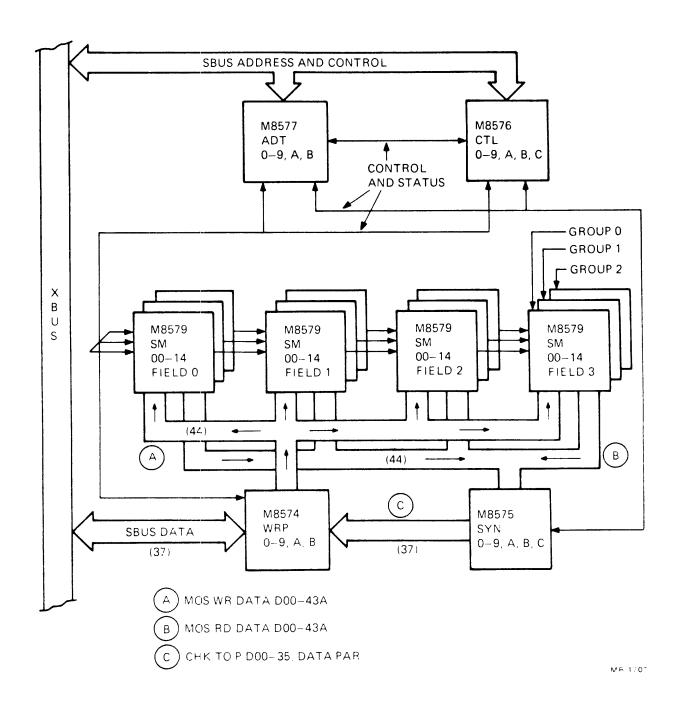

| 5.1<br>5.1.1<br>5.1.1.2<br>5.1.1.3<br>5.1.1.4<br>5.1.1.5<br>5.1.1.6<br>5.1.2<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3<br>5.3.1 | INTRODUCTION.  MF20 Conceptual Block Diagram  MOS Storage Array.  Control Section.  Data Paths.  Master Oscillator.  Power Supply.  XBus.  Summary.  MF20 MODULE BLOCK DIAGRAM.  Storage Module - M8579.  Write Path - M8574.  Syndrome - M8575.  Address and Timing - M8577.  Control and Timing - M8576.  Summary.  STORAGE ARRAY ORGANIZATION.  Storage Units. | 5-1<br>5-1<br>5-3<br>5-3<br>5-3<br>5-3<br>5-4<br>5-4<br>5-6<br>5-6<br>5-7<br>5-8<br>5-9 |

|                  | Page                            |

|------------------|---------------------------------|

| 5.3.2            | Storage Array Access5-9         |

| 5.3.3            | Summary5-9                      |

| 5.4              | FUNCTIONAL BLOCK DIAGRAMS5-9    |

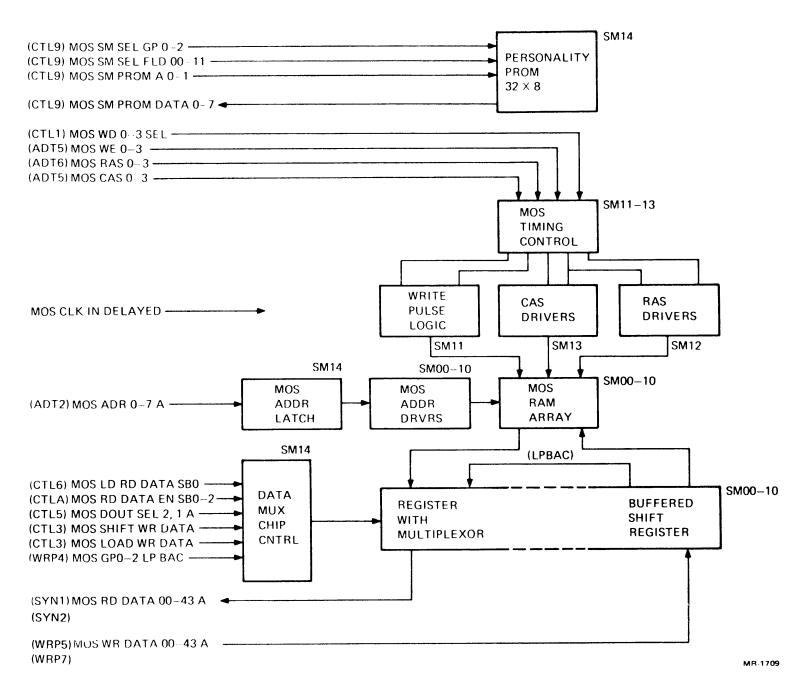

| 5.4.1            | M8579 Storage Module5-11        |

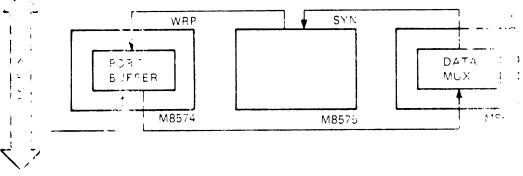

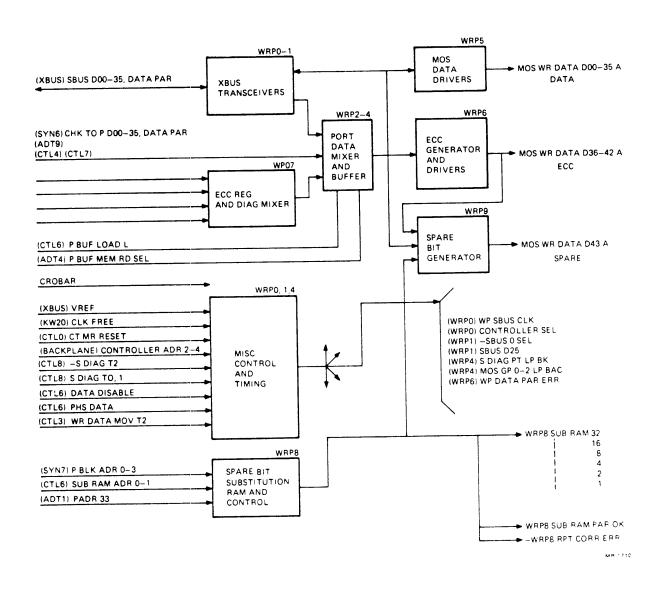

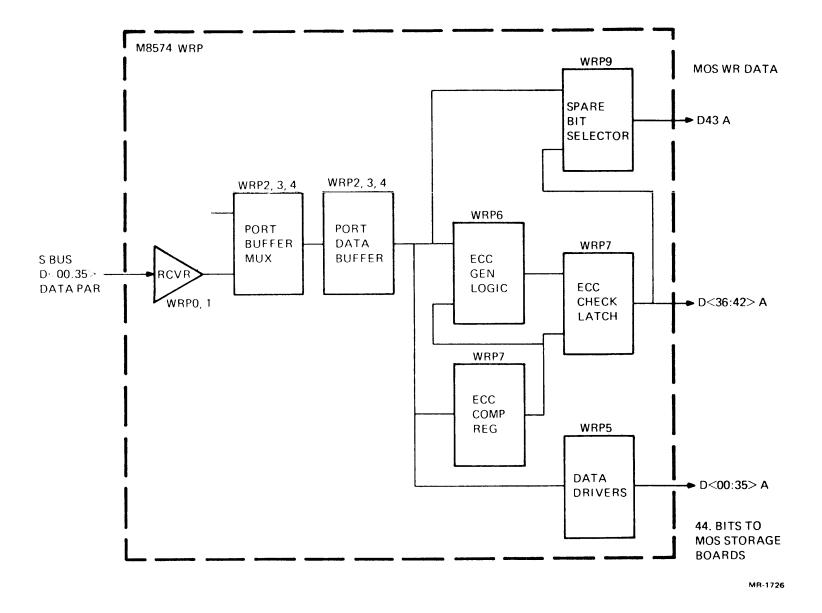

| 5.4.2            | M8574 Write Path5-13            |

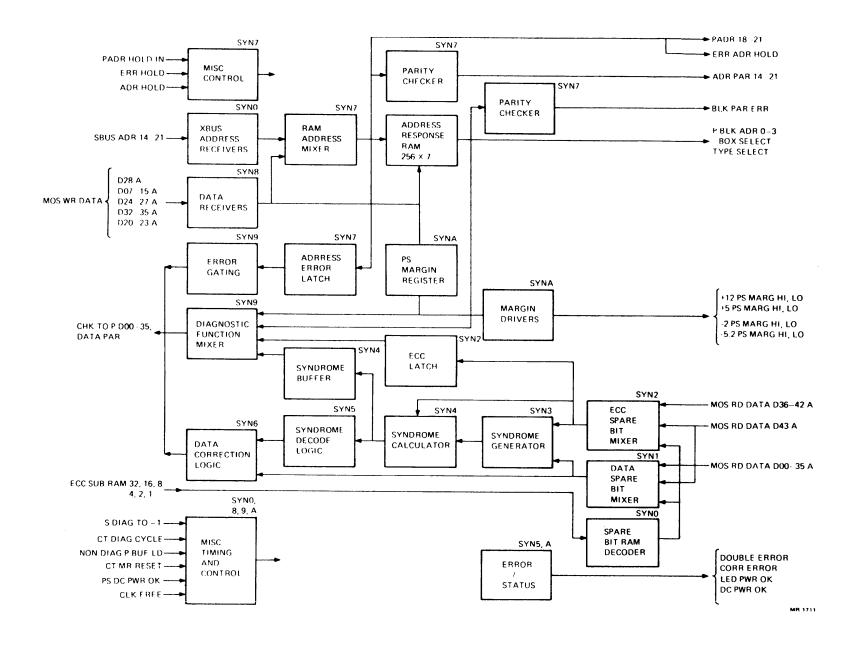

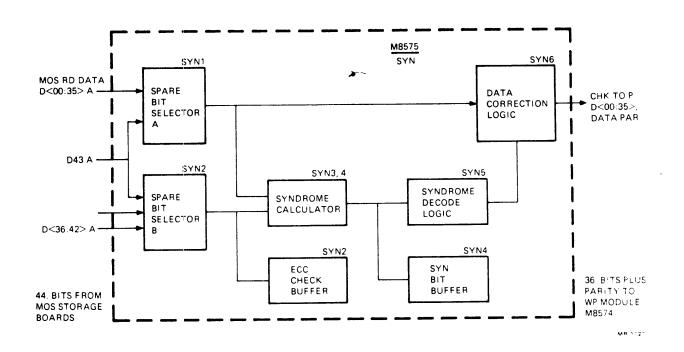

|                  | M8575 Syndrome5-19              |

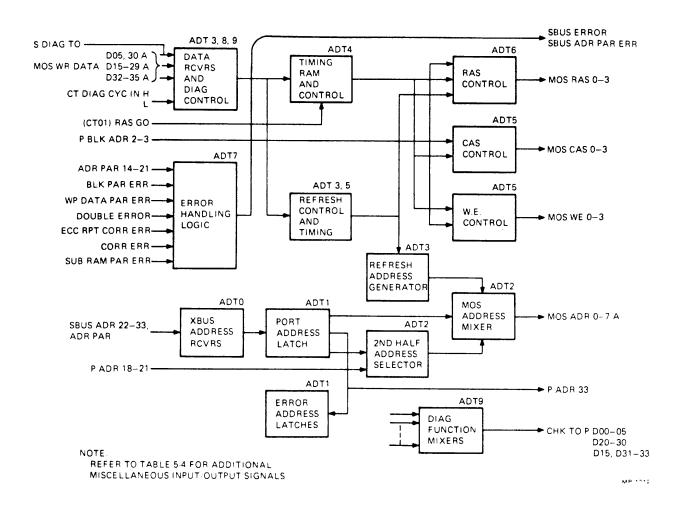

| 5.4.3            | M8577 Address and Timing5-23    |

| 5.4.4            | M8576 Control and Timing5-28    |

| 5.4.5            | m85/6 Control and Timing        |

| 5.4.6            | Summary5-28 THE XBUS5-34        |

| 5.5              | Physical Description            |

| 5.5.1            | physical Description            |

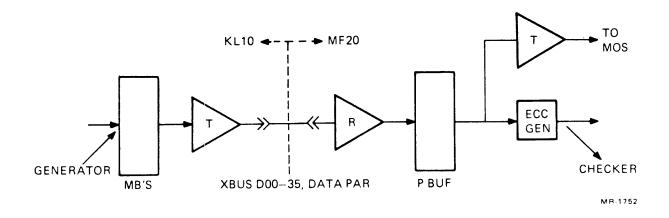

| 5.5.2            | Functional Description5-34      |

| 5.5.2.1          | Read Dialogue5-41               |

| 5.5.2.2          | Write Dialogue5-41              |

| 5.5.2.3          | Read-Pause-Write Dialogue5-42   |

| 5.5.2.4          | Diagnostic Cycle Dialogue5-43   |

| 5.5.3            | Summary5-44                     |

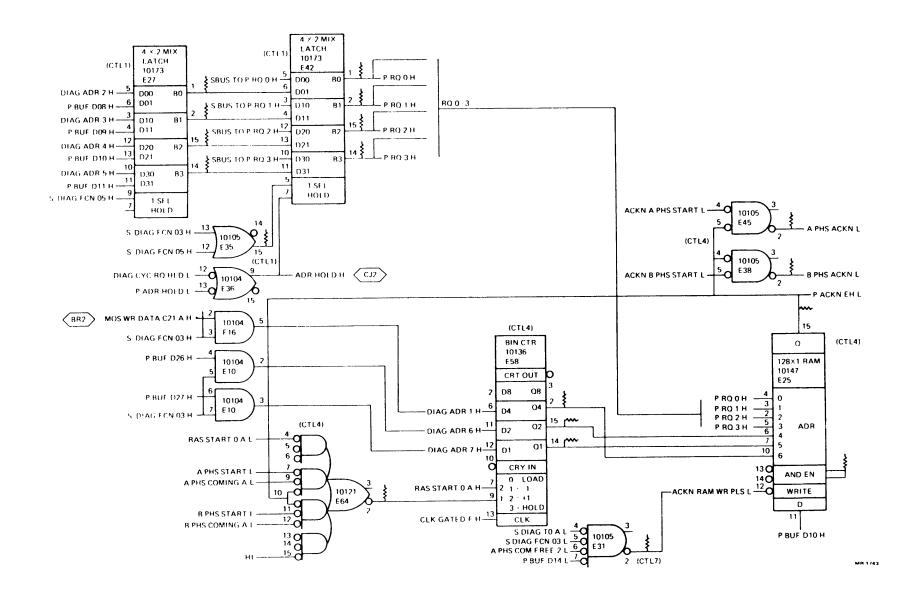

| 5.6              | DIAGNOSTIC FUNCTIONS5-44        |

| 5.6.1            | Programming5-44                 |

| 5.6.2            | Block Diagram5-45               |

| 5.6.3            | Summary5-47                     |

| 5.7              | BASIC MF20 OPERATIONS5-48       |

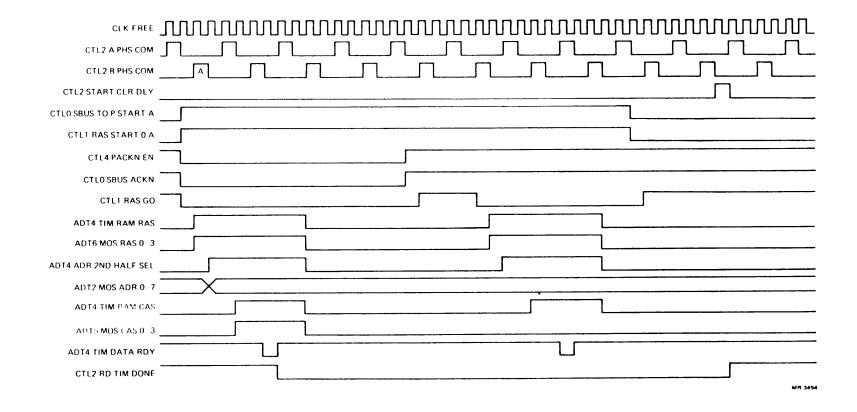

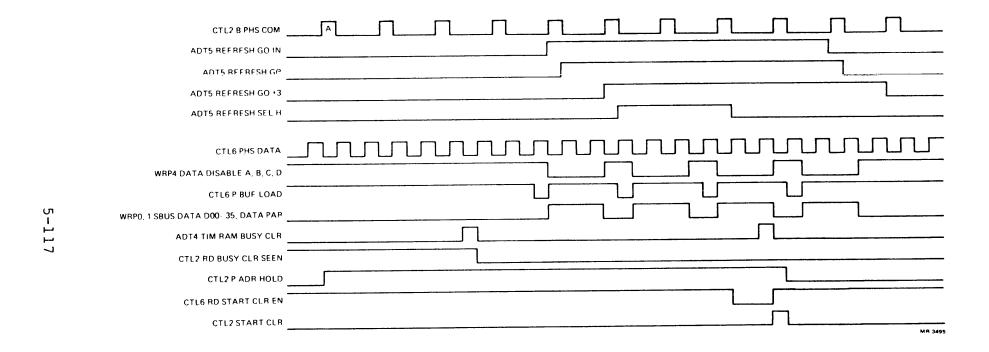

| 5.7.1            | Read Cycle5-48                  |

| 5.7.2            | Write Cycle5-55                 |

| 5.7.3            | Read-Pause-Write Cycle5-60      |

| 5.7.4            | Diagnostic Function Cycle5-60   |

| 5.7.5            | Summary                         |

| 5.8              | MF20 LOGIC DESCRIPTIONS5-65     |

| 5.8.1            | Error Check Code - ECC5-65      |

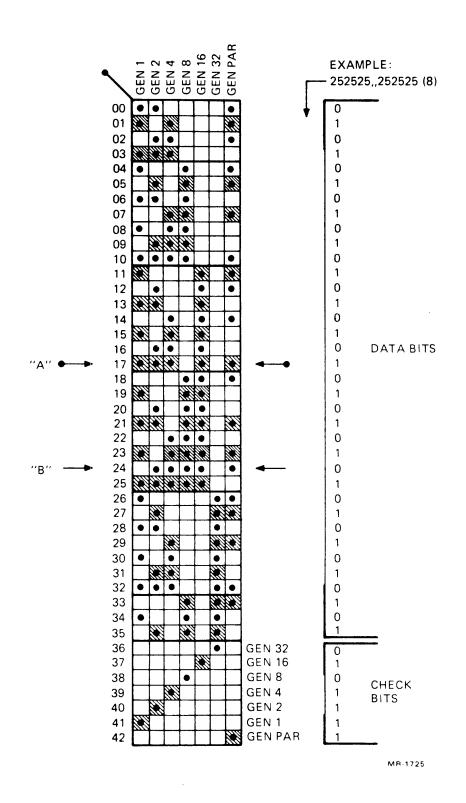

| 5.8.1.1          | ECC Algorithm5-66               |

| 5.8.1.2          | ECC Generation5-68              |

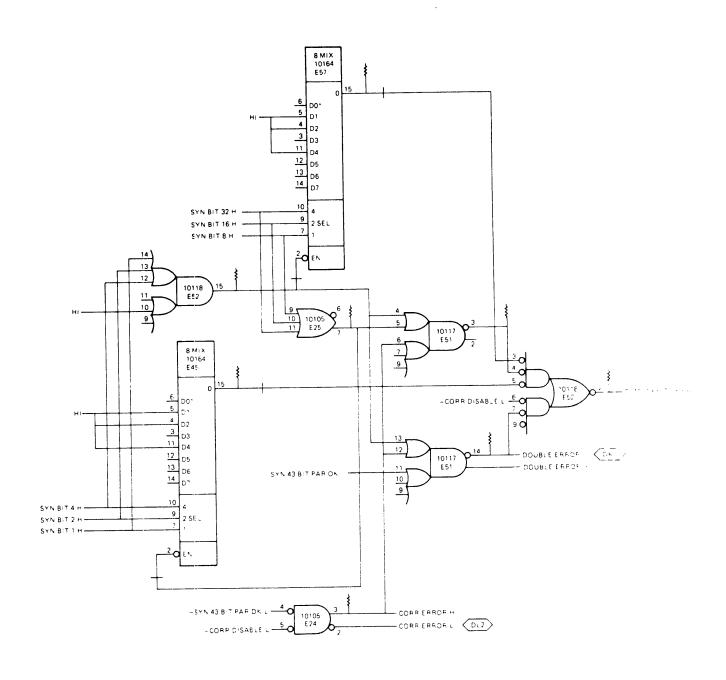

| 5.8.1.3          | ECC Checking and Correction5-70 |

| 5.8.1.4          | Summary5-77                     |

| 5.8.2            | Spare Bit Substitution5-77      |

| 5.8.2.1          | Spare Bit Substitution RAM5-77  |

|                  | Diagnostic Mode Operation5-79   |

| 5.8.2.2          | Normal Read/Write Operation5-82 |

| 5.8.2.3          | Summary5-83                     |

| 5.8.2.4<br>5.8.3 | Storage Module Operation5-83    |

| 5.8.3.1          | Simplified Block Diagram5-84    |

| 5.8.3.2          | One-Bit Slice5-84               |

|                  | Write Operation5-86             |

| 5.8.3.3          | Read Operation5-87              |

| 5.8.3.4          | Summary5-88                     |

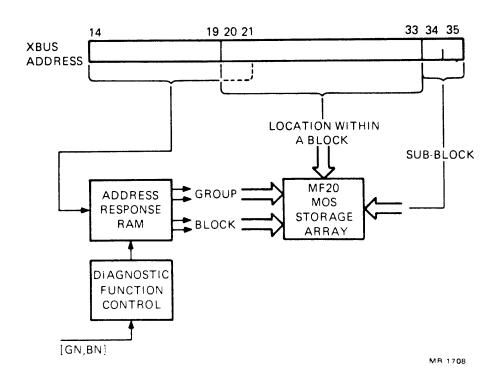

| 5.8.3.5          | Address Response RAM5-89        |

| 5.8.4            | Functional Block Diagram5-89    |

| 5.8.4.1          | Summary5-93                     |

| 5.8.4.2          | Timing RAM5-93                  |

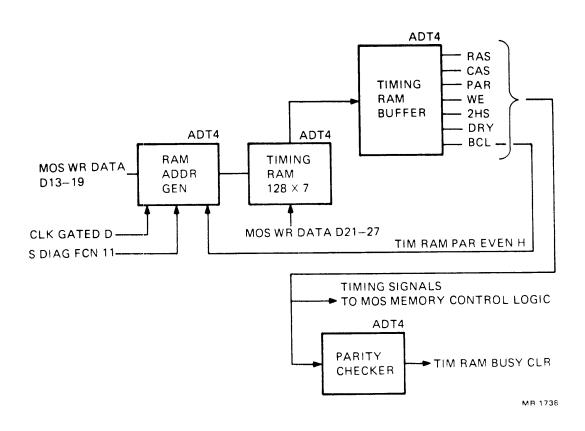

| 5.8.5            | Functional Block Diagram5-93    |

| 5.8.5.1          | Summary5-96                     |

| 5 8 5.2          | Summary                         |

|         | Page                                |

|---------|-------------------------------------|

| 5.8.6   | Fixed Value RAMs5-98                |

| 5.8.6.1 | Functional Block Diagram5-98        |

| 5.8.6.2 | Summary5-108                        |

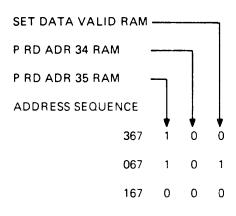

| 5.8.7   | Personality PROM5-109               |

| 5.8.7.1 | Overview5-109                       |

| 5.8.7.2 | Functional Block Diagram5-109       |

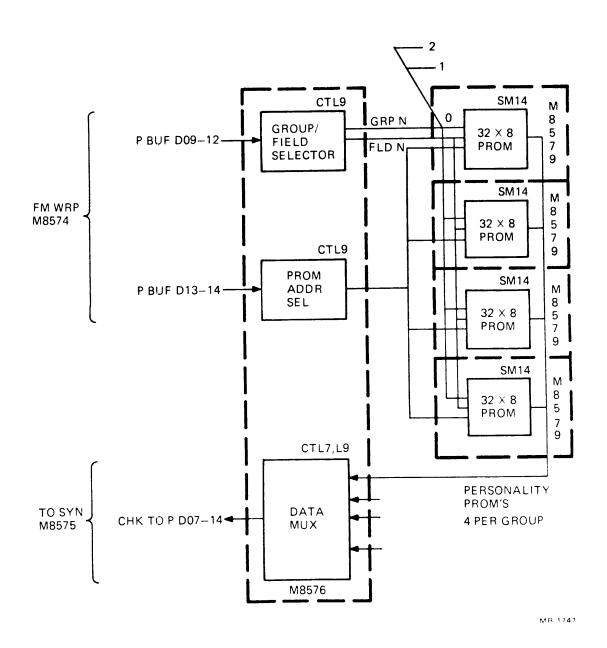

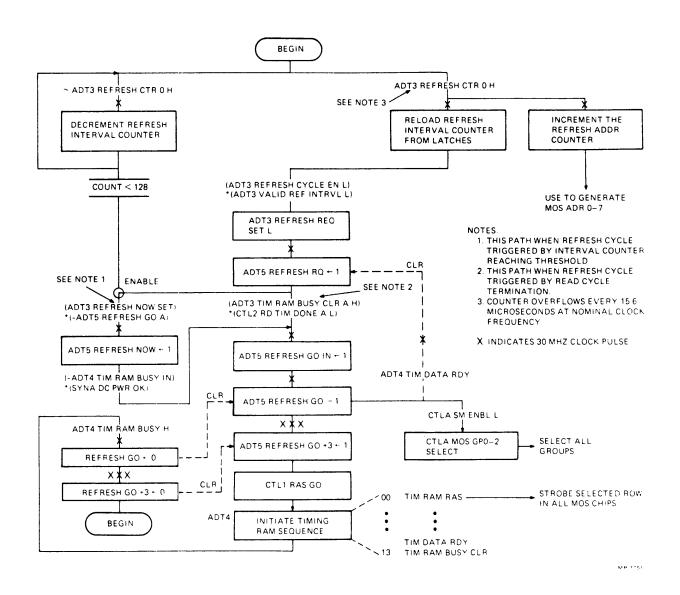

| 5.8.8   | Refresh Control Logic5-112          |

| 5.8.8.1 | Refresh Functional Block5-112       |

| 5.8.8.2 | Refresh Operation5-112              |

| 5.8.8.3 | Summary                             |

| 5.8.9   | Error-Handling Logic5-118           |

| 5.8.9.1 | Error Classification5-118           |

| 5.8.9.2 | Error Information Retrieval5-122    |

| 5.8.9.3 | Error Logic Analysis5-123           |

| 5.8.9.4 | Error Recovery and Analysis5-123    |

| 5.9     | KW20 MASTER OSCILLATOR              |

| 5.9.1   | Physical Description5-126           |

| 5.9.2   | KW20 Functional Block Diagram5-126  |

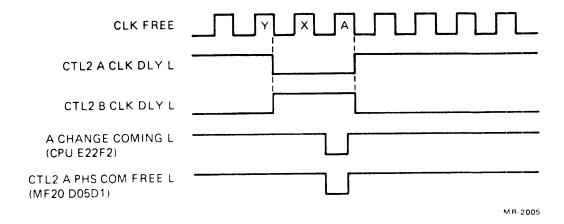

| 5.9.3   | MF20 Clock Signal Distribution5-129 |

| 5.9.4   | Synchronization                     |

| 5.10    | H7131 POWER SUPPLY                  |

| 5.10.1  | Input/Output Specifications5-133    |

| 5.10.2  | Power Distribution5-135             |

| 5.10.3  | Battery Pack                        |

| 5.10.4  | Summary5-138                        |

| 3.10.4  | Summary                             |

| CHAPTER | 6 PREVENTIVE MAINTENANCE            |

| 6.1     | INTRODUCTION6-1                     |

| 6.2     | TEST EQUIPMENT REQUIRED6-1          |

| 6.3     | PM PROCEDURES6-1                    |

| 6.3.1   | Run SYSERR                          |

| 6.3.2   | Run TGHA6-2                         |

| 6.3.3   | Clean Air Filters6-3                |

| 6.3.4   | Check Fans6-3                       |

| 6.3.5   | Check Power Supply Voltages6-3      |

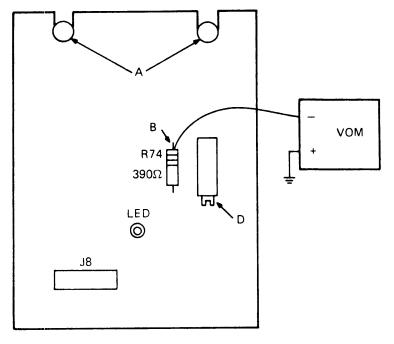

| 6.3.6   | KW20 Clock Checks6-4                |

| 6.3.7   | Run Diagnostics6-4                  |

| 6.3.8   | Run Voltage and Clock Margins6-6    |

| 6.3.9   | Check Overtemperature Sensors6-8    |

| 6.3.10  | Check Door Interlocks6-8            |

| 6.3.11  | Check Battery Backup6-9             |

| 6.3.12  | Check System Cabling Integrity6-9   |

|         |                                     |

| CHAPTER | 7 CORRECTIVE MAINTENANCE            |

| 7.1     | INTRODUCTION7-1                     |

| 7.2     | DIAGNOSTICS7-1                      |

| 7.2.1   | DGQFB (MEMCON)                      |

| 7.2.1.1 | Purpose                             |

|           | Page                                         |

|-----------|----------------------------------------------|

| 7.2.1.2   | General Program Operation7-3                 |

| 7.2.1.3   | Operating Procedures7-3                      |

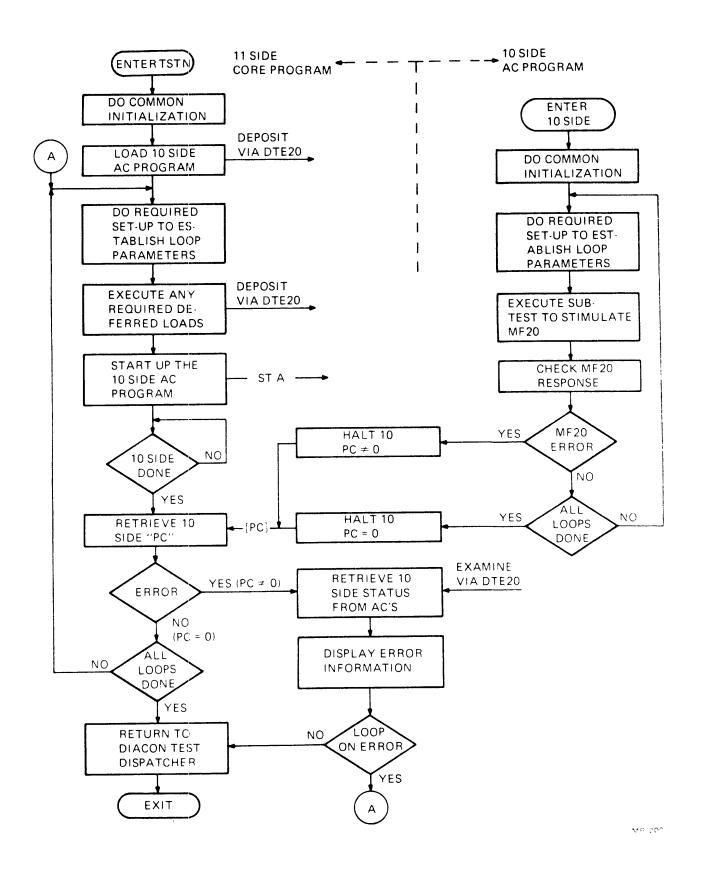

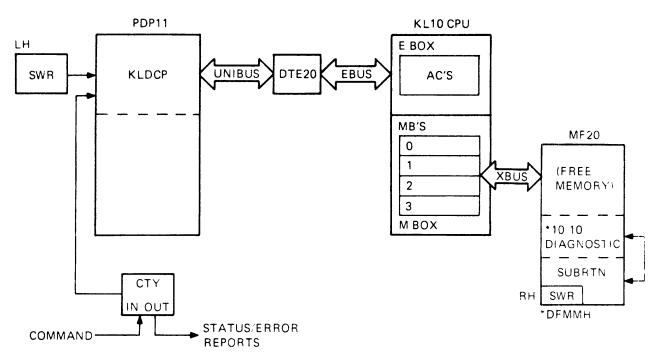

| 7.2.2     | 11-Based Diagnostics7-10                     |

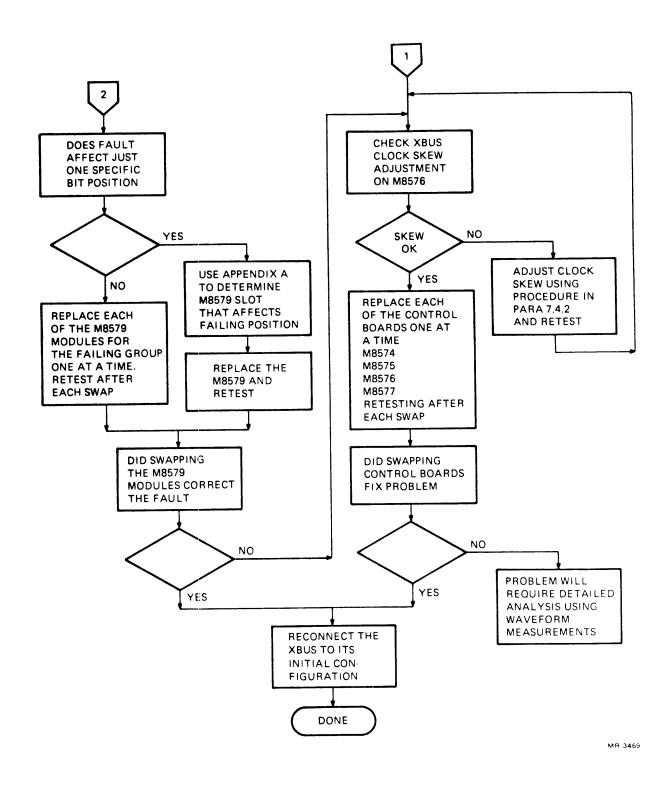

| 7.2.2.1   | Diagnostic Test Flow7-10                     |

| 7.2.2.2   | DHKBF (MF20 Diagnostic Part 1)7-13           |

| 7.2.2.3   | DHKBG (MF20 Diagnostic Part 2)7-22           |

|           | 10-Based Diagnostics                         |

| 7.2.3     | DFMMH (Figure 7-3)7-32                       |

| 7.2.3.2   | Drmm (rigure /-3)                            |

| 7.2.3.3   | SYSERR                                       |

| 7.2.3.4   | TGHA7-45                                     |

| 7.3       | TROUBLESHOOTING PROCEDURES                   |

| 7.3.1     | Introduction7-49                             |

| 7.3.2     | Memory Fault Symptoms7-49                    |

| 7.3.3     | General Troubleshooting Approach7-52         |

| 7.3.4     | Using the Diagnostics7-58                    |

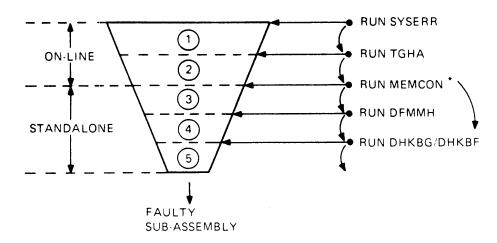

| 7.3.4.1   | Tops-Down Approach7-58                       |

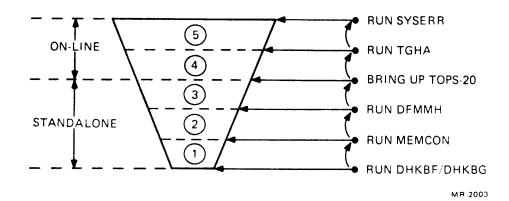

| 7.3.4.2   | Bottoms-Up Approach7-61                      |

| 7.4       | SUBASSEMBLY REMOVAL AND REPLACEMENT7-61      |

| 7.4.1     | Power Supply7-61                             |

| 7.4.1.1   | Removal Procedure                            |

|           | Replacement Procedure7-62                    |

| 7.4.1.2   | Battery Pack7-63                             |

| 7.4.2     | Battery Pack                                 |

| 7.4.2.1   | Removal Procedure                            |

| 7.4.2.2   | Replacement Procedure                        |

| 7.4.3     | KW20 Master Oscillator7-64                   |

| 7.4.3.1   | KW20 Fan Removal Procedure                   |

| 7.4.3.2   | KW20 Fan Replacement Procedure7-64           |

| 7.4.3.3   | KW20 Logic Module Removal Procedure7-65      |

| 7.4.3.4   | Logic Module Replacement Procedure7-65       |

| 7.4.4     | MF20 Logic Assembly7-66                      |

| 7.4.4.1   | Logic Module Removal Procedure7-66           |

| 7.4.4.2   | Logic Module Replacement Procedure7-60       |

|           | Fan Removal Procedure7-66                    |

| 7.4.4.3   | Fan Replacement Procedure7-67                |

| 7.4.4.4   | Air Filter Removal/Replacement Procedure7-67 |

| 7.4.4.5   | All Filter Removal/Replacement Procedure7-5: |

| 7.5       | MF20 ADJUSTMENTS7-68                         |

| 7.5.1     | KW20 Regulator Adjustment7-68                |

| 7.5.2     | M8576 Clock Deskew7-69                       |

| 7.5.2.1   | Clock Check Procedure7-68                    |

| 7.5.2.2   | Clock Deskew Procedure7-71                   |

|           | MDOOD GEED DDDDDDDDDDDDDDDDDDDDDDDDDDDDDD    |

| CHAPTER 8 | MF20F SITE PREPARATION AND INSTALLATION      |

| 8.1       | INTRODUCTION8-1                              |

| 8.2       | PHYSICAL LAYOUT8-1                           |

| 8.3       | MF20F CONFIGURATIONS8-1                      |

| 8.4       | SITE PREPARATION8-1                          |

|           | REFERENCE DOCUMENTS8-6                       |

| 8.5       | DIAGNOSTICS8-6                               |

| 8.6       | STANDARD TOOLS AND EQUIPMENT8-6              |

| 8.7       | STANDARD TOOLS AND EQUIPMENI                 |

|                      | Page                                                          |

|----------------------|---------------------------------------------------------------|

| 8.8                  | UNPACKING AND INSPECTION8-6                                   |

| 8.8.1                | Unpacking8-6                                                  |

| 8.8.2                | Inspection                                                    |

| 8.9                  | INSTALLATION TO KLIOR8-7                                      |

| 8.10                 | VANE SWITCHES8-10                                             |

| 8.11                 | TEST AND ACCEPTANCE8-10                                       |

| CHAPTER 9            | MG20 SPECIFIC INFORMATION                                     |

| 9.1                  | INTRODUCTION9-1                                               |

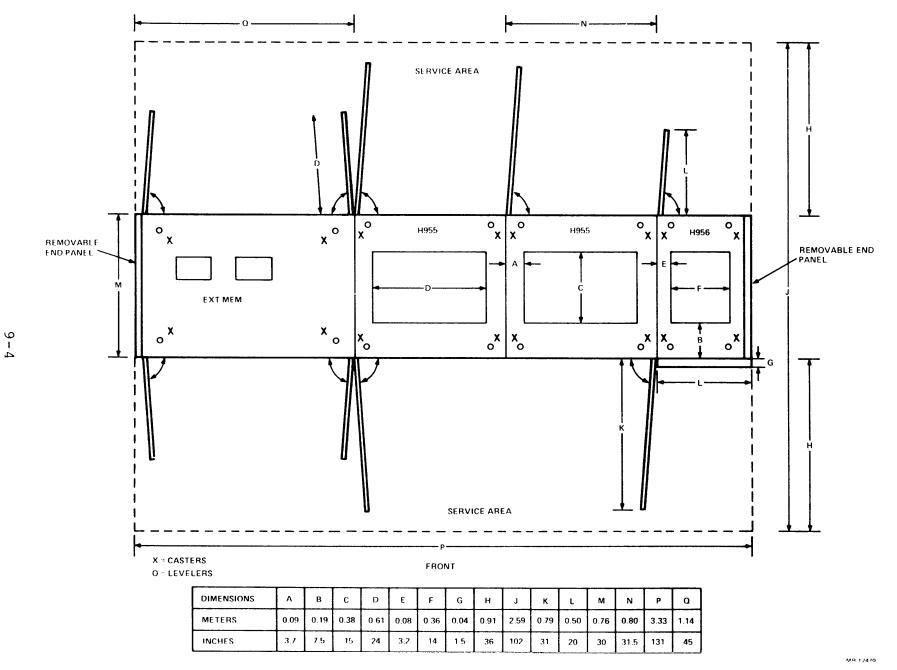

| 9.2                  | CONFIGURATIONS9-1                                             |

| 9.3                  | REFERENCE DOCUMENTS9-3                                        |

| 9.4                  | SITE PREPARATION OF THE MG20-DA/DB FOR                        |

|                      | THE KL10-D SYSTEM9-3                                          |

| 9.5                  | UNPACKING THE MG20-DA/DB9-3                                   |

| 9.6                  | INSPECTING THE MG20-DA/DB9-5                                  |

| 9.7                  | MG20 MODULE UTILIZATIONS9-5                                   |

| 9.8                  | SOFTWARE AND DIAGNOSTIC REQUIREMENTS9-6                       |

| 9.9                  | UPGRADING THE MF20 AND MG20 MEMORIES9-6                       |

| 9.9.1                | Configuration Restrictions9-6                                 |

| 9.9.2                | Power Supply9-6                                               |

| 9.9.3                | MF20 Upgrade Procedure9-8                                     |

| 9.9.4                | MG20 Upgrade Installation9-8                                  |

| 9.10                 | VERIFICATION AND CHECKOUT PROCEDURE9-8                        |

| 9.10.1               | DC Voltage Power Check9-8                                     |

| 9.10.2               | Diagnostic Verification9-9                                    |

| 9.10.2.1             | DHKBF - MF20/MG20 Controller Test I9-9                        |

| 9.10.2.2             | DHKBG - MF20/MG20 Controller Test II9-9                       |

| 9.10.2.3             | DFMMH - MF20/MG20 4096K Memory Reliability9-9                 |

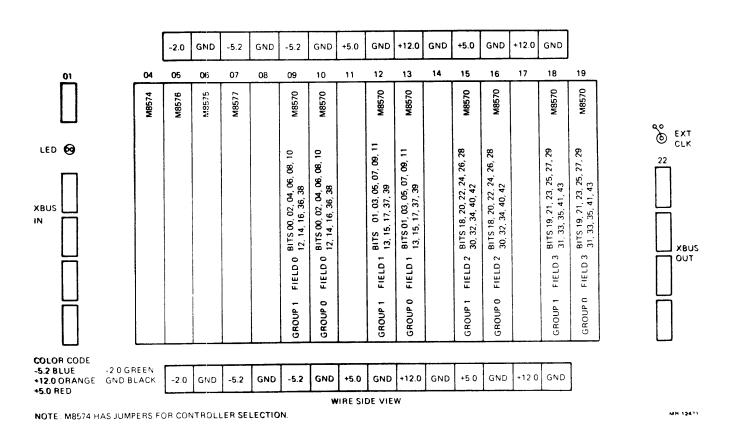

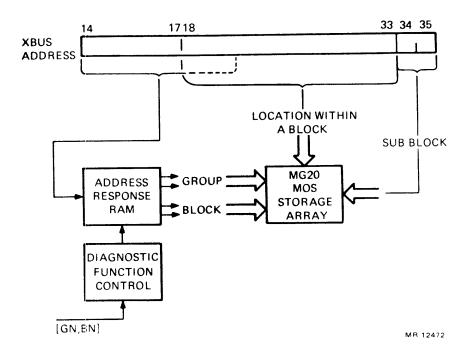

| 9.11                 | STORAGE ARRAY ORGANIZATION9-9                                 |

| 9.11.1               | Storage Units9-9                                              |

| 9.11.2               | Memory Module Access9-10                                      |

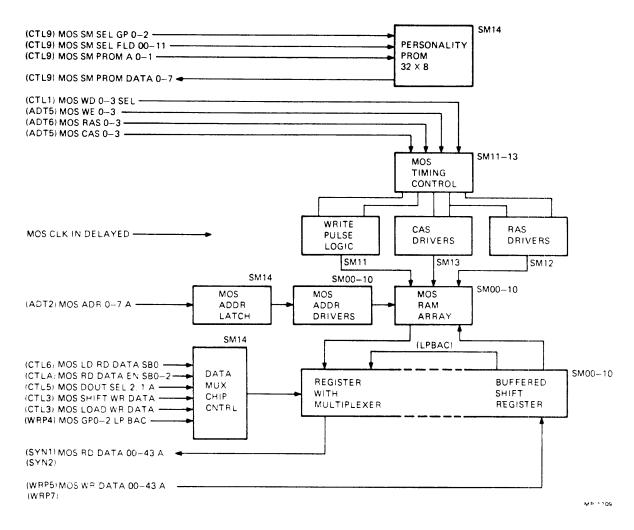

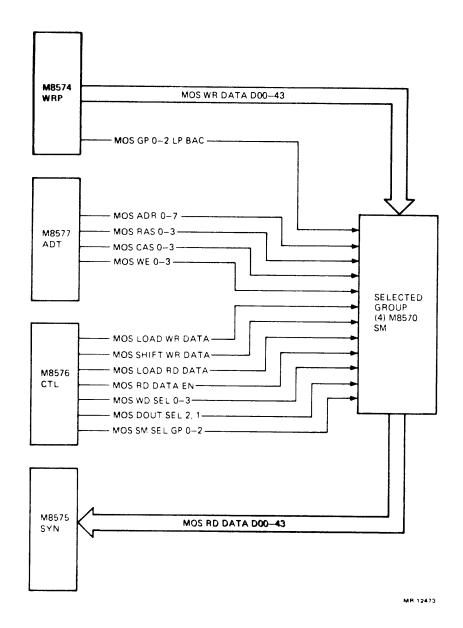

| 9.12                 | FUNCTIONAL BLOCK DIAGRAMS9-10                                 |

| 9.12.1               | M8570 Memory Module9-10                                       |

| 9.13                 | MEMORY MODULE OPERATION9-13                                   |

| 9.13.1<br>9.13.2     | Simplified Block Diagram9-13 One-Bit Slice9-15                |

| 9.13.2               |                                                               |

| 9.13.3               | Write Operation9-16 Read Operation9-17                        |

| 9.13.4               | •                                                             |

| 9.14.1               | PERSONALITY PROM9-17 Functional Block Diagram9-19             |

| 9.14.1               |                                                               |

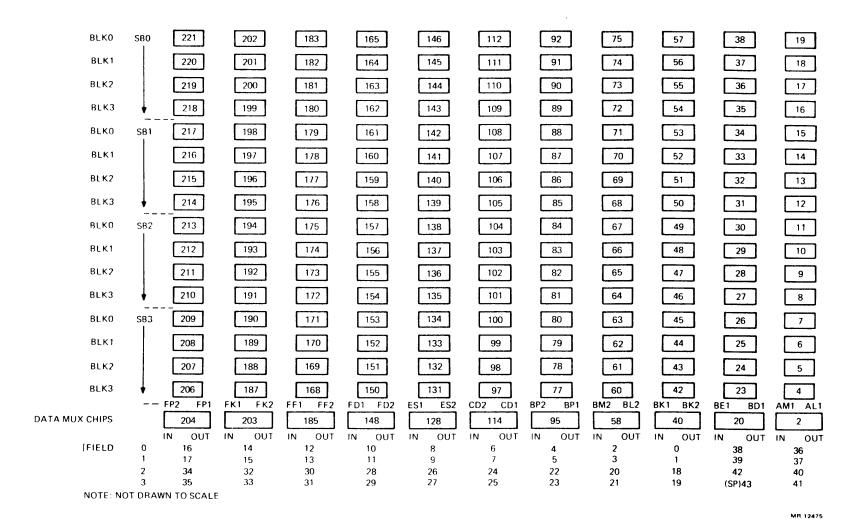

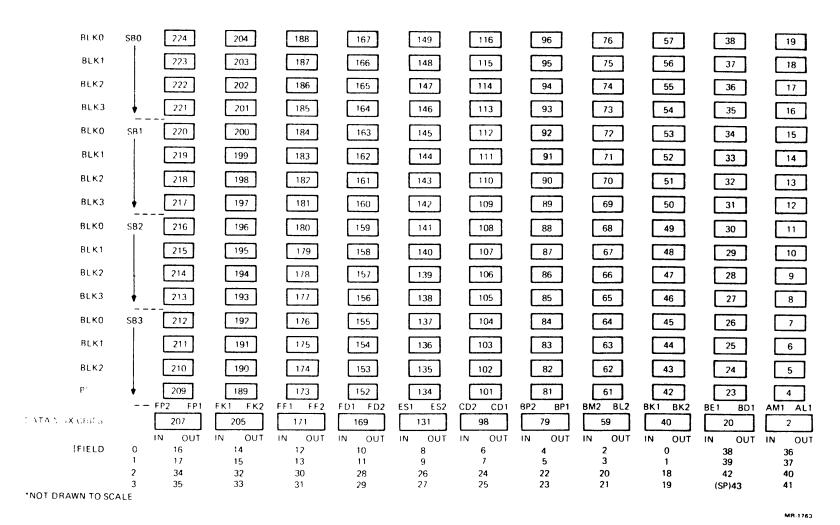

| •                    | M8570 MEMORY MODULE GEOGRAPHY9-19 COMPLEX IC DESCRIPTIONS9-21 |

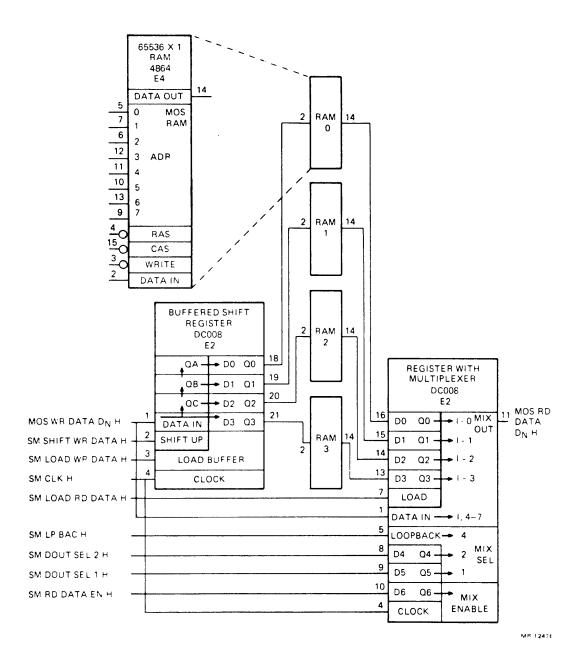

| 9.16                 |                                                               |

| 9.16.1               | DC008 Data Multiplexer Chip9-21 Read Operation9-21            |

| 9.16.1.1             |                                                               |

| 9.16.1.2<br>9.16.1.3 | Write Operation9-23 Loopback Operation9-23                    |

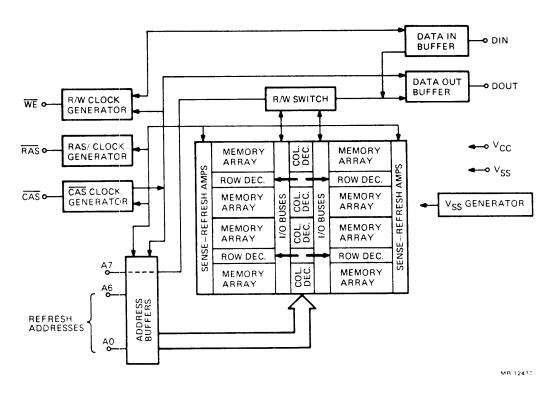

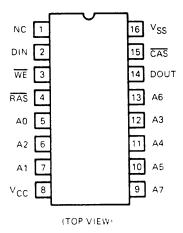

| 9.15.1.3             | 4864 MOS RAM CHIP9-24                                         |

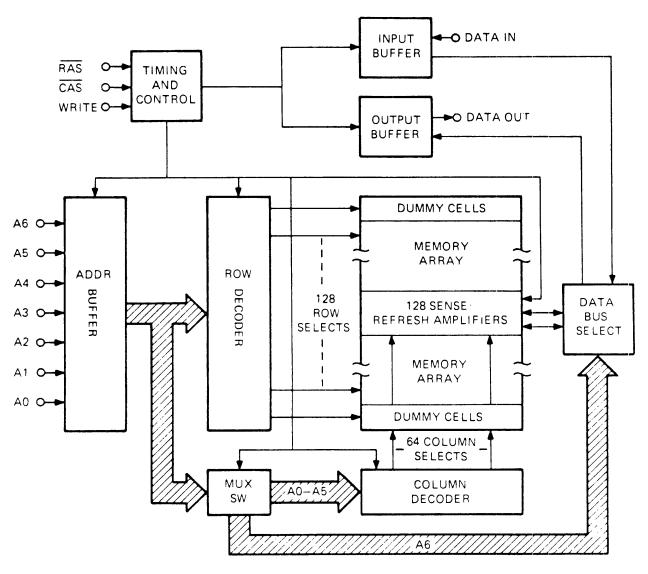

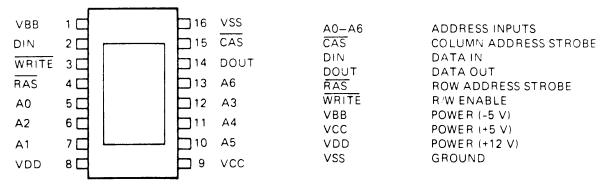

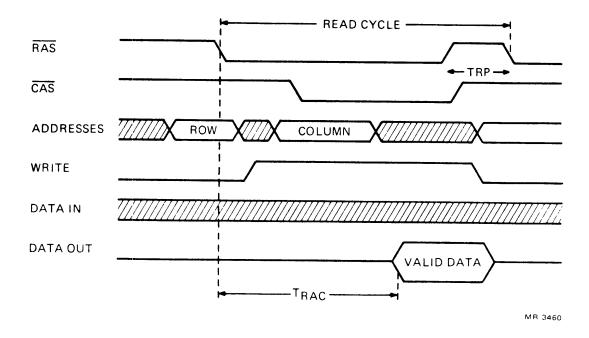

| 9.16.2.1             | General Description9-24                                       |

| 9.16.2.1             | Basic Operation9-24                                           |

|                      | Dabto operactors ************************************         |

|                                                                                                                                                                                                                                                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 10                                                                                                                                                                                                                                                                   | TGHA (THE GREAT HEURISTIC ALGORITHM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.3<br>10.3.1<br>10.3.2<br>10.3.3<br>10.3.4<br>10.3.5<br>10.3.6<br>10.4<br>10.4.1<br>10.4.2<br>10.4.3<br>10.4.4<br>10.5.1<br>10.5.2<br>10.5.2<br>10.5.3<br>10.5.4<br>10.5.5<br>10.5.6<br>10.5.7<br>10.6.1<br>10.6.2<br>10.6.3<br>10.6.4 | INTRODUCTION. 10-1  UPDATE INSTRUCTIONS. 10-1  Update of TOPS-10. 10-1  Update of TOPS-20. 10-2  MAKING LIST FILES WITH TGHA. 10-2  TGHA File Requirements. 10-3  Initial System Start-Up. 10-3  MG20 Errors. 10-3  Known Error Determination 10-4  Corrective Action. 10-4  Parity Errors. 10-5  HISTORY FILE. 10-5  Directory Page. 10-5  Group Page. 10-6  Storage Module Page. 10-6  Storage Module Page. 10-7  Unused Storage Modules. 10-8  TRACE FILE. 10-8  Spare Bit Swap. 10-9  Parity Error. 10-9  Serious MG20 Hardware Failures 10-9  Use of Spare Bit by KLI 10-10  Missing Database. 10-10  Missing Database. 10-10  Recovery Procedure 10-11  Software State Word. 10-11  Software State Word. 10-11  Serious MG20 Hardware Failures 10-11  Serious MG20 Hardware Failures 10-11  Software State Word. 10-11  Serious MG20 Hardware Failures 10-11  Serious MG20 Hardware Failures 10-11  Software State Word. 10-11  Serious MG20 Hardware Failures 10-11  Serious MG20 Hardware Failures 10-11  Serious MG20 Hardware Failures 10-12  Use of Spare Bit by KLI 10-12  KLI Detected Bad Block 10-12  KLI Detected Bad Block 10-12  KLI Detected Bad Block 10-12 |

| APPENDIX A                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| APPENDIX B                                                                                                                                                                                                                                                                   | COMPLEX IC DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| APPENDIX C                                                                                                                                                                                                                                                                   | 11-BASED 10 DIAGNOSTIC TEST STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## FIGURES

| Figure | No. | Title                                          | Page                |

|--------|-----|------------------------------------------------|---------------------|

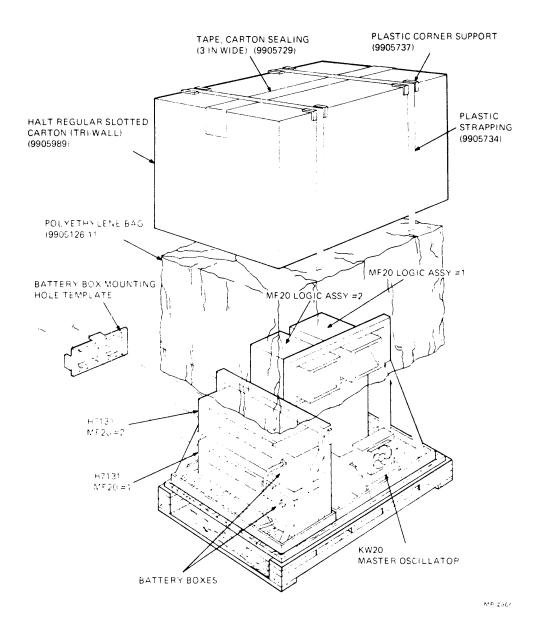

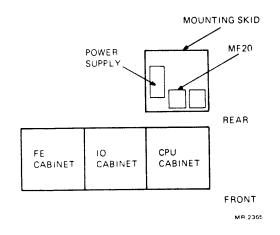

| 1-1    |     | MF20 Physical Layout                           | 1-2                 |

| 1-2    |     | MF20 Simplified Module Utilization Diagram     | 1-3                 |

| 1-3    |     | MF20 Configurations                            | 1-6                 |

| 2-1    |     | KL10-C/E CPU Unit Floor Space Requirements     | 2-2                 |

| 2-2    |     | KL10-C/E CPU-MF20 LH/LJ Unit Floor Space       |                     |

|        |     | Requirements                                   | 2-6                 |

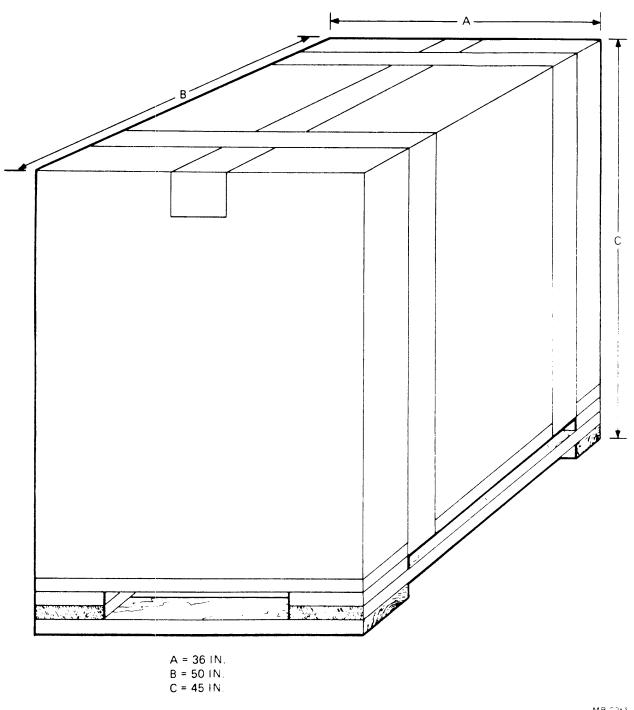

| 2-3    |     | MF20 LA/LB, LC/LD, LK/LL Packaging             | • • • • 2- /        |

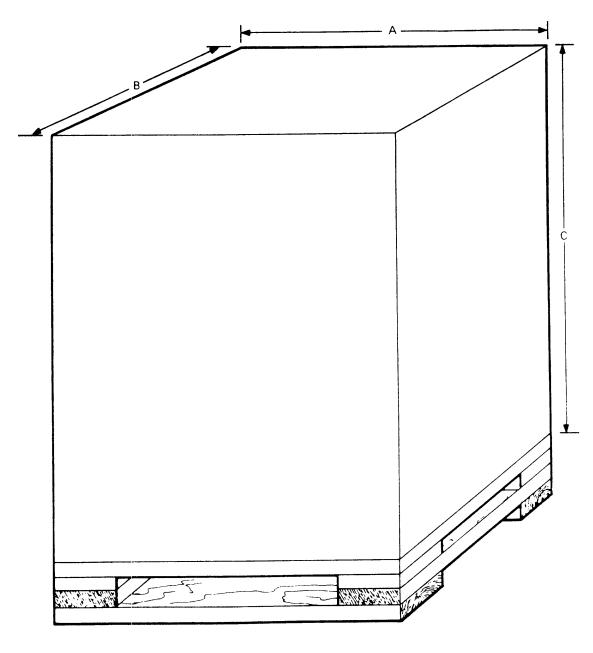

| 2-4    |     | MF20 LH/LJ Packaging                           | 2-9                 |

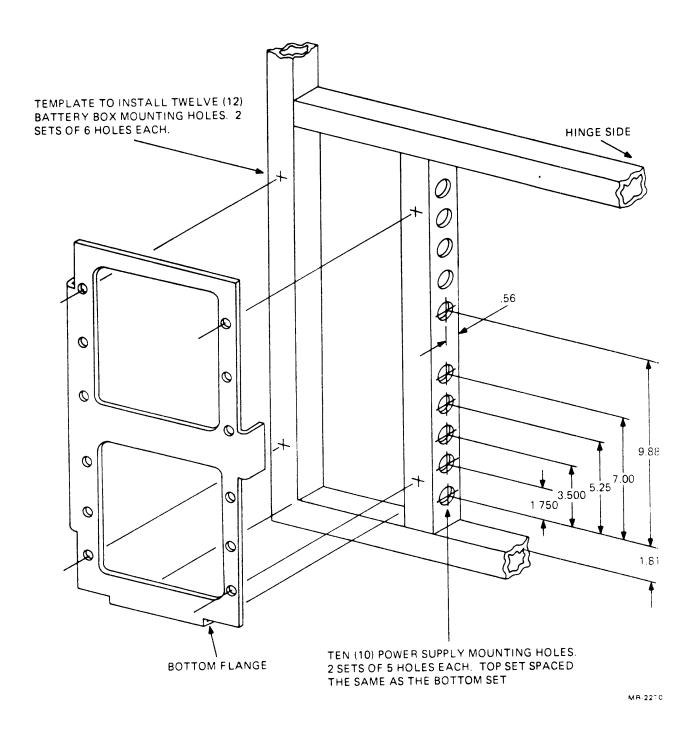

| 2-5    |     | CPU Cabinet Rear Equipment Mounting Door       | 2-10                |

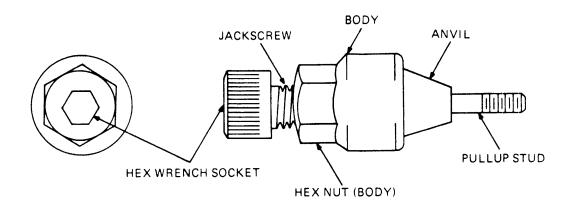

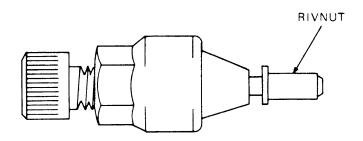

| 2-6    |     | Rivnut Tool                                    | 2-12                |

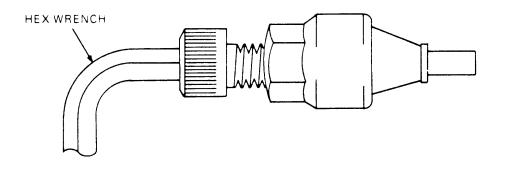

| 3-1    |     | MF20 Shipping Skid                             | 3-3                 |

| 3-2    |     | Skidded Checkout                               | 3-11                |

| 4-1    |     | Memory Configuration Overview Phase 1          | 4-4                 |

| 4-2    |     | Memory Configuration Overview Phase 2          | •••4 <del>-</del> 5 |

| 4-3    |     | Diagnostic Function Format                     | 4-7                 |

| 4 – 4  |     | Data Loopback                                  | 4-12                |

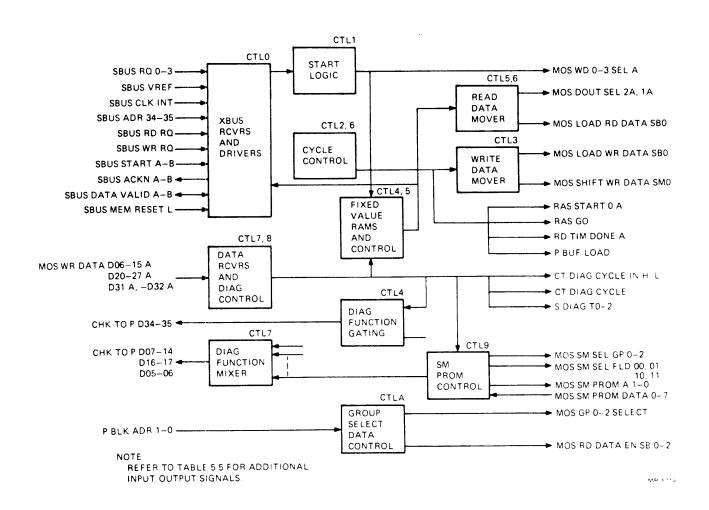

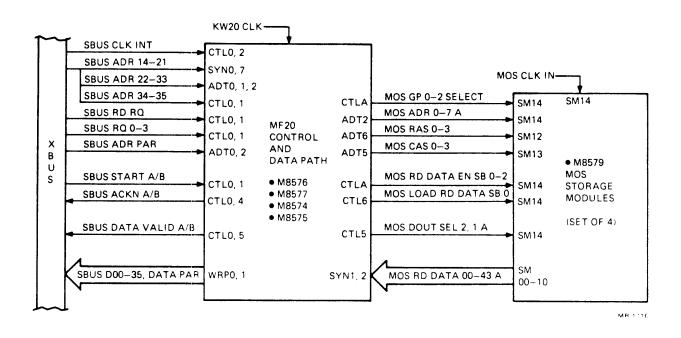

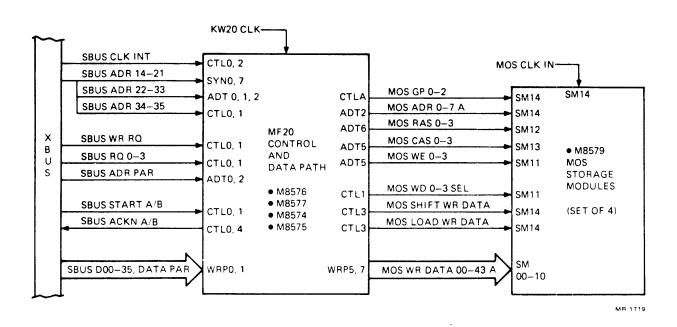

| 5-1    |     | MF20 Conceptual Block Diagram                  | 5-2                 |

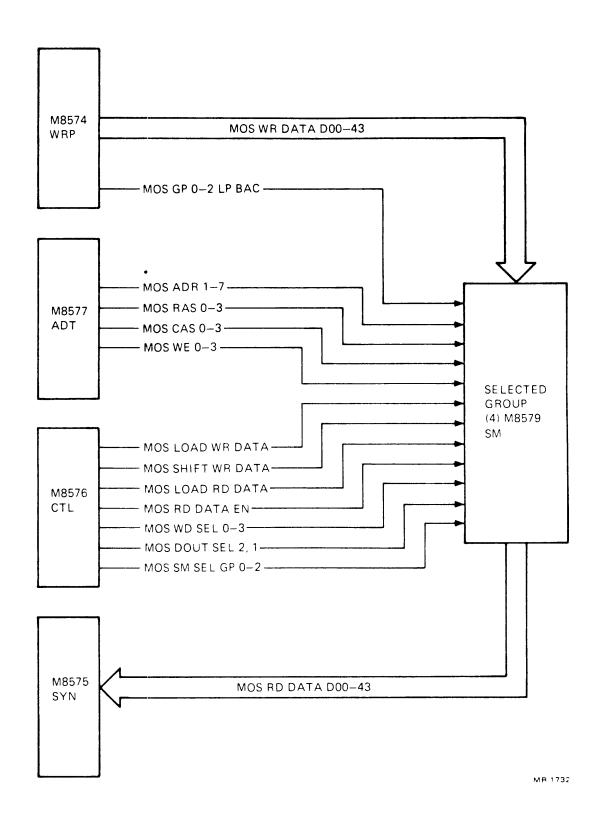

| 5-2    |     | Module Block Diagram                           | 5-5                 |

| 5-3    |     | Storage Array Access                           | 5-10                |

| 5-4    |     | M8579 Functional Block Diagram                 | 5-12                |

| 5-5    |     | M8574 Functional Block Diagram                 | 5-15                |

| 5-6    |     | M8575 Functional Block Diagram                 | 5-20                |

| 5-7    |     | M8577 Functional Block Diagram                 | 5-24                |

| 5-8    |     | M8576 Functional Block Diagram                 | 5-29                |

| 5-9    |     | XBus Overview (Data Bit 04)                    | 5-35                |

| 5-10   |     | MF20 Diagnostic Function Overview              | 5-46                |

| 5-11   |     | Read Cycle Overview                            | 5-49                |

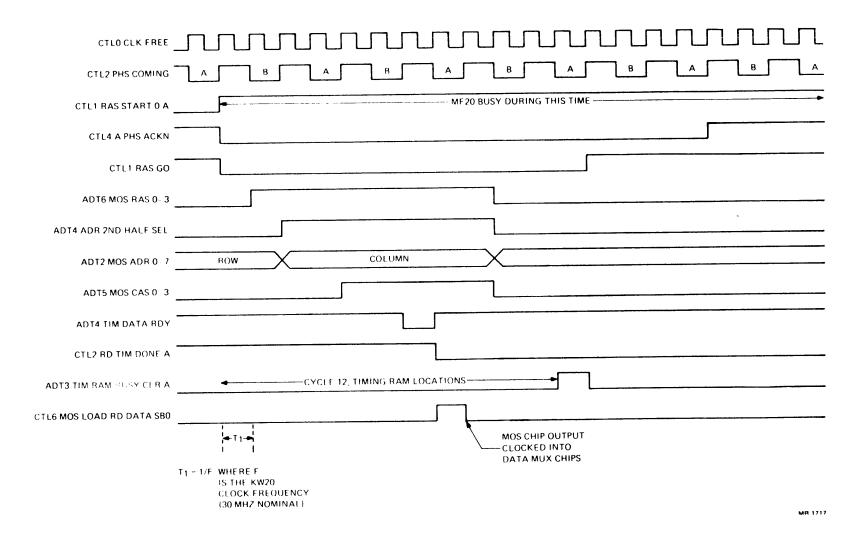

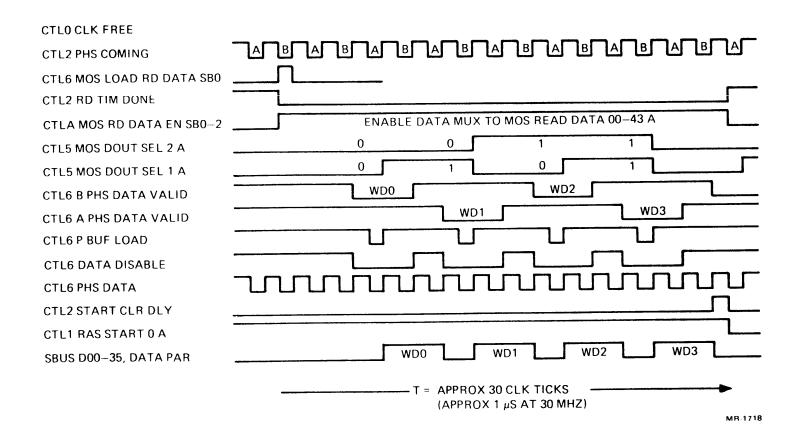

| 5-12   |     | Read Cycle Phase 1 Rough Timing Diagram        | 5-50                |

| 5-13   |     | Read Cycle Phase 2 Rough Timing Diagram        | 5-51                |

| 5-14   |     | Write Cycle Overview                           | 5-56                |

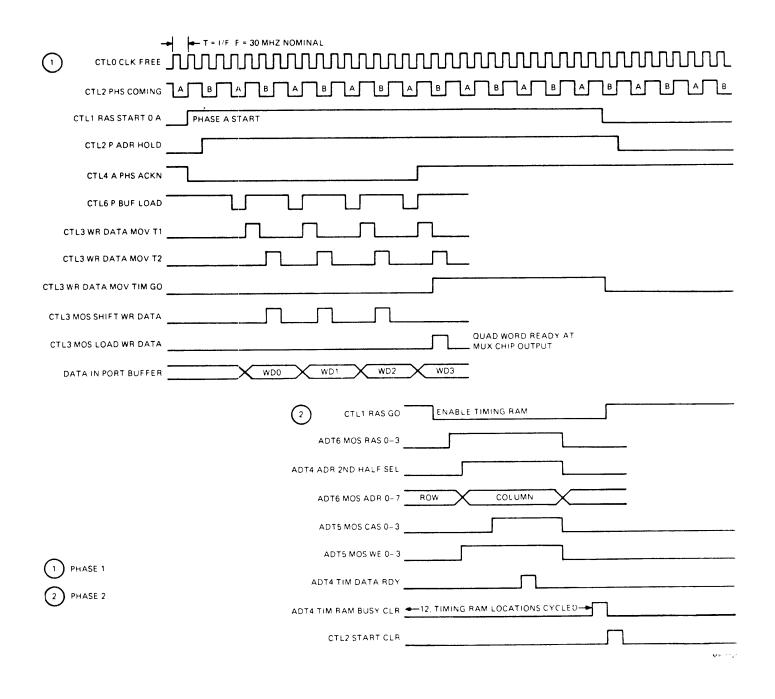

| 5-15   |     | Write Cycle Rough Timing Diagram               | 5-57                |

| 5-16   |     | Read-Pause-Write Cycle Overview                | 5-61                |

| 5-17   |     | Read-Pause-Write Cycle Rough Timing Diagram    | 5-62                |

| 5-18   |     | Diagnostic Function Cycle Overview             | 5-63                |

| 5-19   |     | Diagnostic Function Cycle Rough Timing Diagram | 5-64                |

| 5-20   |     | ECC Coding Format                              | 5-67                |

| 5-21   |     | ECC Generation - Simplified Logic              |                     |

|        |     | Block Diagram                                  | 5-69                |

| 5-22   |     | ECC Check and Correction                       | 5-71                |

| 5-23   |     | ECC Error Flags - Logic Diagram                | 5-73                |

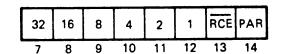

| 5-24   |     | Spare Bit RAM Format                           | 5-78                |

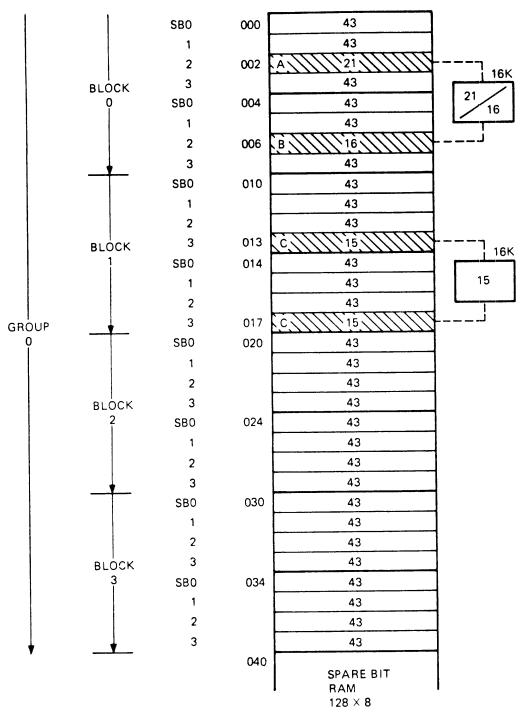

| 5-25   |     | Spare Bit RAM Mapping                          | 5-80                |

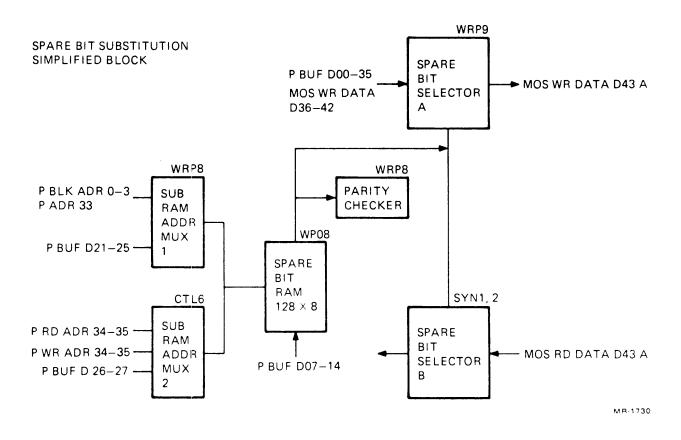

| 5-26   |     | Spare Bit Substitution - Simplified            |                     |

|        |     | Block Diagram                                  | 5-81                |

| 5-27   |     | MOS Storage Module - Simplified Block Diagram. | 5-85                |

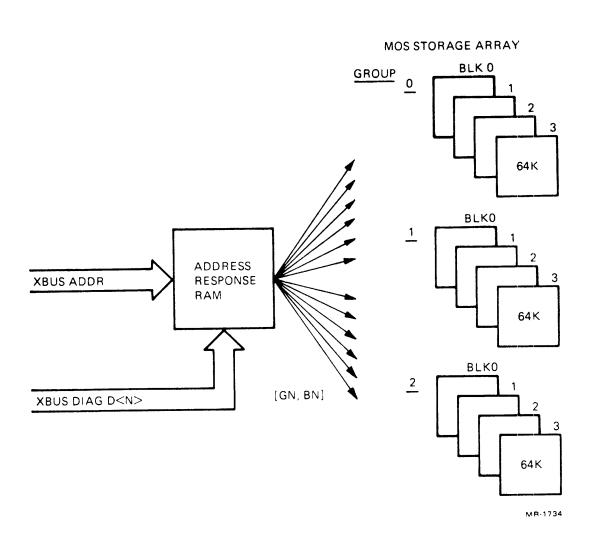

| 5-28   |     | Address Response RAM Overview                  | 5-90                |

| 5-29   |     | Address Response RAM - Bit Format              | 5-91                |

| 5-30   |     | Address Response RAM - Simplified              |                     |

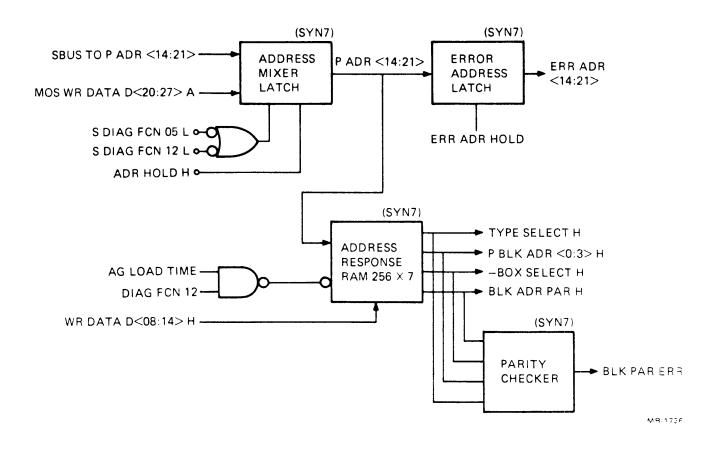

|        |     | Block Diagram                                  | 5-92                |

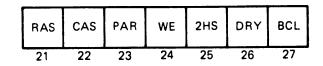

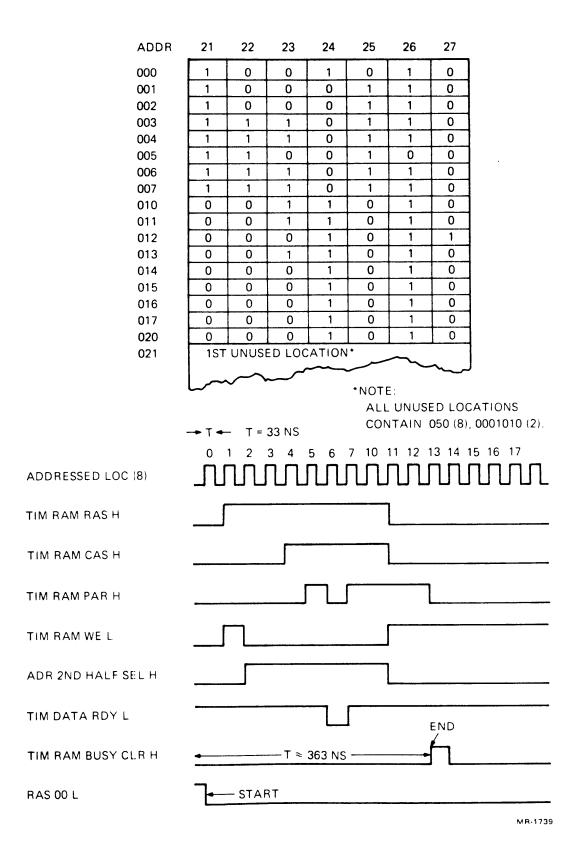

| 5-31   |     | Timing RAM - Bit Format                        | 5-94                |

## FIGURES (Cont)

| Figure        | No. | Title                                                                    | Page   |

|---------------|-----|--------------------------------------------------------------------------|--------|

| 5-32<br>5-33  |     | Timing RAM - Functional Block Diagram Timing RAM Map - Simplified Timing |        |

| 5-34          |     | Fixed Value RAM - ACKN Bit Map                                           |        |

| 5 <b>-</b> 35 |     | ACKN RAM - Address Translation                                           |        |

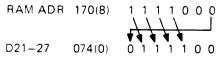

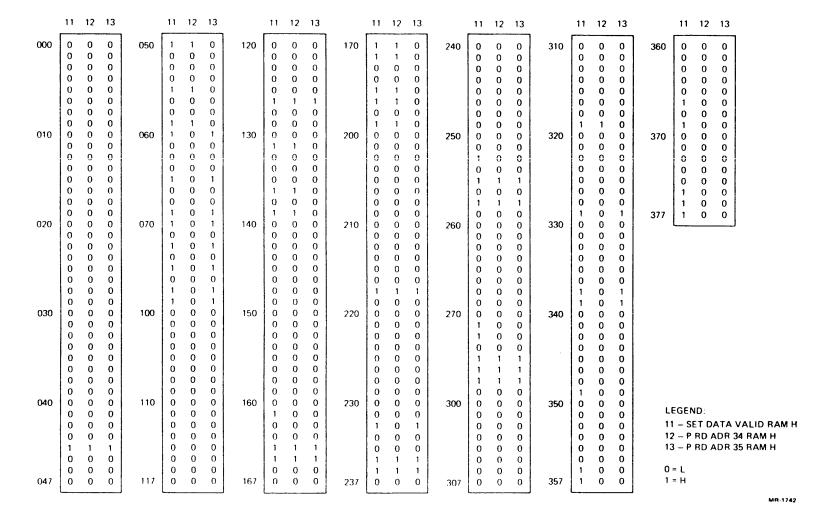

| 5-36          |     | Fixed Value RAM - Data Valid Bit Map                                     |        |

| 5-37          |     | ACKN RAM - Logic Block Diagram                                           |        |

| 5-38          |     | Data Valid RAM - Logic Block Diagram                                     | .5-105 |

| 5-39          |     | Fixed Value RAM - Examples                                               | .5-106 |

| 5-40          |     | Personality PROM - Bit Format                                            | .5-110 |

| 5-41          |     | Personality PROM - Functional Block Diagram                              | .5-111 |

| 5-42          |     | Refresh Control Logic Functional                                         |        |

| 5-42          |     | Block Diagram                                                            | .5-113 |

| 5-43          |     | Refresh Timing Flowchart                                                 | .5-115 |

| 5-44          |     | Read Followed By Refresh Timing                                          |        |

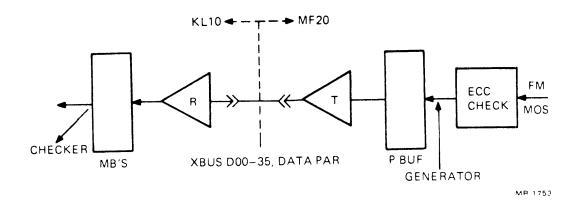

| 5-45          |     | Data Parity - Write Transmission Path                                    | .5-119 |

| 5-46          |     | Data Parity - Read Transmission Path                                     | .5-120 |

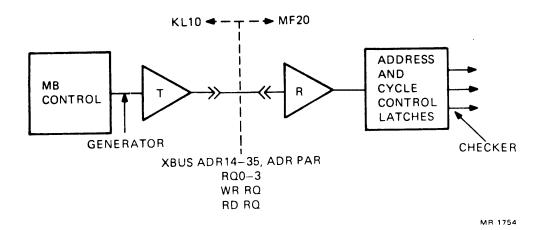

| 5-47          |     | Address Parity - Transmission Path                                       |        |

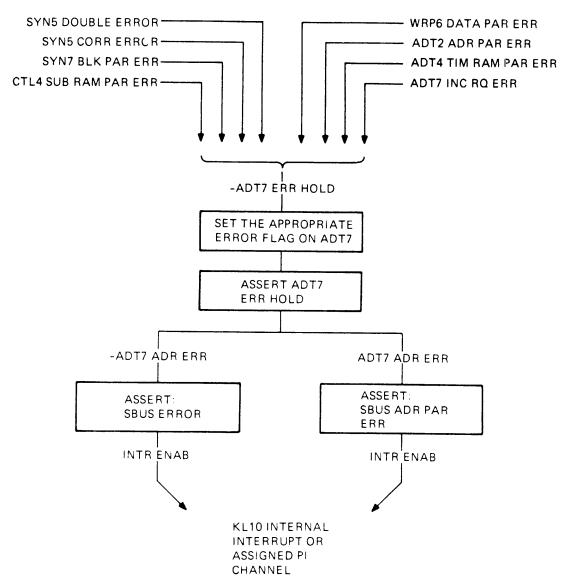

| 5-48          |     | Error Handling Logic - Simplified Flowchart                              |        |

| 5-49          |     | MF20 System Block Diagram                                                |        |

| 5-50          |     | KW20 Functional Block Diagram                                            | .5-128 |

| 5-51          |     | MF20 Clock Signal Distribution                                           |        |

| 5-52          |     | Basic MF20 Timing Logic                                                  |        |

| 5-53          |     | Basic MF20 Timing Waveforms                                              | .5-132 |

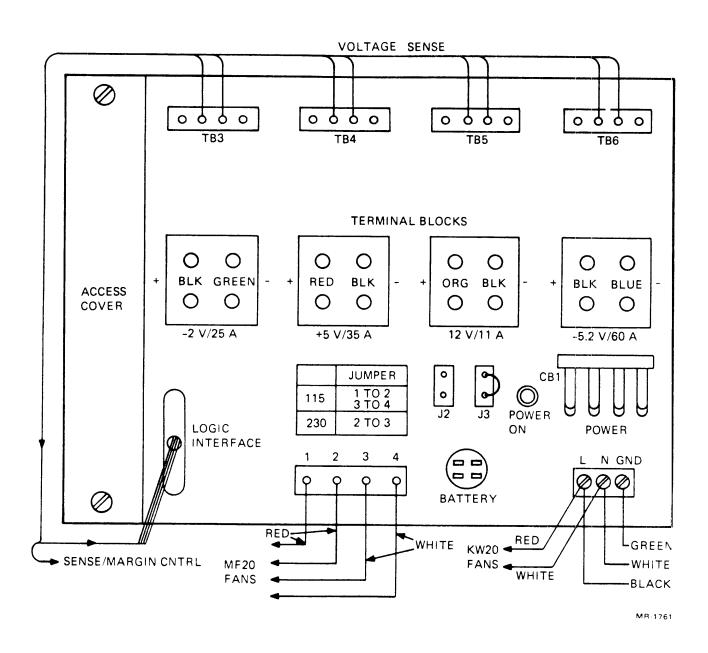

| 5-54          |     | MF20 Power Supply Front Panel                                            |        |

| 5-55          |     | MF20 Power Distribution                                                  |        |

| 5 <b>-</b> 56 |     | Battery Pack                                                             |        |

| 7-1           |     | MF20 Diagnostic Overview Operational                                     |        |

| / - 1         |     | Block Diagram                                                            | 7 – 4  |

| 7-2           |     | MF20 11-Based Diagnostic Test - Simplified                               |        |

| 1 2           |     | Flowchart                                                                | 7-11   |

| 7 – 3         |     | MF20 Diagnostic Overview 10/10 Operational                               |        |

| , 3           |     | Block Diagram                                                            | 7-12   |

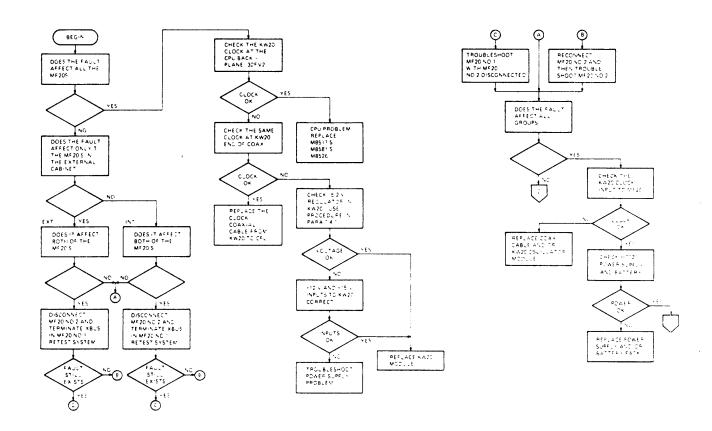

| 7 – 4         |     | Troubleshooting Block Diagram                                            | 7-53   |

| 7 <b>-</b> 5  |     | MF20 Troubleshooting Flowchart                                           | 7-54   |

| 7-6           |     | MF20 Troubleshooting Tops-Down Approach                                  | 7-59   |

| 7-7           |     | MF20 Troubleshooting Bottoms-Up Approach                                 | 7-60   |

| 7-8           |     | KW20 Clock Adjustments                                                   | 7-69   |

| 7-9           |     | MF20 Clock Deskew                                                        | 7-70   |

| 8-1           |     | MF20F Physical Layout                                                    | 8-2    |

| 8-2           |     | MF20F Service Requirement Area                                           | 8-4    |

| 8-3           |     | KL10R and MF20F Service Requirement Area                                 | 8-5    |

| 8-4           |     | KW20 Clock Oscillator                                                    | 8-9    |

| 9-1           |     | MG20-LE/LF Physical Layout                                               | 9-2    |

| 9-2           |     | KL10-D and MG20 Service Area Requirements                                | 9-4    |

| 9-3           |     | MG20 Simplified Module Utilization List                                  | 9-7    |

| 9-4           |     | Memory Module Access                                                     | 9-11   |

| 9-5           |     | M8570 Functional Block Diagram                                           | 9-12   |

| 9-6           |     | MOS Memory Storage Module Simplified                                     |        |

| , ,           |     | Block Diagram                                                            | 9-14   |

| 9-7           |     | Personality PROM - Bit Format                                            | 9-18   |

|               |     |                                                                          |        |

# FIGURES (Cont)

| 9-8 M8570 Storage Module Geography                                  | Figure No.                                                                                                                                                                           | Title                                                                                                                                                      | Page                                      |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Table No. Title Page  1-1 New System Configuration Guide (MOS Only) | 9-9<br>9-10<br>9-11<br>A-1<br>B-1<br>B-2<br>B-3                                                                                                                                      | DC008 Logic Block Diagram                                                                                                                                  | 9-22<br>9-25<br>9-26<br>A-2<br>B-2<br>B-4 |

| New System Configuration Guide (MOS Only)                           |                                                                                                                                                                                      | TABLES                                                                                                                                                     |                                           |

| 1-2                                                                 | Table No.                                                                                                                                                                            | Title                                                                                                                                                      | Page                                      |

| /=V MH/U Primary Error Flags/=5}                                    | 1-2<br>2-1<br>2-2<br>2-3<br>3-1<br>4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>7-2<br>7-6<br>7-7 | Read and Write Cycle and Access Times  MF20-LA/LB, LC/LD Data Sheet (Internal Memory MF20-LH/LJ, LK/LL Data Sheet (External Cabing Installation Scheduling | 1-11<br>1y) 2-3<br>net) 2-4<br>           |

This manual is intended for use by service personnel who have previously been trained in the KL10 and its associated core memory subsystems (MA20, MB20). It assumes the reader is familiar with the KL10 architecture, SBus protocol, and use of the KLAD diagnostic system to load and run diagnostics. It also assumes familiarity with running SYSERR and user mode diagnostics under control of a TOPS-10 and TOPS-20 operating system. Although formal MF20/MG20 training is desirable, the experienced DECsystem-10. DECSYSTEM-20 service engineer should be able to use this manual to service the MF20 and MG20 without special training.

This manual contains ten chapters and three appendices as described in the following paragraphs.

Chapter 1 - Introduction

This chapter provides an overview of the MF20 MOS Memory

Subsystem. It includes a general description, a summary of the

technical specifications, and references to other related

documentation. This chapter answers the question: What is an

MF20 and how does it tie into a KL10-based DECSYSTEM-20?

Chapter 2 - Site Preparation and Planning This chapter contains a detailed physical description of all the major components and subassemblies that comprise the MF20. The information presented is primarily used for site planning and preparation.

Chapter 3 - Installation Procedures

This chapter describes the detailed step-by-step procedures for installing an MF20 option either as a new system installation of as an add-on to an existing configuration. It includes the required checkout procedures to be performed after installing the unit.

Chapter 4 - Operation Programming

This chapter describes the steps required to place the MF20 was state where it can be placed on-line, ready to be used by the operating system. Unlike previous KL10-based memory systems, the MF20 does require a moderate amount of program intervention metable it can be used to store and retrieve data.

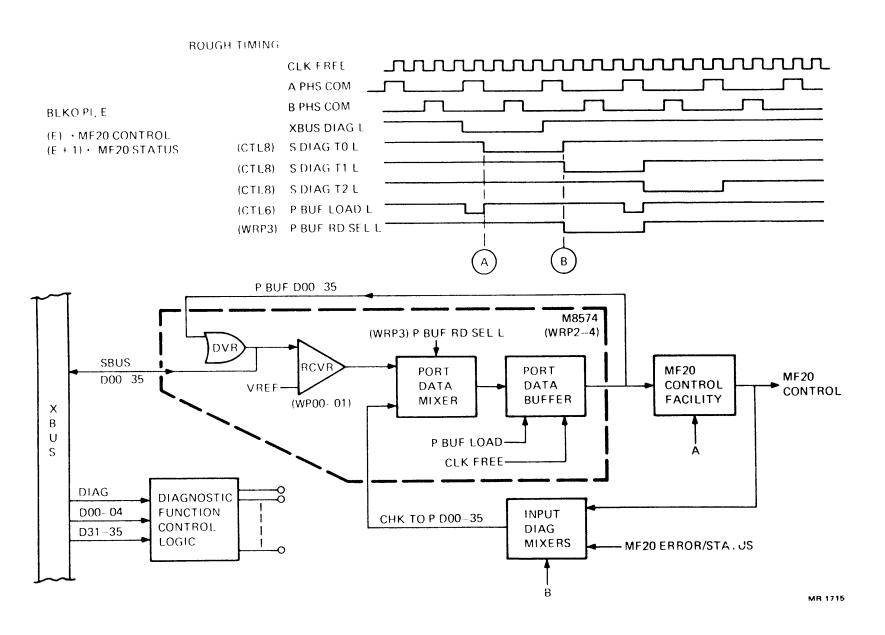

Chapter 5 - Technical Description

This chapter includes a functional description of each major area within the MF20 subsystem. The theory of operation is discussed using block diagrams, tables, and simplified logic diagrams to emphasize how the functional areas of logic interact over to backplane. This treatment is consistent with the probability maintenance philosophy - fault isolation to the module level

Chapter 6 - Preventive Maintenance

This chapter describes the recommended preventive maintenance

procedures and schedules.

Chapter 7 - Corrective Maintenance

This chapter describes the use of hardware and software tools to

repair a failing MF20. It emphasizes the use of both system and

diagnostic software to perform fault isolation. It also includes

descriptions of any required removal, replacement, and adjustment

procedures.

Chapter 8 - MF20F Site Preparation and Installation

This chapter describes the external MOS memory cabinet layout. It

also includes the mechanical, power, and environmental data sheet,

service area requirements, and option variations for the MF20F.

The installation procedures are also outlined in this chapter.

Chapter 9 - MG20 Specific Information This chapter provides an overview of the MG20 internal memory and external cabinet. Site preparation and installation procedures are described.

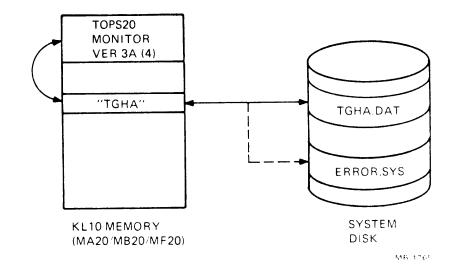

Chapter 10 - TGHA (The Great Heuristic Algorithm)

This chapter explains the use of TGHA with the MF20 and MG20 MOS memories. Examples are provided for both memories.

Appendix A - M8579 Storage Module Geography

This appendix describes the physical layout of the 16K MOS chips

on the storage module and how to determine chip position if the

physical address is known.

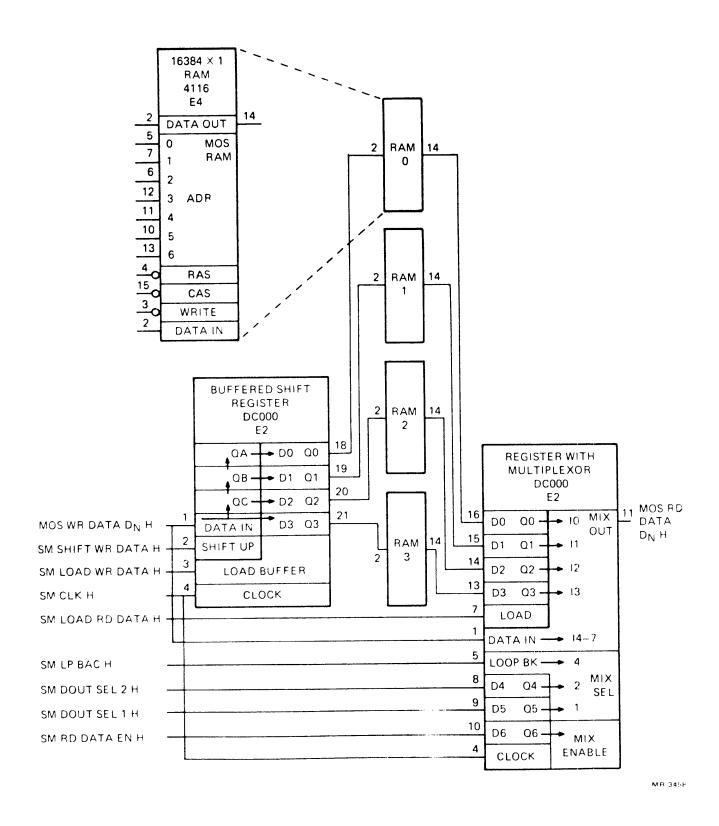

Appendix B - Complex IC Descriptions This appendix describes the operation of the data multiplexer and MOS RAM chips used on the M8579 storage modules.

Appendix C - 11-Based 10 Diagnostic Test Structure

This appendix briefly describes the basic operations involved with

using an 11-based program to test a KL10-based hardware subsystem.

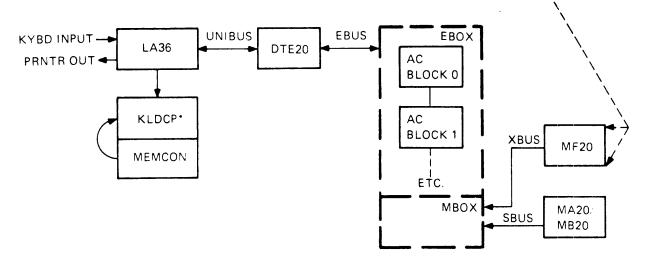

#### 1.1 GENERAL DESCRIPTION

The MF20/MF20F is a MOS Memory Subsystem for use in KL10-based computer systems. The MF20F is an external cabinet. It can provide additional storage for up to 3,145,728 44-bit words in increments of 256K (262,144) words. The MF20 may be installed as the only primary storage resource on a Decsystem-10/DECSYSTEM-20, or it can be added on to supplement existing core memory systems using MA20/MB20 memories. The MF20F may be installed on a KL10-E or KL10-R.

#### 1.1.1 Key Features

Large Capacity - Up to 1.5 megawords can exist on the rear door of a DECsystem-10/DECSYSTEM-20.

High Reliability - Automatic error detection and correction for single-bit errors (SBEs) is coupled with a spare bit substitution mechanism.

Increased MTBF - A sophisticated set of diagnostic functions permits software to continue running by patching out hardware faults. This makes it possible to defer corrective maintenance.

Reduced MTTR - Diagnostic hardware permits the diagnostic programs to access detailed control and data path signals. This provides excellent fault resolution to aid the service engineer.

On-Line Diagnosis - Newly developed software coupled with modifications to existing software permits continual on-line error logging and analysis to provide early warning of any deterioration in the MF20's performance.

Battery Backup - A battery backup power supply system provided adequate dc power to the MF20 to preserve data integrit, for 30 seconds. This is sufficient time to allow switchover to an uninterruptable power source (UPS) in the event of a primary power outage.

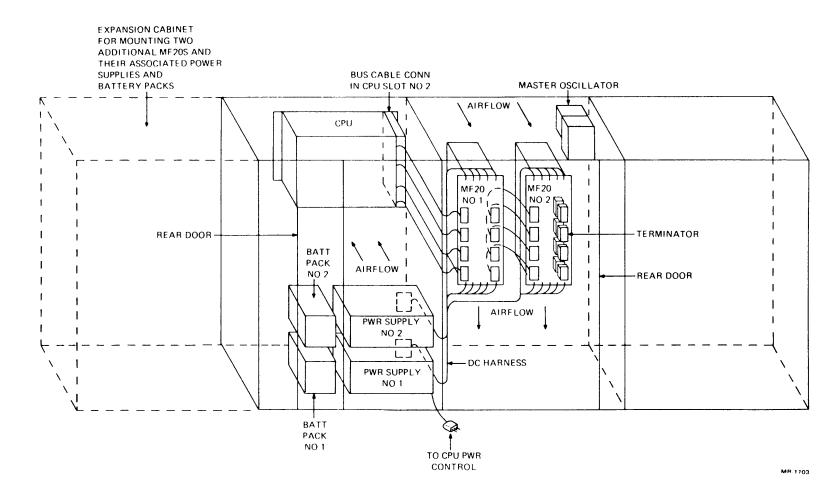

- 1.1.2 Physical Components (Figure 1-1)

The basic MF20 subsystem consists of several components with combine to provide a variety of memory configurations.

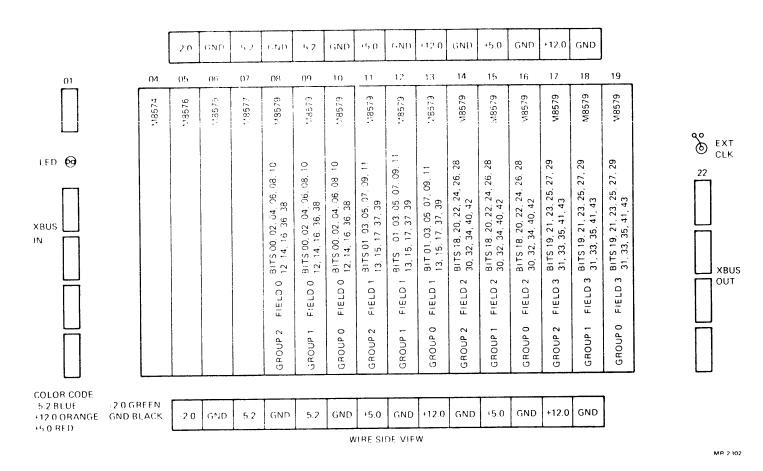

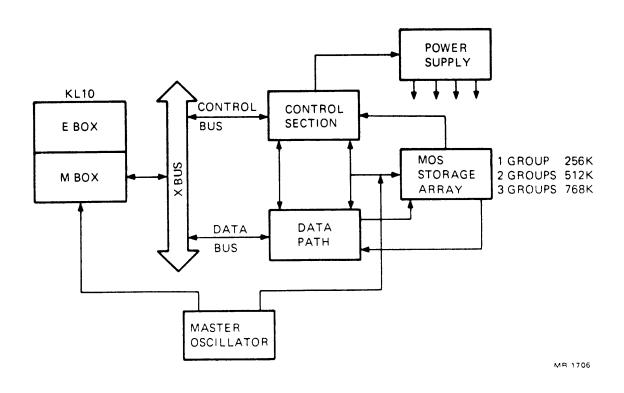

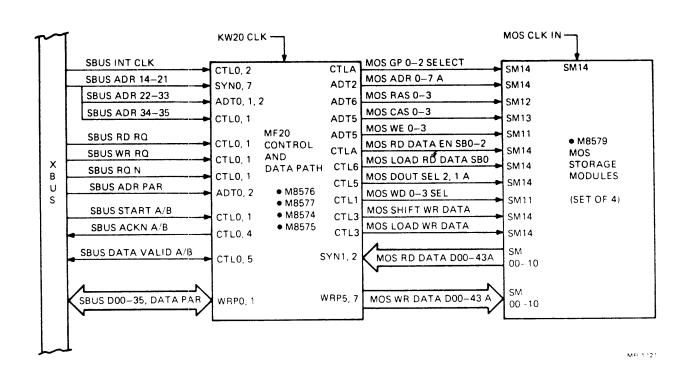

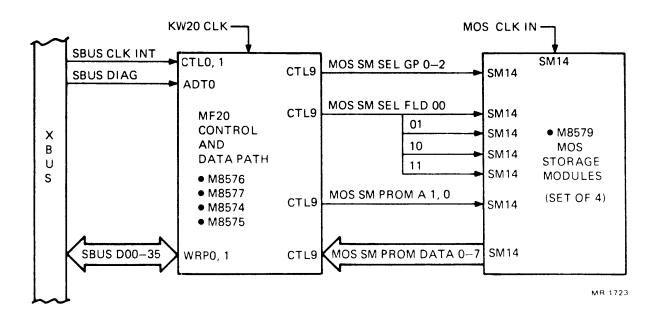

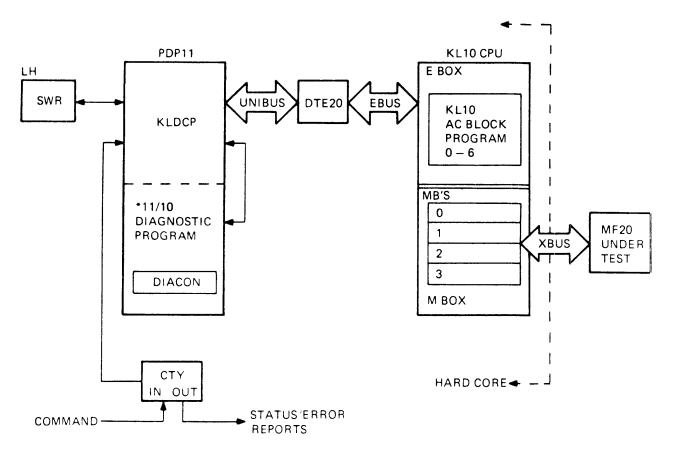

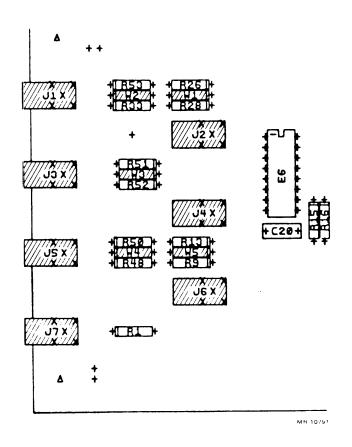

- 1.1.2.1 MF20 Logic Assembly (Figure 1-2) This unit houses all the MF20/MF20F logic modules and consists of the following subassemblies.

- Mounting box complete with printed circuit backplane can accommodate up to sixteen extended-width, hex-height modules

Figure 1-1 MF20 Physical Layout

Figure 1-2 MF20 Simplified Module Utilization Diagram

- 2. Cooling fans

- 3. The following logic modules:

- a. One M8574 write path module

- b. One M8575 syndrome module

- c. One M8576 control and timing module

- d. One M8577 address and timing module

- e. Four M8579 MOS storage array modules [Each set of four M8579 modules provides a capacity of 262,144 44-bit words; up to three sets (12 boards = 786,432 words) can mount in a single MF20.]

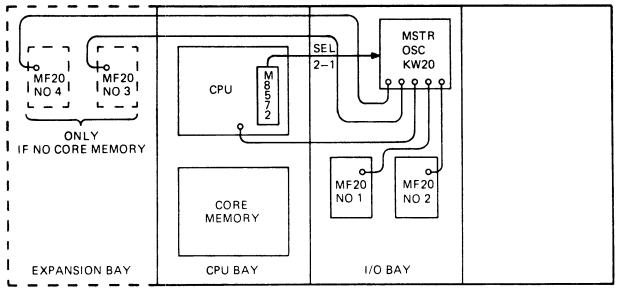

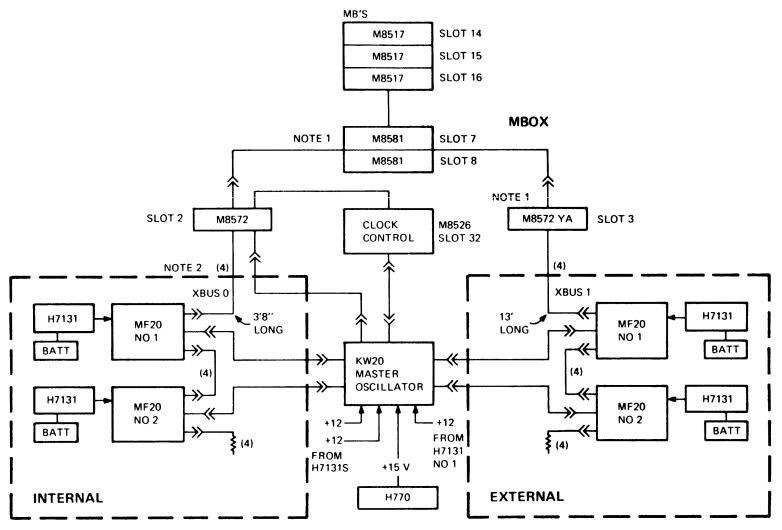

Two MF20 logic assemblies can be mounted on the rear door of the I/O cabinet in a DECSYSTEM-20. In the KL10-R they already exist. An additional pair of MF20 logic assemblies mount in a separate cabinet along with their associated power supplies.

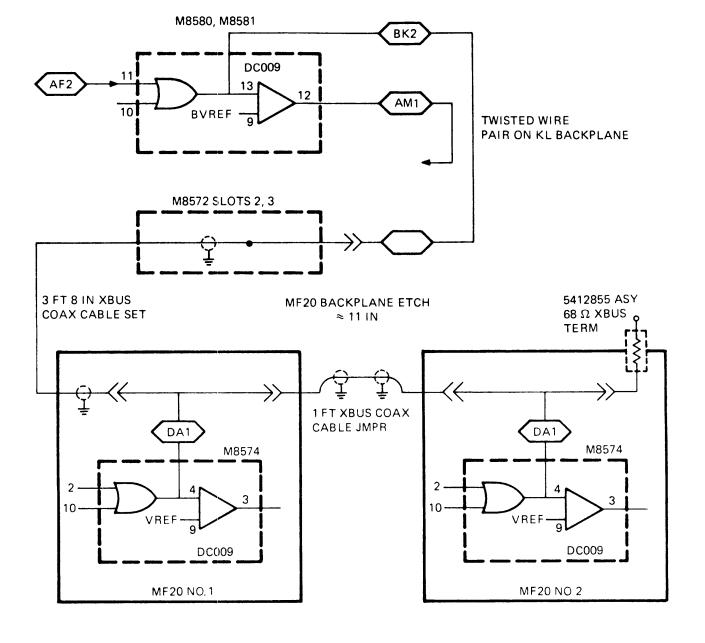

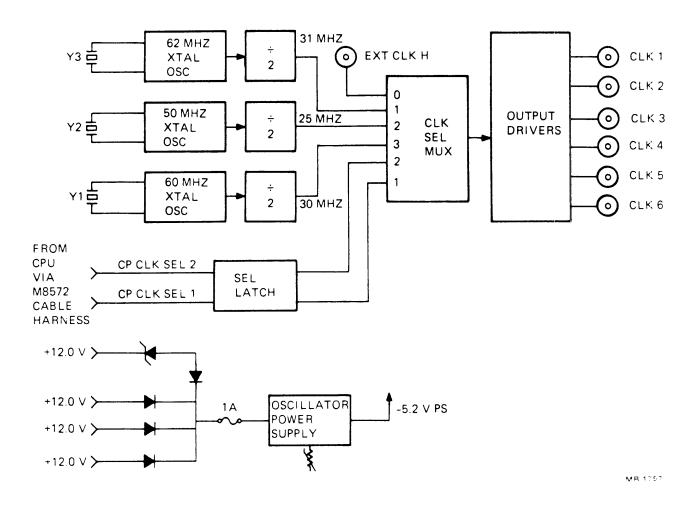

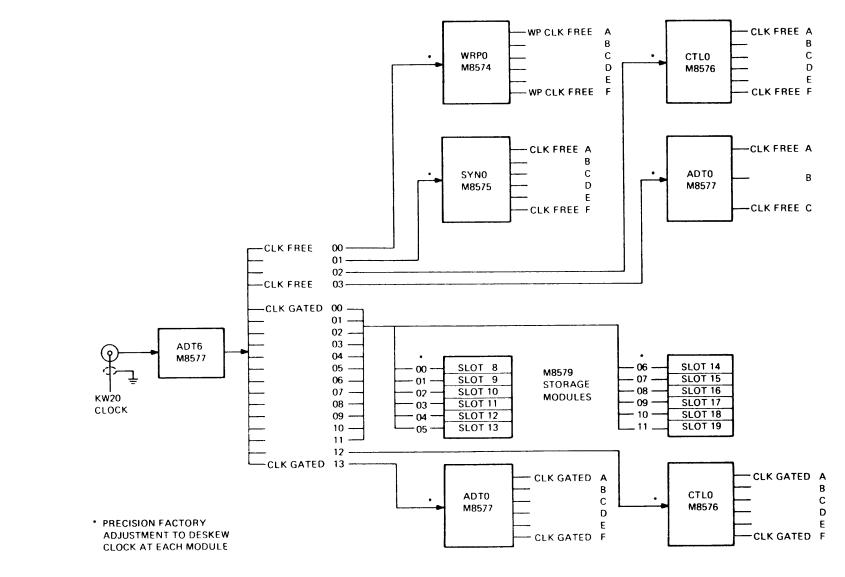

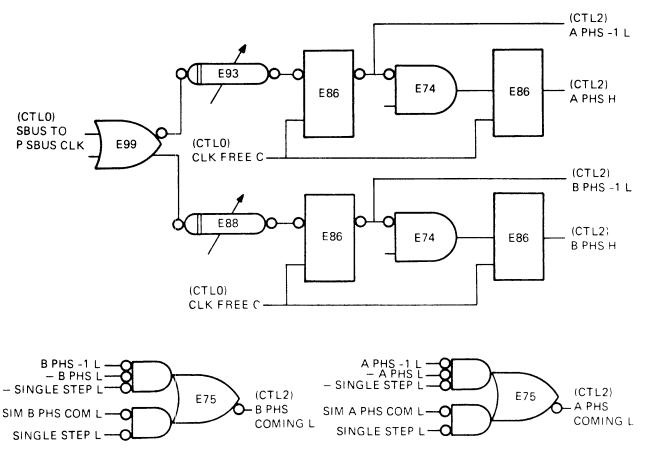

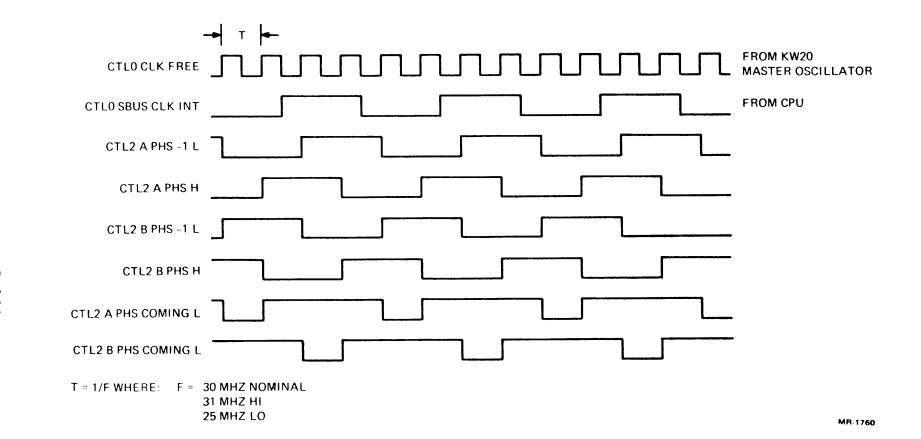

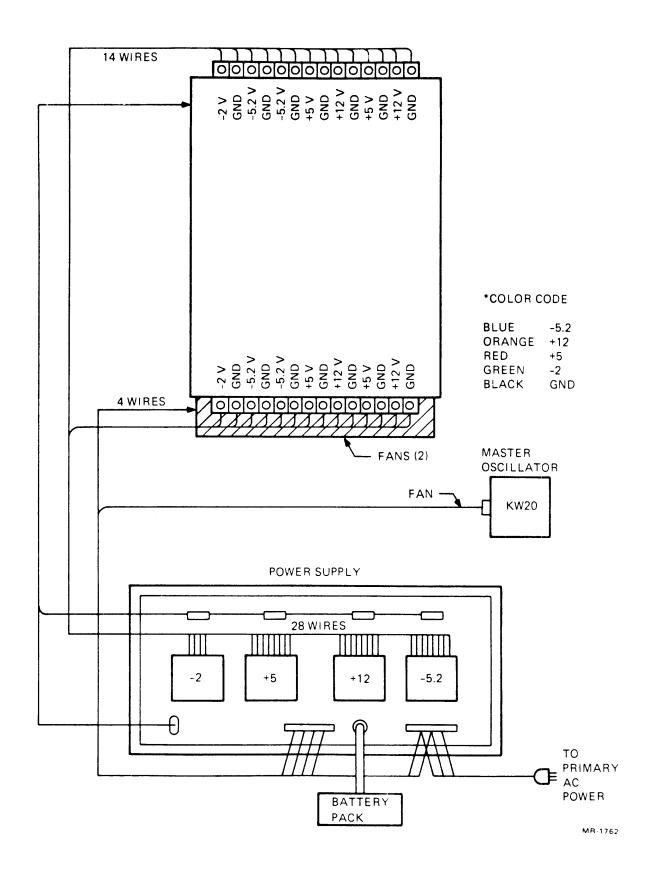

- 1.1.2.2 KW20 Master Oscillator This unit mounts in the upper front of the system I/O cabinet (CPU cabinet in the KL10-R) and contains the clock source that provides timing for both the KL10 CPU and the MF20s. A single KW20 can provide all the clocks required to operate up to four MF20 logic assemblies.

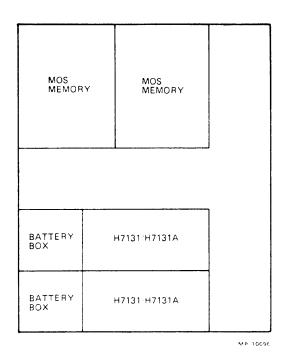

- 1.1.2.3 Power Supply (H7131/H7131-A) A standalone power unit provides all the necessary dc voltages to operate a single MF20. Each MF20 requires a separate power supply. The power supply includes a battery backup assembly that maintains sufficient power to operate the MF20 for up to 30 seconds following a power failure.

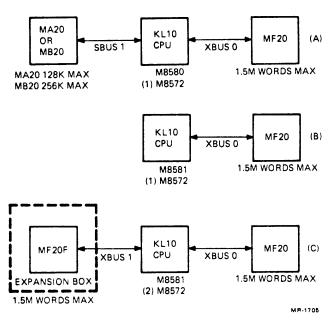

- 1.1.2.4 KL10 CPU Modifications The MF20/MF20F uses an improved version of the KL10's SBus called the XBus. To support the XBus the M8519 SBus translator modules in slots 7 and 8 of the CPU backplane must be replaced as follows.

- 1. Core/MOS mixed configurations use two M8580 modules in place of the M8519s.

- 2. MOS-cnly configurations use two M8581 modules in place of the M8519s.

Besides the translator modules, a quad-height XBus cable connector, the M8572, plugs into slot 2 to connect the MF20 to the CPU via the XBus. A second M8572 (YA version) plugs into slot 3 if an expansion cabinet with additional MF20s is installed.

1.1.2.5 Miscellaneous Components - The MF20 list of physical components includes various cables, power harnesses, terminators, etc. These components will be described in Chapters 2 and 3.

## 1.1.3 Configurations (Figure 1-3)

The MF20 can be configured on single-processor KL10-based systems in integral multiples of 256K (262,144) up to a maximum of 3 megawords (3,145,728). The physical components discussed in Paragraph 1.1.2 are packaged in the following discrete options.

MF20-LA - Basic 256K memory with the master oscillator bcx (KW20); 60 Hz

MF20-LB - 50 Hz version of MF20-LA

MF20-LC - Additional logic assembly and power supply for expansion from 768K to 1.5 megawords on 60 Hz systems

MF20-LD - 50 Hz version of MF20-LC

MF20-E - A set of four M8579 storage modules (a  $\underline{group}$ ) that comprises a 256K expansion unit

MF20-LH - First box of 256K memory packaged in an external cabinet for expansion greater than 1.5 megawords; 60 Hz

MF20-LJ - 50 Hz version of MF20-LH

MF20-LK - Second additional logic assembly and power supply for expansion greater than 2.2 megawords; 60 Hz

MF20-LL - 50 Hz version of MF20-LK

Table 1-1 shows the options that must be ordered to configure an MF20 subsystem of a given capacity. Figure 1-3 shows simplified block diagrams of three possible MF20 configurations.

Figure 1-3 MF20 Configuration

Table 1-1 New System Configuration Guide (MOS Only)

| Storage Capacity                                      | Optior                                                                                       | ns                                                                                                                     |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| (256K Units)                                          | 60 Hz                                                                                        | 50 Hz                                                                                                                  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11 | MF20-LA MF20-E MF20-E MF20-E MF20-E MF20-E MF20-LH MF20-E MF20-E MF20-E MF20-E MF20-E MF20-E | MF20-LB<br>MF20-E<br>MF20-E<br>MF20-E<br>MF20-E<br>MF20-E<br>MF20-E<br>MF20-E<br>MF20-LL<br>MF20-E<br>MF20-E<br>MF20-E |

### NOTE

To compute total capacity in 44-bit words (36 data, 7 check, 1 spare), multiply number of units by 262,144.

Example: 3 units

$3 \times 262,144 = 786,432.$

### 1.1.4 Technical Overview

The MF20 is more than just a replacement for core memory subsystems on the DECsystem-10/DECSYSTEM-20. It is a sophisticated MOS memory storage subsystem with extensive programmable controls that must be set up by the software before it can be used to store and retrieve information. This paragraph provides a brief description of the hardware-software interaction. Refer to Chapter 5 for a complete technical description of the MF20 logic.

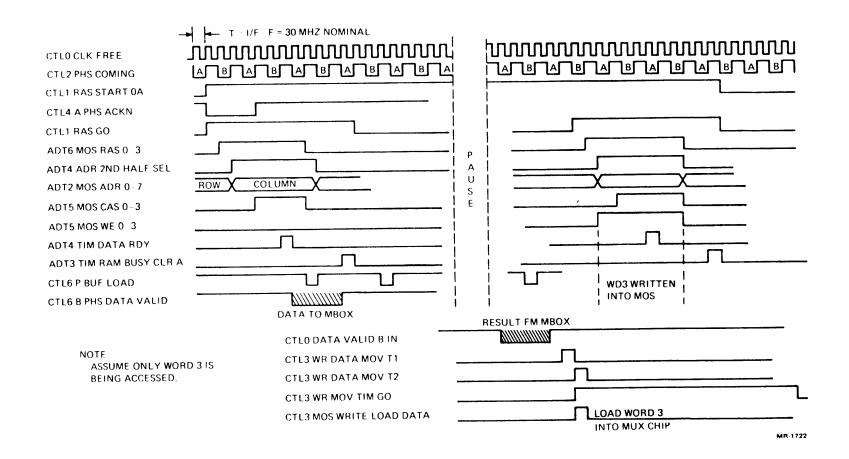

1.1.4.1 Timing and Control - Most memory systems are hard-wired to generate fixed sequences of control and timing signals. These perform the basic read, write, and read-pause-write operations that transfer information between the CPU and the memory's storage array. The pulse widths and repetition rates of these signals are chosen so that the memory circuits operate error-free under worst-case conditions. Once chosen, the circuit parameters of most memory systems are fixed and can only be modified by extensive hardware wiring and circuit changes.

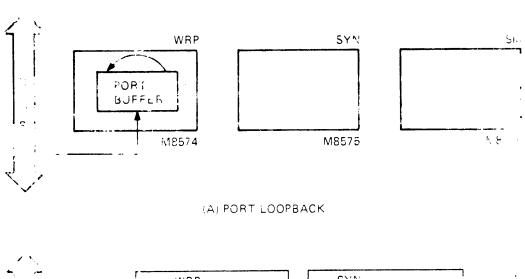

This is not the case in the MF20. A control RAM called the timing RAM is used to establish the signal sequences for accessing the MOS storage array. The actual order and pulse widths of the signals generated become a function of the bit patterns loaded into this RAM. When the MF20 is initially powered on, software resident in the PDP-11 must load the timing RAM to establish the proper control and timing sequences. To modify the timing to compensate for variations between different MOS chip manufacturers, the software simply changes the contents of the timing RAM.

1.1.4.2 Configuration and Patching - Earlier DEC memories established the actual relationship between program address and physical memory modules by setting certain front panel switches. The initial process of setting up these switches was called configuration and required manual operator intervention. If certain memory modules failed, they could be patched out by reconfiguring the switches to place the bad boxes off-line until they could be repaired. If a single bit failed in a particular module, that whole module had to be patched out and the system operated with a considerable loss in its available primary storage resource.

In the MF20 the processes of configuration and patching are automated and programmable. A control RAM called the address response RAM is used to establish the relationship between program address and physical memory modules. Effectively, the software sets the switches by loading the RAM with specific bit patterns. During real-time operations the software can reconfigure the memory to patch out failed areas by simply changing the contents of the RAM.

The chance of a single-bit error (SBE) causing considerable loss in the available MOS resource is minimized by use of a hardware

spare bit mechanism. This consists of spare MOS RAM chips coupled with a control RAM that decides which bit positions are to be substituted for which addresses. This spare bit substitution RAM is loaded by the program to establish the relationship between address and bad-bit position. System software uses the error correction code (ECC) single-bit error detection mechanism coupled with special diagnostic function instructions to determine and log the failing bit position. Using this information the program can set up the spare-bit substitution RAM to substitute the spare bit for the failing bit. The philosophy is based on the fact that single-bit errors are correctable and transparent to the program. If an SBE is substituted for before a second bit fails, the chance that a double-bit error (DBE) will cause a fatal error is minimized. Like the other control RAMs, the spare bit substitution RAM must be initialized by the program during system startup.

- 1.1.4.3 Error Detection and Correction The MF20 contains additional hardware for detecting and correcting errors. It uses a standard ECC code to provide the mechanism for detection and correction of SBEs, and detection only of DBEs. This feature coupled with the spare-bit logic provides the MF20 with extremely high reliability.

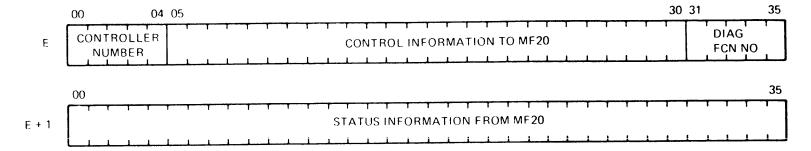

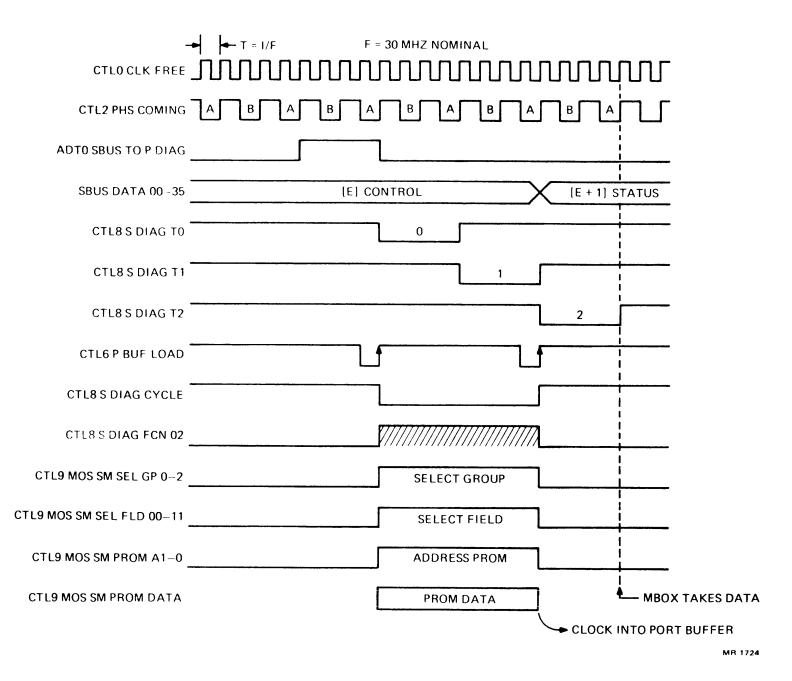

- 1.1.4.4 Fault Isolation Eleven diagnostic functions have been included in the design of the MF20. These diagnostic functions are special instructions that permit the program to load the control RAMs during initialization, configuration, and patching, and to read them during error analysis and recovery. A comprehensive set of diagnostic instructions permits the program to read the states of internal logic signals when analyzing errors. With the ability to gather detailed information about errors, the diagnostic software provides error reports and statistics that enable the service engineer to rapidly locate a failing module and make the repair.

- 1.1.4.5 Summary It is important to recognize the interdependence of hardware and software when working with the MF20. Since the control RAMs are volatile, they must be set up properly by running certain programs. In effect, the MF20 is not an MF20 until the correct information is loaded into the RAMs. Chapter 4 contains a more detailed discussion of this hardware-software interdependency.

#### 1.2 MF20 SYSTEM SPECIFICATIONS

Memory Type Metal Oxide Semiconductor (MOS)

Capacity Minimum 262,144 words Maximum 3,145,728 words

Word Length 44 bits (36 data bits; 6 ECC bits; 1 ECC

parity bit; 1 spare bit)

Interleave Always 4-way

All cells within the MOS array must be Refresh Interval

refreshed once every 2 ms

Read/Write Cycle and See Table 1-2

Access Times

Power Supply

Switching regulator Type

Outputs, dc

+5 V + 1.5% @ 35 A max.+12 V + 1.5% @ 11 A max.-5.2 V + 1.5% @ 60 A max. $-2 V + \overline{1.5}$  @ 25 A max.

Input, ac

Voltage 90-132 Vac

180-264 Vac

12 A @ 120 Vac Current

49-51 Hz Frequency

59-61 Hz

70% Power Factor

Size

66.04 cm X 22.86 cm X 35.56 cm Supply

(26 in X 9 in X 14 in)

20.32 cm X 30.48 cm X 25.4 cm Battery

$(8-5/8 \text{ in } \times 9-3/4 \text{ in } \times 10 \text{ in})$

Weight

30.84 kg (68 lb) Supply

12.6 kg (28 lb) Battery

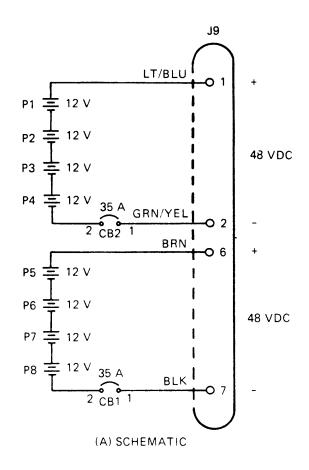

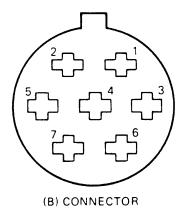

Battery Pack

96 Vdc ncm. in two 48 V segments Voltage

One 35 A circuit breaker for each 48 V Protection

segment

4 mA trickle charge Charge Current

145 + 8 Vdc open-circulated Charge Voltage

90 + 2 Vac rmsCrossover Voltage

Min. Battery Voltage 85 Vdc during discharge

Recharge Time 18 hr for each 30 s discharge time

Environment

$15^{\circ}$  to  $32^{\circ}$  C ( $59^{\circ}$  to  $90^{\circ}$  F) (operating)  $-40^{\circ}$  to  $66^{\circ}$  C ( $-40^{\circ}$  to  $151^{\circ}$  F) (storage) Temperature

20% to 80% (operating) Humidity

0% to 90% (storage)

7° C/hr (12° F/hr) Rate of Change

2%/hr

600 ft<sup>3</sup>/min Air Volume Inlet

KW20 Oscillator

Number of outputs

25 MHz (min.) Frequencies

30 MHz (ncm.) 31 MHz (max.) External Source

Switchable under program control Control

#### 1.3 REFERENCES

## 1.3.1 Drawings

MF20 Field Maintenance Print Set (MP00662) KL10-E Field Maintenance Print Set (MP00300) KL10-PV Field Maintenance Print Set (MP00301) MF20F Field Maintenance Print Set (MP01711) KL10-R Field Maintenance Print Set (MP01708)

#### 1.3.2 Hardware Documentation

The following manuals are available in hard copy from:

Digital Equipment Corporation

444 Whitney Street

Northboro, MA 01532

Attention: Printing and Circulating Services (NR03/W3) Customer Services Section

MBox Unit Description Manual (EK-OMBOX-UD)

KL10-Based DECSYSTEM-20 Installation Manual (EK-0KL20-IN)

DECSYSTEM-20 Site Preparation Guide (EK-DEC20-SP)

KL10-Based Site Preparation, Power System,

Installation Manual (EK-OKL10-SP)

1.3.3 Software Documentation

TOPS-20 Operator's Guide (AA-41760-TM)

TOPS-20 Operator's Guide Addendum (AA-41760-T2)

SPEAR Manual (AA-J833A-TK)

Table 1-2 Read and Write Cycle and Access Times

| Action                                                     | At Memory              | At CPU                 |

|------------------------------------------------------------|------------------------|------------------------|

| Read cycle time                                            |                        |                        |

| Successive reads of 1 word                                 | 733 ns                 | 733 ns                 |

| Read 1 word followed by a write                            | 733 ns                 | 1000 ns                |

| For each additional word of a 2-, 3-, or 4-word read, add: | 200 ns                 | 200 ns                 |

| Write cycle time                                           |                        |                        |

| <pre>1-word write* 4-word write</pre>                      | 867-1133 ns<br>1267 ns | 867-1133 ns<br>1267 ns |

| Read access time                                           |                        |                        |

| Read first word                                            | 533 ns                 | 800 ns                 |

| For each additional word of 2-, 3-, or 4-word read         | 200 ns                 | 200 ns                 |

| Write access time                                          |                        |                        |

| 1-word write                                               | 133 ns                 | 267 ns                 |

| For each additional word of 2-, 3-, or 4-word write        | 133 ns                 | 133 ns                 |

<sup>\*</sup>The time varies depending on the position of the word in a quadword group.

$$\operatorname{\textsc{NOTE}}$$  These times are based on a nominal clock frequency of 30 MHz.

#### 2.1 INTRODUCTION

This chapter provides information necessary to prepare the site prior to installing the MF20, and to schedule and plan the subsequent installation. Since installation of the MF20 option involves a major change to the DECSYSTEM-20's mainframe, it is imperative that the customer and the field service engineer work together to develop an effective installation plan and schedule prior to the arrival of the MF20 at the site. Proper planning will minimize the amount of time the system will be unavailable for customer use.

#### 2.2 SITE PREPARATION

Since the MF20 is an addition to an existing DECSYSTEM-20, the site preparation activity is minimal. Most of the site preparation activity has already been done at the time of the DECSYSTEM-20 installation itself. Any detailed site preparation information required and not found in this document is available in the DECSYSTEM-20 Site Preparation Guide (EK-DEC20-SP). Tables 2-1 and 2-2 provide the detailed mechanical, electrical and environmental data required to plan the installation.

#### 2.2.1 Internal MF20 Options

The MF20-LA/LB, LC/LD options are installed on the rear equipment mounting doors that already exist in the DECSYSTEM-20 cabinets. Refer to Figure 2-1 for the physical details. Since the DECSYSTEM-20 cabinets will already be fixed in place, the floor space requirements have already been defined. The primary consideration prior to receiving the MF20 at the site will be the transportation from the point of delivery at the site to the actual computer room where the DECSYSTEM-20 is located. The MF20 (LA/LB or LC/LD options) will be shipped on a specially fabricated shipping skid with brackets used to mount the following hardware units.

- 1. MF20 logic assembly

- 2. H7131 power supply

- 3. Battery pack

- 4. KW20 master oscillator (MF20-LA/LB only)

The same skid will be reused to remount the MA20 or MB20 if it is to be removed and returned for credit. Refer to Figure 2-2 for a description of the shipping skid.

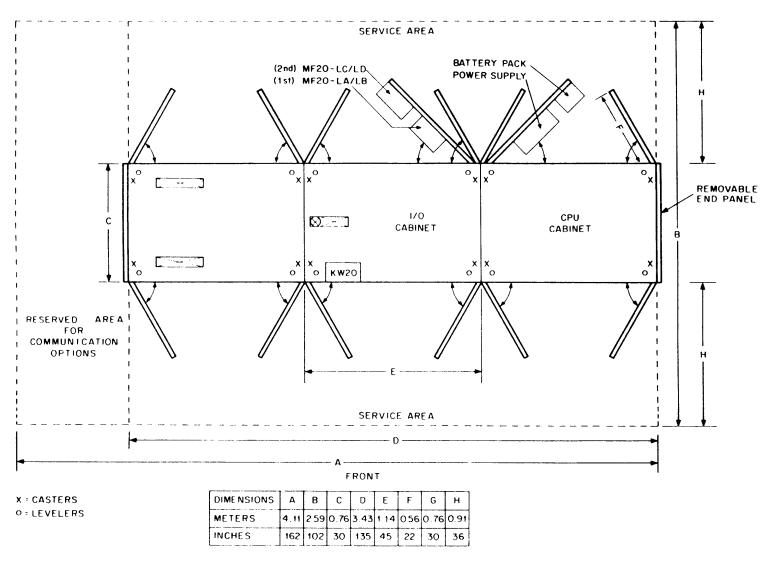

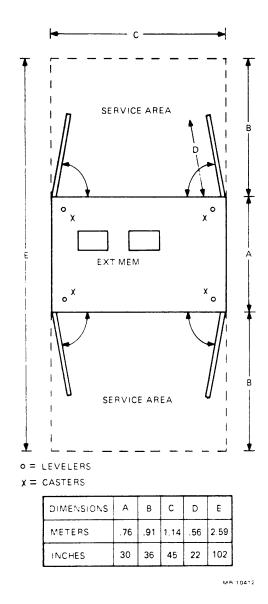

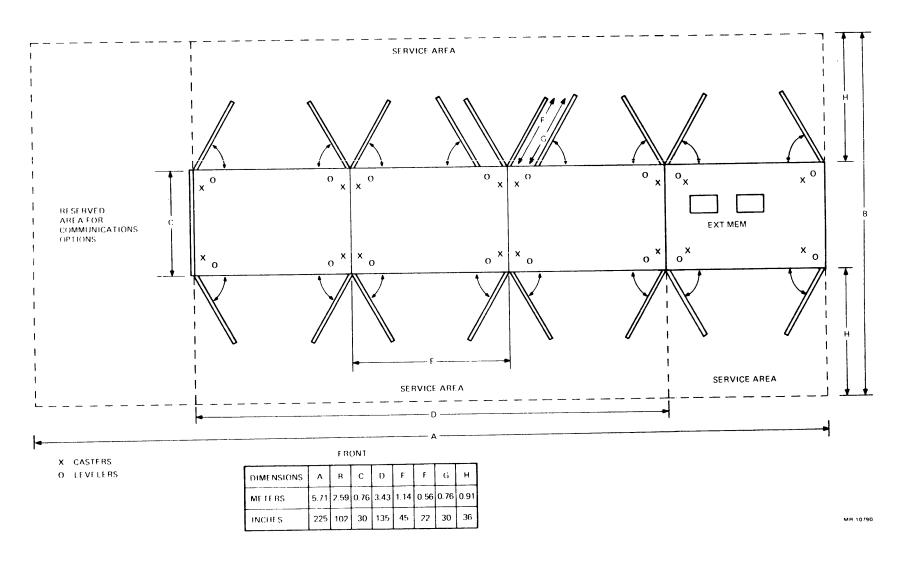

#### 2.2.2 External MF20 Options

The MF20-LH/LJ, LK/LL options mount in a free-standing cabinet that bolts onto the end of the DECSYSTEM-20 to the right of the CPU cabinet (viewed from the front). Refer to Figure 2-3 for the physical details. It is important here to consider the present location of the DECSYSTEM-20 in the computer room. There may not be sufficient space to the right of the CPU cabinet to attach the

\*TWO BATTERY PACKS AND TWO POWER SUPPLIES MOUNTED ONE ABOVE THE OTHER. BOTTOM UNITS ARE FOR FIRST MF20.

MR-2266

# Table 2-1 MF20-LA/LB, LC/LD Data Sheet (Internal Memory)

### MECHANICAL

| Mounting<br>Code | Weight | Height | Width | Depth | Cab Type<br>If Used | Skid<br>Type |

|------------------|--------|--------|-------|-------|---------------------|--------------|

| RM               |        | N/A    | N/A   | N/A   | N/A                 | 9905990-00   |

### POWER (AC)

| Low | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State Current (CRMS) | Surge<br>Current | Surge<br>Duration |

|-----|---------|------------|------------------------|----------|-----------------------------|------------------|-------------------|

| 100 | 115     | 122        | 60 Hz 1                | 1        | 7.6 A                       | 38 A             | less than         |

| 191 | 220     | 233        | 50 Hz 1                |          | 3.8 A                       | 19 A             | 200 ms            |

#### POWER (AC)

| Interrupt Tolerance (Max) | Heat<br>Dissipation          | Watts | KVA | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------|------------------------------|-------|-----|--------------------|--------------------------|-----------------------------|

| 30 s<br>Note 1            | 2390 Btu hr<br>602 kg-cal hr | 700   | 874 | N/A<br>Note 2      | N A<br>Note 2            | .5 m A                      |

### ENVIRONMENTAL (DEVICE)

| Tempe     | Temperature Relative Humidity Rate o |           | f Change | Air Volume          |             |                         |

|-----------|--------------------------------------|-----------|----------|---------------------|-------------|-------------------------|

| Operating | Storage                              | Operating | Storage  | Temp                | Rel. Humid. | Inlet                   |

|           | -40 to 66 C<br>-40 to 151 F          |           | 0-90%    | 7° C≀hr<br>12° F≀hr | 2ºa hr      | 600 ft <sup>3</sup> min |

#### ENVIRONMENTAL (MEDIA)

| Tempe     | ratule  | Relative Humidity |         | Rate of Change |             |

|-----------|---------|-------------------|---------|----------------|-------------|

| Operating | Storage | Operating         | Storage | Temp           | Rel. Humid. |

| NΑ        | ΝÁ      | NA                | N·A     | NA             | NΑ          |

## MAXIMUM CABLE LENGTH AND TYPE(S)

| Memory         | I/O Bus | <b>M</b> as <b>s</b> bus | Device | Other |

|----------------|---------|--------------------------|--------|-------|

| XBus<br>Note 3 | NΑ      | NΑ                       | N∴A    | N A   |

# Table 2-2 MF20-LH/LJ, LK/LL Data Sheet (External Cabinet)

### MECHANICAL

| Mounting<br>Code | Weight                                | Height          | Width           | Depth          | Cab Type If Used | Skid<br>Type |

|------------------|---------------------------------------|-----------------|-----------------|----------------|------------------|--------------|

| FS               | , , , , , , , , , , , , , , , , , , , | 152 cm<br>60 in | 116 cm<br>45 in | 76 cm<br>30 in | 3-H9500          | N/A          |

#### POWER (AC)

|     | C Volta | ge<br>High | Frequency<br>Tolerance | Phase(s) | Steady State Current (CRMS) | Surge<br>Current | Surge<br>Duration |

|-----|---------|------------|------------------------|----------|-----------------------------|------------------|-------------------|

| 100 | 115     | 122        | 60 Hz 1                | 1 1      | 7.6 A                       | 38 A             | less than         |

| 191 | 220     | 233        | 50 Hz 1                |          | 3.8 A                       | 19 A             | 200 ms            |

#### POWER (AC)

| Interrupt<br>Tolerance<br>(Max) | Heat<br>Dissipation          | Watts | KVA | PWR Cord<br>Length | PWR Cord<br>Conn<br>Type | Leakage<br>Current<br>(Max) |

|---------------------------------|------------------------------|-------|-----|--------------------|--------------------------|-----------------------------|

| 30 s<br>Note 1                  | 2390 Btu/hr<br>602 kg·cal/hr | 700   | 874 | N/A<br>Note 2      | N/A<br>Note 2            | .5 ma                       |

#### ENVIRONMENTAL (DEVICE)

| Temperature                  |                                 | Relative I | Relative Humidity |                     | of Change   | Air Volume               |

|------------------------------|---------------------------------|------------|-------------------|---------------------|-------------|--------------------------|

| Operating                    | Storage                         | Operating  | Storage           | Temp                | Rel. Humid. | Inlet                    |

| 15° to 32° C<br>59° to 90° F | -40° to 66° C<br>-40° to 151° F | 20-80%     | 0-90%             | 7° C/hr<br>12° F/hr | 2%/hr       | 600 ft <sup>3</sup> /min |

### ENVIRONMENTAL (MEDIA)

| Tempe     | rature  | Relative  | Humidity | Rate of Change |             |

|-----------|---------|-----------|----------|----------------|-------------|

| Operating | Storage | Operating | Storage  | Temp           | Rel, Humid. |

| N/A       | N: A    | N/A       | N/A      | N/A            | N/A         |

## MAXIMUM CABLE LENGTH AND TYPE(S)

| Memory         | I/O Bus | Massbus | Device | Other |

|----------------|---------|---------|--------|-------|

| XBus<br>Note 3 | N/A     | N/A     | N/A    | N/A   |

# NOTES: (applicable to Tables 2-1 and 2-2)

- 1. Battery back-up supply

- 2. Connects to the 863 power control unit via cabling and connectors supplied with the option

- 3. External memory: One 13 ft XBus cable connects SBus 1 in the CPU cabinet to the MF20 no. 2 in the external cabinet.

Four XBus jumper cables (1 ft) connect MF20 no. 1 to MF20 no. 2 in the external cabinet.

Internal memory: One 3 ft 8 in XBus cable connects SBus 0 in the CPU cabinet to the MF20 no. 1 in the I/O cabinet.

Four XBus jumper cables (1 ft) connect MF20 no. 1 to MF20 no. 2 in the I/O cabinet.

Figure 2-2 KL10-C/E CPU-MF20 LH/LJ Unit Floor Space Requirements

MR-226

\*TWO BATTERY PACKS AND TWO POWER SUPPLIES MOUNTED ONE ABOVE

THE OTHER. BOTTOM UNITS ARE FOR FIRST ME20

MP 2268

Figure 2-3 MF20 LA/LB, LC/LD, LK/LL Packaging

external memory. In this case the entire DECSYSTEM-20 will have to be relocated to a position in the computer room that permits installing the MF20. This could involve considerable changes and must be accomplished prior to receiving the MF20 cabinet on site. As with the internal MF20, the prime consideration prior to receiving the MF20 at the site will be the transportation from the point of delivery at the site to the actual computer room where the DECSYSTEM-20 is located. The MF20 (LH/LJ option) will be shipped on a specially fabricated skid. Refer to Figure 2-4 for a description of the package shipped. Refer to the DECSYSTEM-20 Site Preparation Guide, pages 1-38 for detailed equipment handling information.

#### 2.3 INSTALLATION PLANNING

At least 30 days prior to the scheduled arrival of the MF20 at the computer site, the customer and the field service engineer should meet to plan and schedule the installation. To minimize the amount of time the system must be down during any one day, a 3-phase approach is suggested. The 3-phase approach will also minimize the impact of any unexpected problems that may arise. Without a careful plan these problems could seriously affect the customer's normal work schedules.

## 2.3.1 Phase 1 - Prearrival Activity

#### 2.3.1.2 Mounting Hole Check

1. Power Supply - Check the CPU cabinet rear equipment mounting door for holes and rivnuts in the short member of the door frame as shown in Figure 2-5.

#### NOTE