This drawing and specifications, herein, are the property of Digital Equipment Corporation and shall not be reproduced or copie or used in w ole or in part as the basis for the manufacture or sale of items without written permission.

PDP-K Technical Memoranda # 2

Title:

Extension of PDP-11 Instruction Set

Author(s):

Ad van de Goor

Index Keys:

.

Instruction Sets Opcode Space Modes Stack Operations

Distribution Keys: K

Revision:

Obsolete:

None

None

Date:

21 January 1970

# 0.0 ABSTRACT

Soveral methods of extending the PDP-11 instruction set are discussed. Coding comparisons are made. Subject to the trivial weighting scheme used, two solutions were excluded from further analysis because of their poor performance. The "multiply/ divide" subsolution as discussed in sections 4.4 and 5.4 was the best performer.

## 1.0 INTRODUCTION

A more elaborate version of the PDP-11/20 is considered as a possible candidate for the PDP-K. It is felt that if the PDP-K is a member of the PDP-11 family, substantial gains could be obtained from:

1.1 Upwards Program Compatibility

For DEC this would mean a lower total software investment, and new machines could be introduced more easily as present PDP-11 software would run on PDP-K.

For customers this would mean that they could move to a larger machine without the direct need for reprogramming.

## 1.2 Peripheral Compatibility

Only one line of peripheral devices has to be built. The introductions of a new machine could be done more easily for this reason. Any new peripheral device would be available for the whole family.

## 2.0 PROBLEMS IN ADAPTING THE PDP-11 ARCHITECTURE TO A BIGGER MACHINE

Two important problems of the PDP-11 have to be solved in order to meet the PDP-K requirements.

- 2.1 Limited number of instructions and limited amount of opcode space left. For the PDP-K three more classes of instructions are considered:

- 2.1.1 EAE instructions, i.e., rotate/ shift and multiply/divide for 16-bit words.

- 2.1.2 Double Precision Integer Arithmetic Instructions.

- 2.1.3 Floating Point Arithmetic Instructions.

### 2.2 Limited Address Space

The total amount of addressable core memory on the PDP-11/20 is 65K (1K = is 1024) bytes, or 32K 16-bit words. For a big 32-bit version of the PDP-11 this would only mean 16K 32-bit words could be addressed, which is certainly not adequate for such a machine.

### 3.0 PURPOSE OF MEMORANDUM

The purpose of this memorandum is to examine the suggested methods of solving the first problems: extending the basic PDP-11 instruction set. An acceptable solution, subject to several constraints, will be sought.

- 3.1 Program compatibility at least on the assembly language level.

- 3.2 Simplicity in programming by minimizing the number of instruction formats and restrictions imposed on instructions.

- 3.3 Opcode space left for future expansion.

- 3.4 Opcodes of the largest member of the family have to fit in the added instruction set, thus minimizing the number of formats, and making programming easier.

## 4.0 POSSIBLE SOLUTIONS

Four possible solutions to the opcode space problem are shown below. They are followed by a discussion in section 5:0.

- 4.1 Implement new instructions as "pure stack" instructions (i.e., zero address). Each new instruction can now be specified with one combination out of 2<sup>16</sup>. This allows for hundreds of new instructions. Any binary operation (like multiply, divide, etc.), would take the two operands from the top of the stack, and leave the result on the top of the stack. Register 6 would be used as the implied stack pointer.

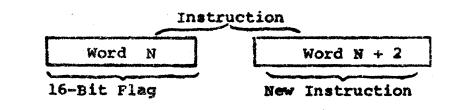

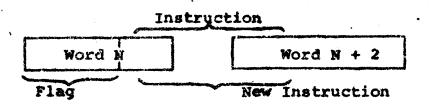

- 4.2 Introduce a flag to indicate that the remainder of the word containing the flag (note: remainder can be = 0) and the next word form a new instruction. Depending on the length of the flag, two cases exist. •

4.2.1 Full Word Flag

4.2.2 Partial Word Flag

The advantage of this technique is that the new instructions can have the same source-destination format as the standard (i.e., current PDP-11/20), instructions. The disadvantage is that every new instruction takes two words. The partial word flag case offers the advantage of a greater number of new instructions at the expense of somewhat more complicated hardware.

## 4.3 Modes

A mode is a (hardware) state of the processor to allow instructions to be interpreted differently. Basically two kinds of modes have to be recognized:

- 4.3.1 <u>Enter</u> and <u>leave</u> modes only with dedicated commands (i.e., only switch modes when an instruction specifies to do so).

- 4.3.2 Enter modes for a specified number of instructions after which the mode is switched back to the standard mode automatically.

The advantage of modes is that instructions in any mode are only 1 word long. The disadvantage is that special instructions have to be given to enter, and in the case of 4.3.1, to leave the mode.

## 4.4 Use Reserved Multiply/Divide Space

These two opcode spaces are not used in the PDP-11/20. The to-be-added two-operand instructions can be implemented as sourcedestination instructions where the stack is one implied operand, and the second operand is specified with the full 6-bit destination field of the instruction. One of these 6 bits can be used as a direction bit such that operations can have either their source or destination as the implied stack. This allows for 32 now instructions to be specified.

## 5.0 EVALUATION OF PROPOSED SOLUTIONS

When evaluating the proposed solutions, the implementation of a 32-bit version of the PDP-11 should be included. For such a machine, double-precision floating point instructions, together with EAE instructions, operating on 32-bit registers are desirable, (assuming that these instructions can operate on registers). This means that opcode space for those instructions has to be reserved to provide for their efficient operation.

Simplicity in programming and machine organization dictate that the number of instruction formats for the three classes of new instructions, (as discussed in section 2.1), should be minimal. In order to make the extended instruction set more acceptable, it is very desirable to make the added instructions fit in currently existing formats, or add at most a single new format. Several coding comparisons are done to assist in the evaluation. The five problems below (Pl-P5), are considered representative. The assumptions made in coding the problems can be deduced from the listed code in Appendixes A-D. The variables A, B, C, D and E are considered single precision floating point (32-bit numbers).

| Pl: | A ← B+C                                      | /simple case             |

|-----|----------------------------------------------|--------------------------|

| P2: | A <b>4</b> −−−− (B+C) ★ (D+E)                | /temporary variable case |

| P3: | A(i) - B(i) + C(i)                           | /subscripted case        |

| P4: | A(i) -B(i+3) *C(i*5)                         | /mixed arithmetic case   |

| P5: | $A(i,j) \leftarrow A(i,j) + B(i,k) + C(k,j)$ | /multi-dimensional       |

|     |                                              | array case               |

P5 is an example of the inner-loop statement of the array multiplication: [A] = [B] + [C] It is assumed that the array bounds are declared from o to u. For array B this would be: Real Array B (0 - bul, 0 - bu2). The first index of B goes to bul, the second to bu2. It will be assumed that the indexes are in registers Ri, Rj, and Rk.

Assuming that the indexes i and j are in register Ri and Rj, the value B (i, j) will be address as follows: Location of B(i, j) = location of B (i.e., startinglocation of matrix) + i\*bul+j).

-7-

## 5.1 Pure Stack Operations

In order to make the pure stack operations efficient, one of the opcode spaces reserved for multiply/divide has to be used for a double move (MOVD' instructions.

MOVD: Move 2 words (32 bits) from S(ource) D(estination). This instruction is required especially in a 32-bit machine. The one binary opcode space left can be used to implement the EAE instructions.<sup>1</sup> The instruction format would be as follows:

|   |   | OPERATION |   | DESTINATION |   |  |

|---|---|-----------|---|-------------|---|--|

| 1 | 3 | 3         | 3 | 6           | ] |  |

|   |   |           |   |             |   |  |

REGISTER

This same format is used for the JSR (subroutine call) instruction. The EAE instructions are made to operate on registers only. The register involved is specified by the 3 "register" bits.

The value of the effective address of the "destination" determines the number of positions to be shifted or rotated. Because the auto-increment and autodecrement modes do not apply to these instructions, one of the 2 mode bits can be used to specify a single or combined operation, (i.e., see PDP-10 LSH, LSHC, etc.). The remaining space can be used to implement instructions like EXCHANGE, REPEAT, etc.

Appendix A gives the coding examples for the five problems. The handling of multi-dimensional arrays is very cumbersome because the address computations have to be done on the stack. Introducing a second set of 16-bit multiply/divide instructions implemented as the above EAE instructions will solve this problem at the expense of a more complex instruction set. Subcolumn Table 1 MPD of Section 6 shows the improvement gained by this.

<sup>1</sup>Except for 16-bit multiply/divide

-8-- \*

### 5.2 Flagged Instructions

The coding examples shown in Appendix B are the same for alternatives 4.2.1 and 4.2.2. 4.2.2 Is preferable only if the additional opcode space is needed. It is suggested that the EAE multiply/ divide instruction will be implemented in the space "reserved" for them. The EAE rotate/shift instructions have to be implemented as "flagged" instructions, the format would be similar to that discussed in section 5.1., except for the flag. The double precision integer and floating point instructions would be implemented as full sourcedestination instructions.

## 5.3 Modes

Before going into detail, proposal 4.3.2 (setting the modes for a specific number of instructions (N)), will be examined. This is considered less attractive because of problems arising in a string of N<sup>1</sup> instructions to be executed in the new mode.

- 5.3.1 Branching in terms of skipping over a group of instructions in the specified string will cause problems because N is not updated automatically.

- 5.3.2 Programming will be very difficult because when branching into a sequence of instructions their mode, (in which those operate), will be difficult to determine.

- 5.3.3 It will be difficult for a compiler to set up the right "N" because it will require some kind of "lock-ahead".

- 5.3.4 In case of interrupts/traps, the remainder of N has to be saved and restored upon exit of the interrupt/trap service routine.

Where N is an arbitrary positive number.

The extended mode, (which contains the floating, double-precision integer instructions, etc.), is entered by the command Enter Extended Mode (EEM). The processor stays in this mode until the instruction Leave Extended Mode (LEM) is given.

In regard to 4.3.1, subroutine calls and interrrupt/traps cause problems typical for modes in saving/restoring the mode and entering the routine (subroutine or interrupt/trap service routine), in the correct mode. The interrupt/ trap case is the easiest one. The mode can be preserved in a dedicated bit in the Central Processor Status Register(PS). Entering the interrupt/trap service routine in the right mode can be done similarly by storing the mode of that routine in the PS interrupt/trap vector. The correct mode will then be entered automatically upon interrupt.

Entering a subroutine in the desired mode in a program compatible way can be done by taking the lowest bit (bit 0) of the subroutine address as the mode bit. In the current PDP-11/20, this bit has to be equal zero because the subroutine address is a word address. By defining a "0" in bit 0 of the subroutine address as the standard mode, program compatibility is preserved.

Saving/restoring the mode upon a subroutine call/ exit is much more difficult. The only hardware solution found thus far is to store the mode on the stack in a separate word. The new JSR would then store 2 words on the stack: the register to be saved and the mode. Programs making use of the knowledge that only 1 word gets stored on the stack by a JSR have to be modified.

A program compatible software solution to the mode problem is to have the called subroutine take care of the mode handling by restoring the mode (upon exit), which existed prior to the call of the subroutine. A possible way of doing this is by having the existing mode, prior to all calls for a given subroutine, fixed, such that the subroutine only has to match the mode upon exit to the existing (fixed) mode at call time.

It is suggested that the multiply and divide instructions, (operating on 16-bit integers), be implemented in the space reserved for them, and all other instructions be implemented in the extended mode.

Appendix C shows the coding examples. They suggest that an instruction to enter the extended mode for a single instruction is very useful. The column EEM1 (Enter Extended Mode for 1 Instruction), of Table 1, Section 6, shows this.

## 5.4 Use Mutliply/Divide Space

One of the two binary opcode spaces has to be used to implement the EAE instructions as described in section 5.1. The remaining instructions have to implemented with the stack as an implied operand as discussed in section 4.4. Coding examples are given in Appendix D. They show, like the "pure stack" case, that handling multi-dimensional arrays is cumbersome. The improvements made by adding a set of 16-bit multiply/divide instructions, as suggested in section 5.1, are shown in subcolumn MPD of Table 1, Section 6.

## 6.0 COMPARISON OF PROPOSED SOLUTIONS

Table 1 shows the results of the five problems for the seven] proposed solutions. Four quantifiers are used for each problem to measure the quality of the solutions.

6.1 The Number of Instructions

It is quite well known that the probability of making a programming error increases more than linear with the number of instructions, (apart from their complexity), thus a "good" solution should have a low number of instructions.

6.2 The Number of Words<sup>2</sup>

This is the number of words needed to core the algorithms given in the appendixes. This is an important criterium, especially on a small machine. For a 32-bit machine the numbers have to be divided by 2.

6.3 The Number of Memory References

The number of memory references both for a 16 and 32-bit machine are included in the tables because they are important indicators for the execution times of the algorithms. The numbers in Table 1 are derived under the following assumptions:

- 6.3.1 The stack is supposed to be in corememory. (Section 6.4 discusses the results when this assumption is not made).

- 6.3.2 For the two operand extended instructions the arithmetic unit is supposed to behave as follows: 1) reads both operands into its internal registers; 2) it performs the required operation (e.g. FMUL, FADD); and 3) it stores the results back. In case of different assumptions the numbers in the table can be adjusted accordingly.

<sup>1</sup>Four main solutions, three of which have a subsolution. <sup>2</sup>Words are considered to be 16 bits long.

#### .

# 6.4 Number of Memory References With A Hardware Stack

The idea is to implement the top M<sup>1</sup> words of the stack in flip-flop registers. From Table 1 it can be seen that the execution speed increases for almost all problems and solutions. Those solutions making heavy use of the stack gain most.

<sup>1</sup>For simplicity M is supposed to be such that in none of the problems the stack "overflows" into core.

# TABLE 1 - CODING RESULTS OF PROBLEMS P1 + P5

.

| POBLEM  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                      | PURE STA                                              | СК                            |                                        | MODE                       |                                | MULTIPLY/D                     | Statistics of the second s |

|---------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------|----------------------------------------|----------------------------|--------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| NUTBERS | QUANTIFIER                                                                                  |                                                       | MPD                           | FLAG                                   |                            | EEM1                           |                                | MPD                                                                                                            |

| 1       | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref With Hardware Stack</pre> | 4<br>7<br>25/12.5 <sup>1</sup><br>13/6.5 <sup>1</sup> | 4<br>7<br>25.12.5<br>13/6.5   | 2<br>8<br>18/9<br>18/9                 | 4<br>8<br>18/9<br>18/9     | 4<br>8<br>18/9<br>18/9         | 3<br>6<br>20/10<br>12/6        | 3<br>6<br>20/10<br>12/6                                                                                        |

| 2       | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref With Hardware Stack</pre> | 8<br>13<br>51/25.5<br>23/11.5                         | 8<br>13<br>51/25.5<br>23/11.5 | 5<br>17<br>43/ <b>2</b> 1.5<br>35/17.5 | 7<br>14<br>40/20<br>32/16  | 7<br>14<br>40/20<br>32/16      | 6<br>11<br>41/20.5<br>21/10.5  | 6<br>11<br>41/20.5<br>21/10.5                                                                                  |

| 3       | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref With Hardware Stack</pre> | 4<br>7<br>25/12.5<br>13/6.5                           | 4<br>7<br>25/12.5<br>13/6.5   | 2<br>8<br>18/9<br>18/9                 | 4<br>8<br>18/9<br>18/9     | 4<br>8<br>18/9<br>18/9         | 3<br>6<br>20/10<br>12/6        | · 3<br>6<br>20/10<br>12/6                                                                                      |

| 4       | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref With Hardware Stack</pre> | 10<br>15<br>39/22.5<br><b>21/10.5</b>                 | 8<br>13<br>31/15.5<br>19/9.5  | 6<br>14<br>24/12<br>24/12              | 10<br>16<br>26/13<br>26/13 | 8<br>14<br>24/12<br>-<br>24/12 | 8<br>13<br>31/16.5<br>19/9.5   | 7<br>12<br>26/13<br>16/8                                                                                       |

| 5       | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref With Hardware Share</pre> | 21<br>28<br>74/46<br>36/18                            | 15<br>22<br>46/23<br>28/14    | 12<br>21<br>37/18.5<br>29/14.5         | 18<br>24<br>40/20<br>32/16 | 15<br>21<br>37/18.5<br>29/14.5 | 16<br>23<br>55/30.5<br>31/15.5 | 13<br>20<br>40/20                                                                                              |

Table 2 gives a rating summary of Table 1, the rating is from 1 (lowest), to 7 (highest). When two solutions have equal rating, they both get the same number being the average rating when they would not have been equal.

The problems Pl - P3 are very similar in nature, therefore a summarized rating is given in the first part of Table 2. Similarly, for P4 - P5 in the second part of Table 2. The third part of Table 2 is a summary of the previous two tables assuming equal weights for the two previous groups of problems. Part 4 of Table 2 is merely the sum of the first two quantifiers of the third part.<sup>1</sup> For a small machine. the number of instructions and the number of words are the most important criteria. for selecting the best solution. On a bigger machine, execution speed is becoming important. Part 5 of Table 2 is such an indicator. Tte entries are the sums of the first, second, and fourth quantifiers of part 3. It is assumed that on the bigger machine the top of the stack is implemented in hardware.

<sup>1</sup>Again here, for simplicity reasons, equal weights are assumed.

# TABLE 2 - RATING SUMMARY OF CODING PROBLEMS

| PART         | QUANTIFIER                                                              | PURE STACK            |                       |                      | MODE                  |                            | MULTIPLY DIVIDE                          |                       |

|--------------|-------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|-----------------------|----------------------------|------------------------------------------|-----------------------|

| PROBLEMS     |                                                                         |                       | MPD                   | FLAG                 |                       | EEMI                       | an a | MPD                   |

| 1<br>Pl - P3 | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref</pre> | 1.5<br>4.5<br>1.5/1.5 | 1.5<br>4.5<br>1.5/1.5 | 7<br>1<br>5/5        | 3.5<br>2.5<br>6.5/6.5 | 3.5<br>2.5<br>6.5/6.5      | 5.5<br>6.5<br>3.5/3.5                    | 5.5<br>6.5<br>3.5/3.5 |

|              | With Hardw <b>are</b><br>Stack                                          | 4.5/4.5               | 4.5/4.5               | 1/1                  | 2.5/2.5               | 2.5/2.5                    | 6.5/6.5                                  | 6.5/6.5               |

| 2<br>P4 - P5 | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref</pre> | 1<br>1<br>1/1         | 4.5<br>5<br>3/3       | 7<br>5<br>6.5/6.5    | 2<br>2<br>4.5/4.5     | <b>4.5</b><br>5<br>6.5/6.5 | 3<br>3<br>2/2                            | 6<br>7<br>4.5/4.5     |

|              | With Hardware<br>Stack                                                  | 2/2                   | 6/6                   | 3.5/3.5              | 1/1 •                 | 3.5/3.5                    | 5/5                                      | 7/7                   |

| 3<br>Pl - P5 | <pre># of Instructions # of Words # of Memory Ref # of Memory Ref</pre> | 2.5<br>5.5<br>2.5/2.5 | 6.0<br>9.5<br>4.5/4.5 | 14<br>6<br>11.5/11.5 | 5.5<br>4.5<br>11/11   | 7.5<br>7.5<br>13/13        | 8.5<br>9.5<br>5.5/5.5 .                  | 11.5<br>13.5<br>8/8   |

|              | With Hardware<br>Stack                                                  | 6.5/6.5               | 10.5/10.5             | 4.5/4.5              | 3. <b>5/3.5</b>       | 6/6                        | 11.5/11.5                                | 13.5/13.5             |

| 4            | <pre># of Instructions     + Number of     Words</pre>                  | 8                     | 15.5                  | <b>2</b> 0           | 10.0                  | 15.0                       | 18.0                                     | 25                    |

| -5           | # cf Memory Ref<br>With Hardware<br>Stack                               | 14.5                  | 26                    | <b>2</b> 4.5         | 13.5                  | 21.0                       | 29.5                                     | 38.5                  |

-16-

## 7.0 CONCLUSION

Looking at Table 2, part 4 and 5, it can be consluded that the subsolutions, (i.e., MPD for "pure stack" and "multiply/divide", and EEM1 for "mode"), are a big improvement over their "main" solutions. This, because of the improved handling of multi-dimensional arrays, the price paid for this, however, is a more complex instruction set (i.e., adding a duplicate set of 16-bit multiply/divide instructions to operate on register or enter the extended mode for a single instruction).

The main solutions "pure stack" and "mode" have the lowest rating and can therefore be excluded from further consideration.

In order to make a definite commitment to any of the remaining five solutions, more research should be done in determining the weights of the problems and weights of the quantifiers.

From the results, this far however, the following can be said:

7.1 The "mode" subsolution has to look much better<sup>1</sup> in order to be a candidate because of the mode problems in subroutines. The suggested hardware solution is such that the price of storing the mode on the stack has to be paid ALWAYS. Also, in programs which do not make use of the mode, (i.e., all current PDP-11 software). For this reason the suggested software solution is a better candidate because there, the price is only paid when modes are used.

<sup>1</sup>When the proper weights are found.

- 7.2 The "flag" solution is advisable only when it is expected that the use of the "flagged" instructions (i.e. those of class 2.1.2 and 2.1.3 of section 2) is low.

- 7.3 The most promising solution this far is the "multiply/divide" subsolution. It consistently scored highest or second highest

•

# APPENDIX A

PURE STACK CODING EXAMPLES

| Pl:         | A         | — B*C            |                                                         |

|-------------|-----------|------------------|---------------------------------------------------------|

|             | llovd     | C, - (SP)        | /move C to the stack                                    |

|             | IIOVD     | B, - (SP)        | /move B to the stack                                    |

|             | I'MUL     |                  | /floating multiply B*C                                  |

|             | VOVD      | (SP) +, A        | /store result in A                                      |

| P2:         | A <b></b> | (B+C) * (D+E)    |                                                         |

|             | MOD       | <b>B</b> , (SP)  |                                                         |

|             | MCTD      | C, - (SP)        |                                                         |

|             | FPD       | •                | /floating add B+C                                       |

|             | MC/D      | $D_{i} - (SP)$   | -                                                       |

|             | MOD       | E, - (SP)        | · · · · · · · · · · · · · · · · · · ·                   |

|             | FAD       |                  | /floating add D+E                                       |

|             | PNIL      | •                | /floating multiply (D+E) + (B+C)                        |

|             | MCND      | (SP) +, A        |                                                         |

| <b>P3</b> : | A (i) 🗲   | -B(i) *C(i)      | /assume index i is in register Ri                       |

|             | MOVY      | C(R1), - (SP)    | /move C(i) to the stack                                 |

|             | MOV       | B(R1), - (SP)    |                                                         |

|             | FMU',     |                  |                                                         |

|             | MOV)      | (SP) +, A(Ri)    |                                                         |

| P4:         | k(i 🔫     | B (1+3) +C (1+5) | /Rs.is a scratch register                               |

|             | MOV       | Ri, Rs           |                                                         |

|             | ADD       | #3, Rs           | /index i+3 formed                                       |

|             | (IVC M    | B(Rs), - (SP)    |                                                         |

|             | MOV       | Ri, - (SP)       |                                                         |

|             | MOV       | #5, - (SP)       |                                                         |

|             | IMUL      |                  | /compute i*5 and leave 1 word result<br>on top of stack |

|             | MOV       | (SP)+, R#        |                                                         |

|             | MOVD      | C(Rs), - (SP)    |                                                         |

|             | FMUL      |                  | •                                                       |

|             | NOVD      | (SP)+, A(R1)     | /store result                                           |

|             |           | •                |                                                         |

•

APPENDIX A (CONT.)

P5: A(i,j) - A(i,j) + B(i,k) + C(k,j)

| MOV  | Ri, - (SP)      |                                |

|------|-----------------|--------------------------------|

| MOV  | #bul, - (SP)    |                                |

| TMUL |                 |                                |

| MOV  | (SP)+, Rs       |                                |

| ADD  | Rk, Rs          | /Rs contains index for array B |

| MOVD | B(Rs), - (SP)   | /put B(i,k) on stack           |

| MOV  | $Rk_{e} - (SP)$ | · · · · ·                      |

| MOV  | #cul, - (SP)    |                                |

| IMUL |                 |                                |

| MOV  | (SP)+, Rs       |                                |

| ADD  | Ri, Rs          | /Rs contains index for array C |

| DVD  | C(Rs), $-(SP)$  | _                              |

| FMUL | 'n              |                                |

| MOV  | Ri, - (SP)      |                                |

| MOV  | #aul, - (SP)    |                                |

| IMUL |                 |                                |

| MOV  | (SP)+, Rs       |                                |

| ADD  | Rj, Rs          | /Rs contains index for array C |

| MOVD | A(Rz), - (SP)   | •                              |

| FADD | •               |                                |

| MOVD | (SP)+, A(Rs)    | /store result                  |

.

## APPENDIX B

## FLAGGED INSTRUCTIONS CODING EXAMPLES

**P1:** -B\*C Α 🗲-MOVD B,A /move B to A FMUL C,A P2:  $-(B+C) \star (D+E)$ λ 🚄 MOVD B,A FADD C,A /A = B+C nowMOVD  $D_{,-}(SP)$ FADD C, (SP) /top of the stack is C+D (SP)+,AFMUL λ(i) 🖛 P3: -B(i) \*C(i)MOVD B(Ri), A(Ri) /move B(i) to A(i) FADD C(Ri), A(Ri) P4: λ(i) 🕳 -B(i+3)\*C(i\*5) /Rs is a scratch register MOV Ri, Rs ADD #3, R# /index for B(i+3) computed B(Rs), A(R1) MOVD MON7 Ri, Rs **#5, Rs** MUL /index for C(i\*5) computed FMUL C(Rs), A(Ri) P5: A(i,j) --A(i,j) + B(i,k) + C(k,j)MOV Ri, Rs #bul, Rs MUL /index for B(i,k) computed ADD Rk, Rs MOVD B(Rs), - (SP) Rk, Rs MOV MUL #cul. Rs ADD Rj, Rs /index for C(k, j) computed FMUL C(Rs), (SP) MOV Ri, Rs #aul, Rs MUL ADD Rj, RS /index for A(i,j) computed FADD (SP) +, A(Rs)

## APPENDIX C

## MODE CODING EXAMPLES

. •

٠

| E          | ?1:    | A       | B*C                    |                             |

|------------|--------|---------|------------------------|-----------------------------|

|            |        | EEM     |                        | /enter extended mode        |

|            |        | MOVD    | В,А                    | / Enter extended mode       |

|            |        | FMUL    | C,A                    | •                           |

|            |        | LEM     | 0/m                    | /leave extended mode        |

|            |        |         |                        | / Texto carcuided move      |

| 5          | 2:     | A       | -(B+C) * (D+E)         |                             |

| -          |        |         |                        |                             |

|            |        | EEM     |                        | /enter extended mode        |

|            |        | MOVD    | B,A                    |                             |

|            |        | FADD    | C,A                    |                             |

| <b>.</b> . |        | MOVD    | D,-(SP)                |                             |

|            |        | FADD    | C, (SP)                |                             |

|            |        | FMUL    | (SP)+,A                | •                           |

|            |        | LEM     |                        | /leave extended mode        |

|            | - 41   |         |                        |                             |

| 1          | P3:    | A(i)    | - B(i) * C(i)          | ·                           |

|            |        | REM     |                        |                             |

|            |        | NOVD    | B(Ri), A(Ri)           |                             |

|            |        | FMUL    | C(R1), A(R1)           |                             |

|            |        | LEM     |                        |                             |

|            |        |         |                        |                             |

| 1          | 14:    | A(i)    | -B(i+3) *C(i*5)        |                             |

|            |        | 4011    | ni na                  | •                           |

|            |        | MOV     | Ri,Rs                  |                             |

|            |        | ADD     | #3, R <b>s</b>         |                             |

|            |        | EEM     |                        |                             |

|            | •      | MOVD    | B(Rs), A(Ri)           |                             |

|            |        | LEM     | <b>a</b> t <b>a</b>    |                             |

|            |        | MOV     | Ri, Rs                 |                             |

|            |        | MUL     | #5, Rs                 |                             |

|            |        | EEM     |                        |                             |

|            |        | FMUL    | C(Rs), A(Ri)           |                             |

|            |        | LEM     |                        |                             |

| 1          | P5:    | A(1, j) | -A(i,j) + B(i,k)       |                             |

| •          | . a' . |         |                        | * (*/)                      |

|            |        | MOV     | Ri, Rs                 | •                           |

|            |        | MUL     | #bul, Rs               | •                           |

|            |        | ADD     | Rk, Rs                 | /index for B(i,k) computed  |

|            |        | EEM     |                        |                             |

|            |        | MOVD    | B(Rs), - (SP)          |                             |

|            |        | LEM     | •                      |                             |

|            |        | NOM     | Rk, Rs                 |                             |

|            |        | MUL     | #cul, Rs               |                             |

|            |        | ADD     | Rj, Rs                 | /index for C(k, j) computed |

|            |        | EEM     |                        | •                           |

|            |        | FMUL    | $C(\mathbf{Rs}),$ (SP) |                             |

|            |        |         |                        |                             |

î. L

# APPENDIX C

## MODE CODING EXAMPLES

P5: Cont.

/

| LEM  |                |                |     |        |          |

|------|----------------|----------------|-----|--------|----------|

| MOV  | Ri, Rs         |                |     |        |          |

| MUL  | #aul, Rs       |                |     |        |          |

| ADD  | Rj, R <b>s</b> | /ind <b>ex</b> | for | A(i,j) | computed |

| EEM  |                |                |     |        |          |

| FADD | (SP) +, A(Rs)  |                |     |        |          |

| LEM  |                |                |     |        |          |

#

# MULTIPLY, LIVIE CPACE COLNG EXAMPLES

| P1:       | A 🔫        | - 3 <b>*C</b>    |                                   |

|-----------|------------|------------------|-----------------------------------|

|           | MOVD       | $B_{\mu} - (SP)$ | /move B to the stack              |

|           | FMUL       | C, (SP)          | /multiply C with top of the stack |

|           | MOVD       | (SP) +, A        | /move result to A                 |

| <b>~?</b> |            |                  |                                   |

| P2:       | A <b>4</b> | -(B+C) * (D+E)   | •                                 |

|           | MOVD       | B,-(SP)          |                                   |

|           | FADD       | C, (SP)          |                                   |

|           | MOVD       | D,-(SP)          |                                   |

|           | FADD       | E, (SP)          |                                   |

|           | FMUL       | (SF)+, (SP)      |                                   |

|           | MOVD       | (SP)+,A          |                                   |

| P3:       | A(i,       | -B(i) * C(i)     |                                   |

|           | MOVD       | B(Ri), - (SP)    |                                   |

|           | FMUL       | C(Ri), (SP)      |                                   |

|           | MOVD       | (SP)+,A(Ri)      |                                   |

| P4:       | A(i)       | -B(i#3) + C(i#5) |                                   |

|           | MOV        | Ri, R <b>s</b>   |                                   |

|           | ADD        | #3, Rs           | /index i+3 in Rs                  |

|           | MOVD       | B(Rs), $-(SP)$   |                                   |

|           | MOV        | Ri, -(SP)        |                                   |

|           | IMUL       | #5, (SP)         |                                   |

|           | MCV        | (SP)+, Rs        | /index i*5 in Rs                  |

|           | FMUL       | C(Rs), (SP)      |                                   |

|           | MOVD       | (SP)+, A(Ri)     |                                   |

| P5:       | A(i,j)     | -A(i,j) + B(i,k) | * C(k,j)                          |

|           | MOV        | Ri, - (SP)       |                                   |

|           | IMUL       | #bul, (SP)       |                                   |

|           | MOV        | (SP)+, Rs        |                                   |

|           | ADD        | Rk, Rs           | /index for B(i,k) computed        |

|           | MOVD       | B(Rs) = (SP)     |                                   |

|           | MOV        | Rk, - (SP)       |                                   |

|           | IMUL       | #cul, (SP)       |                                   |

|           | MOV        | (SP)+, Rs        |                                   |

|           | ADD        | Rj, Ps           | /index for C(k,j) computed        |

|           | FMUL       | C(Ps), (SP)      |                                   |

|           | MOV        | Ri, - (SP)       |                                   |

|           | IMUL       | #aul, (SP)       |                                   |

|           | MOV        | (SP)+,Rs         |                                   |

|           | ADD        | Rj, R <b>s</b>   | /index for A(i,j) computed        |

|           | FADD       | A(Rs), (SP)      |                                   |

|           | CVOM       | (SP)+, A(Rs)     |                                   |