# MAGNETIC TAPE CONTROL 516 INSTRUCTION MANUAL VOLUME 1

COPY NO.

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

Copyright 1965 by Digital Equipment Corporation

# CONTENTS

| Chapter |                                 | Page |

|---------|---------------------------------|------|

| 1       | INTRODUCTION                    | 1-1  |

|         | Purpose and Scope               | 1-1  |

|         | Manual Organization             | 1-1  |

| _       | Figures                         | 1-1  |

|         | Use of Manual                   | 1-2  |

|         | System Application              | 1-2  |

|         | Programmed Operations           | 1-4  |

|         | CONI Instruction                | 1-4  |

|         | CONO Instruction                | 1 -4 |

|         | Command Repertoire              | 1-5  |

|         | Parity                          | 1-7  |

|         | Priority Interrupt              | 1-7  |

|         | Tape Format                     | 1-7  |

|         | Tape Write and Read Signal Flow | 1-10 |

|         | Write Path                      | 1-11 |

|         | Read Path                       | 1-12 |

|         | System Data                     | 1-12 |

|         | Reference Conventions           | 1-16 |

|         | Reference Documents             | 1-17 |

| 2       | TAPE CONTROL INPUTS AND OUTPUTS | 2-1  |

|         | Processor                       | 2-1  |

|         | Clear Signals                   | 2-1  |

|         | CONO Signals                    | 2-1  |

|         | CONI Signals                    | 2-2  |

|         | Priority Interrupt              | 2-2  |

|         | Data Control 136                | 2-3  |

|         | Output Signals                  | 2-4  |

|         | Input Signals                   | 2-4  |

|         | Transport Interface             | 2-5  |

| Chapter |                                           | Page |

|---------|-------------------------------------------|------|

| 3       | COMMAND LOGIC                             | 3-1  |

|         | Command Sync Quad-Flop                    | 3-1  |

|         | Quad-Flop Structure                       | 3-2  |

|         | Basic Quad-Flop Cycle                     | 3-2  |

|         | Quad-Flop Continue Cycle                  | 3-5  |

|         | Command Hold Buffer                       | 3-6  |

|         | Command Buffer                            | 3-7  |

|         | Command Decoding                          | 3-8  |

|         | Output Command Levels                     | 3-10 |

|         | Illegal Commands                          | 3-11 |

|         | Continue Logic                            | 3-11 |

| 4       | TAPE STATUS LOGIC                         | 4-1  |

|         | Tape Status Quint-Flop                    | 4-1  |

|         | Quint-Flop Structure                      | 4-1  |

|         | Basic Quint-Flop Cycle - First Command    | 4-1  |

|         | REW Command Cycle                         | 4-4  |

|         | Second Command — CON(0)                   | 4-6  |

|         | Second Command — $CON(1)\Lambda$ SEF      | 4-7  |

|         | Space to End of File Command — CON(1)∧SEF | 4-10 |

|         | Motion Delay Logic                        | 4-11 |

|         | Triggering                                | 4-12 |

|         | Output Pulses                             | 4-12 |

|         | Delays                                    | 4-12 |

| 5       | WRITE LOGIC                               | 5-1  |

|         | Function of Write Logic                   | 5-1  |

|         | Clock Circuitry                           | 5-1  |

| Chapter  |                                     | Page         |

|----------|-------------------------------------|--------------|

| 5 (cont) | WRT Command Character Timing        | 5-2          |

|          | WP Write Pulse                      | 5-2          |

|          | TK/GV LT Data Request Command Pulse | 5 <b>-</b> 3 |

|          | Synchronizing Circuit               | 5-3          |

|          | Write-Data Outputs                  | 5-4          |

|          | WRT and RDC                         | 5-4          |

|          | WRF                                 | 5-5          |

| •        | End of Record Write Delay           | 5-6          |

|          | Triggering of EWD                   | 5-6          |

|          | Outputs of EWD                      | 5 <b>-</b> 7 |

|          | Write Commands                      | 5-7          |

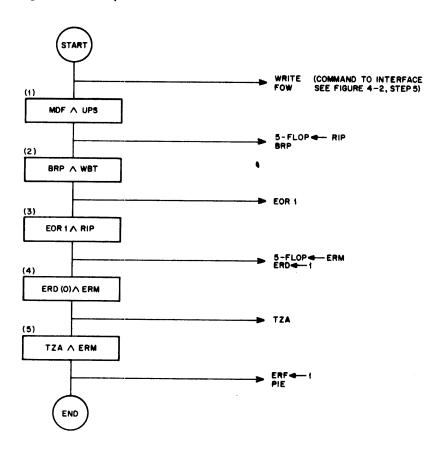

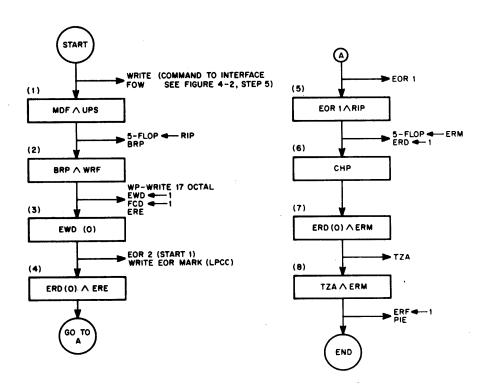

|          | Write Blank Tape (Figure 5–1)       | 5-8          |

|          | Write File (Figure 5-2)             | 5-9          |

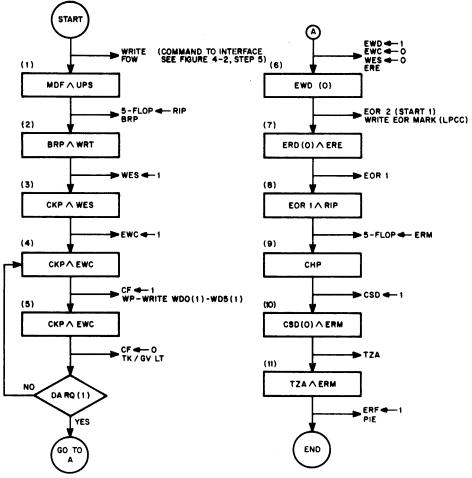

|          | Write (Figure 5-3)                  | 5-10         |

| 6        | READ LOGIC                          | 6-1          |

|          | Function of Read Logic              | 6-1          |

|          | Input Levels                        | 6-1          |

|          | Lateral Parity                      | 6-2          |

|          | Character Sensing                   | 6-3          |

|          | MISS Character Detection            | 6-3          |

|          | Read Comparison                     | 6-4          |

|          | End of Record                       | 6-5          |

|          | EOR 1 Pulse                         | 6-5          |

|          | End of Record Delay and ERE Level   | 6-6          |

|          | Longitudinal Parity                 | 6-6          |

|          | End of File                         | 6-7          |

|          | Second Character Detection          | 6 <b>-</b> 7 |

|          | EFF Set and Reset                   | 6-7          |

| Chapter  | ·                                                | Page         |

|----------|--------------------------------------------------|--------------|

| 6 (cont) | Read Command and Space Forward Command           | 6-8          |

|          | Backward Read Command and Space Backward Command | 6-10         |

|          | Read Compare Command                             | 6-12         |

| 7        | TAPE CONTROL INTERFACE 520                       | <i>7</i> -1  |

|          | Selection and Command Inputs                     | 7 <b>-</b> 1 |

| •        | Write Logic                                      | 7-2          |

|          | Write Data Outputs                               | 7-2          |

|          | Write Parity Net                                 | 7-2          |

|          | Write Buffer                                     | <b>7-</b> 3  |

|          | Read Logic                                       | 7-4          |

|          | Read Buffer                                      | 7-4          |

|          | End-of-File Flag                                 | 7-6          |

|          | Read Parity Net                                  | 7-7          |

|          | Parity Error Flip-Flop                           | 7-7          |

| 8        | TAPE CONTROL INTERFACE 521                       | 8-1          |

|          | Selection and Command Inputs                     | 8-1          |

|          | Selection Inputs                                 | 8-1          |

|          | Command Inputs                                   | 8-1          |

|          | Other Control Functions                          | 8-2          |

|          | Pool                                             | 8-3          |

|          | T A/B Select                                     | 8-3          |

|          | Write Logic                                      | 8-4          |

|          | Write Data Outputs                               | 8-4          |

|          | Write Buffer                                     | 8-4          |

|          | Write Parity Net                                 | 8-4          |

|          | Write Reset Flip-Flop                            | 8-5          |

|          | Read Logic                                       | 8-6          |

|          | Read Buffer                                      | 8-6          |

| Chapter |                                          | Page |

|---------|------------------------------------------|------|

| 8 (co   | nt) End-of-File Flag                     | 8-8  |

|         | Read Parity Net                          | 8-9  |

|         | Parity Error Flip-Flop                   | 8-9  |

| 9       | TAPE CONTROL INTERFACE 522A              | 9-1  |

|         | Command and Selection Inputs             | 9-1  |

|         | Selection Inputs                         | 9-1  |

|         | Command Inputs                           | 9-1  |

|         | Signals Between Interface and Transports | 9-3  |

|         | Converters                               | 9-3  |

|         | Motion Control Signals                   | 9-4  |

|         | Other Transport Control Signals          | 9-5  |

|         | Status Signals from Transports           | 9-6  |

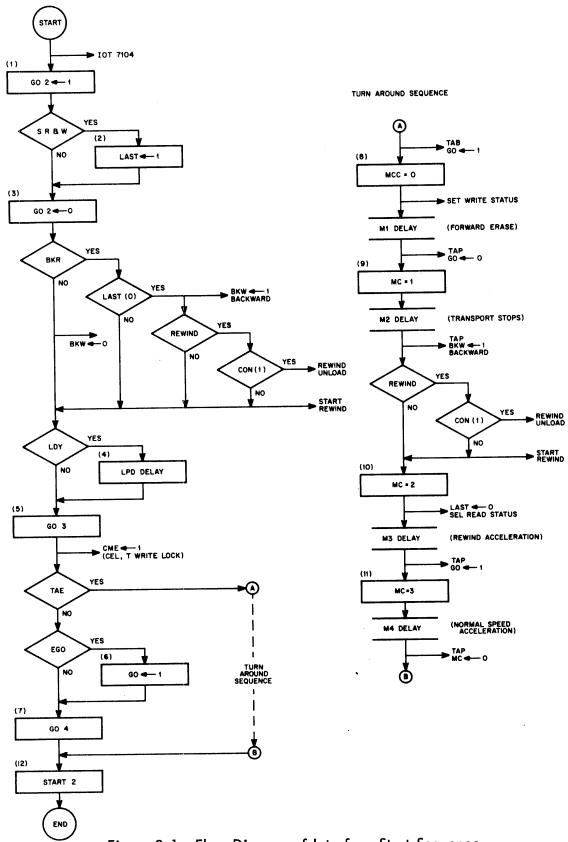

|         | Start Sequence                           | 9-7  |

|         | Set LAST                                 | 9-7  |

|         | Set or Reset BKW                         | 9-8  |

|         | Load Point Delay                         | 9-9  |

|         | Command Enable Last Level                | 9-9  |

|         | Normal Start                             | 9-9  |

|         | Turn Around Sequence                     | 9-10 |

|         | Write Logic                              | 9-12 |

|         | Write Data Outputs                       | 9-12 |

|         | Write Buffer                             | 9-13 |

|         | Write Parity Net                         | 9-13 |

|         | Write Reset Flip-Flop                    | 9-14 |

|         | Write Pulse Generation                   | 9-15 |

|         | Write Echo                               | 9-15 |

|         | Read Logic                               | 9-16 |

|         | Read Buffer                              | 9-16 |

|         |                                          |      |

| Chapter  |                                                       | <u>Page</u> |

|----------|-------------------------------------------------------|-------------|

| 9 (cont) | End-of-File Flag                                      | 9-18        |

|          | Read Parity Net                                       | 9-19        |

|          | Parity Error Flip-Flop                                | 9-19        |

| 10       | MAINTENANCE                                           | 10-1        |

|          | General                                               | 10-1        |

|          | Use of Drawings                                       | 10-1        |

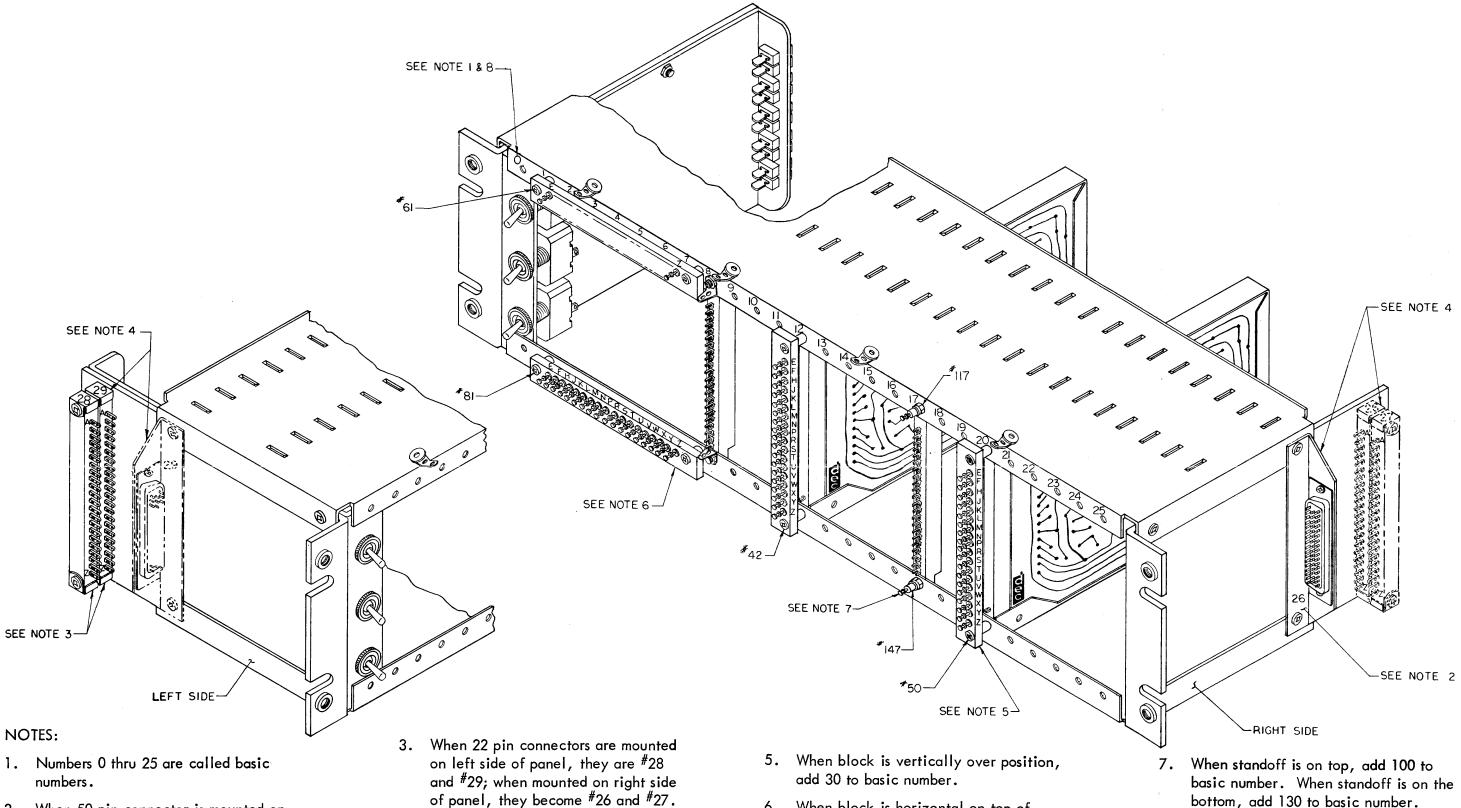

|          | Equipment Layout                                      | 10-2        |

|          | Preventive Maintenance                                | 10-2        |

|          | Adjustment and Calibration                            | 10-2        |

|          | Crystal Clocks                                        | 10-5        |

|          | MOD Delays                                            | 10-6        |

|          | Other Tape Control Delays                             | 10-7        |

|          | Delays in Interface 522A                              | 10-7        |

|          | Programming Suggestions                               | 10-9        |

|          | Successive CONO 220 Commands                          | 10-9        |

|          | Writing Past Tape End Point                           | 10-9        |

|          | Leaving Rewinding Transports Unselected               | 10-9        |

|          | Programmed JNU Pulse                                  | 10-10       |

|          | Programmed CHP Pulse                                  | 10-11       |

|          | Maintenance Programs                                  | 10-11       |

|          | Cursory Operation Test for Type 516 Tape Control      | 10-11       |

|          | Dynamic Status Presentation for Type 516 Tape Control | 10-11       |

|          | PDP-6 Magnetic Tape Data Test 516                     | 10-12       |

|          | Recommended Spare Parts                               | 10-14       |

|          | Module Spares                                         | 10-14       |

|          | Component Spares                                      | 10-16       |

|          | Mechanical Spares                                     | 10-17       |

| Chapter       |                                                                                     | Page |

|---------------|-------------------------------------------------------------------------------------|------|

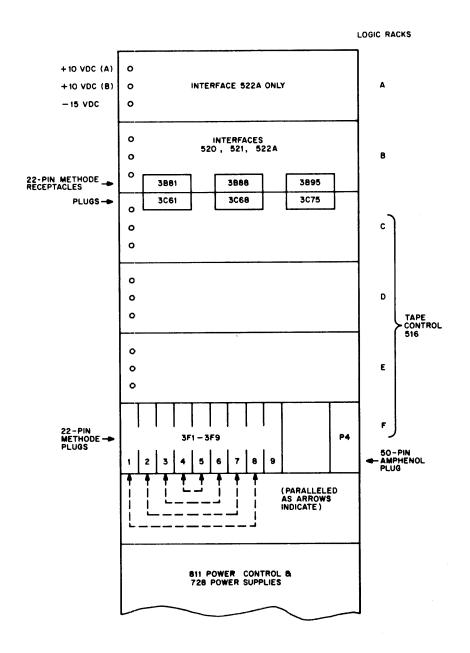

| 11            | INSTALLATION AND PREOPERATIONAL CHECK-OUT                                           | 11-1 |

|               | Site Selection                                                                      | 11-1 |

|               | Unpacking                                                                           | 11-1 |

|               | Inspection                                                                          | 11-3 |

|               | Cable Connections                                                                   | 11-4 |

|               | Power Controls                                                                      | 11-5 |

|               | Power Control Type 834-836                                                          | 11-5 |

|               | MCV Switches                                                                        | 11-5 |

|               | Preoperational Check-Out                                                            | 11-6 |

|               |                                                                                     |      |

|               |                                                                                     |      |

|               | ILLUSTRATIONS                                                                       |      |

| <u>Figure</u> |                                                                                     |      |

| 1-2           | Tape Systems Configurations                                                         | 1-3  |

| 1-3           | Tape Format                                                                         | 1-8  |

| 1-4           | Tape Write and Read Signal Flow                                                     | 1-1  |

| 3-1           | Command Sync Quad-Flop Basic                                                        | 3-2  |

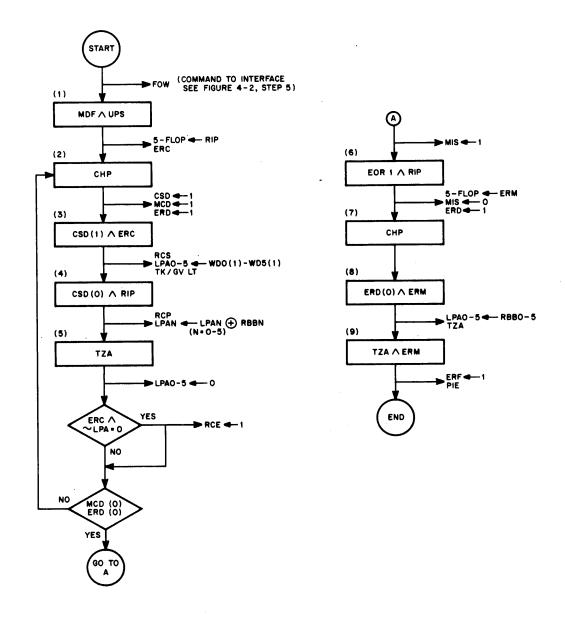

| 3-2           | Command and Status Logic Flow Diagram                                               | 3-3  |

| 4-1           | Tape Write and Read Signal Flow                                                     | 4-3  |

| 5-1           | Write Blank Tape — WBT                                                              | 5-8  |

| 5-2           | Write File – WRF                                                                    | 5-9  |

| 5-3           | Write - WRT                                                                         | 5-11 |

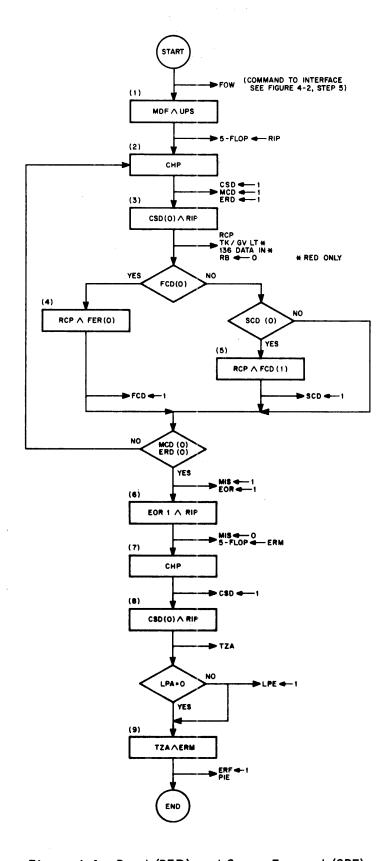

| 6-1           | Read (RED) and Space Forward (SPF)                                                  | 6-9  |

| 6-2           | Backward Read (BER) and Space Forward (SPF)                                         | 6-11 |

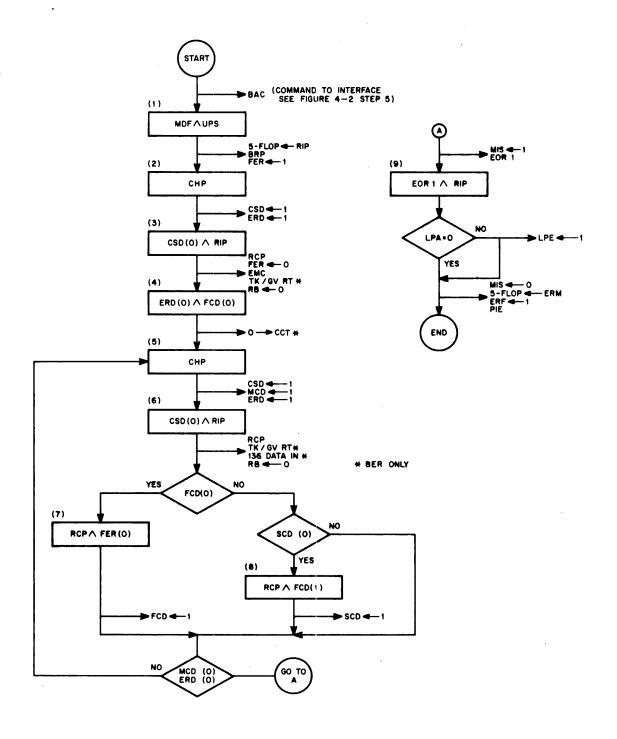

| 6-3           | Read Compare (RDC)                                                                  | 6-13 |

| 9-1           | Flow Diagram of Interface Start Sequence (Including Turn Around Sequence When Used) | 9-2  |

| 10-1          | Digital Cable and Component Numbering                                               | 10-3 |

| 11-1          | Front View Layout, Tape Control 516 and Interface 520, 521, or 522A                 | 11-2 |

# TABLES

| Table |                                              | Page |

|-------|----------------------------------------------|------|

| 1-1   | System Operating Specifications              | 1-12 |

| 1-2   | Physical Characteristics                     | 1-14 |

| 1-3   | Power Requirements                           | 1-15 |

| 2-1   | Priority Interrupt Conditions                | 2-3  |

| 2-2   | Signals from Transport Interface             | 2-6  |

| 2-3   | Signals to Transport Interface               | 2-6  |

| 3-1   | CB Register Bit Assignment                   | 3-8  |

| 3-2   | Command Decoding                             | 3-9  |

| 3-3   | Command Sequences That Require Continue Mode | 3-12 |

| 4-1   | Motion Delay Logic                           | 4-14 |

| 9-1   | Converter Module Inputs and Outputs          | 9-4  |

| 10-1  | Crystal Clock Frequency and Period           | 10-5 |

| 10-2  | Tape Control Delay Time Constants            | 10-8 |

| 10-3  | Interface 522A Delay Time Constants          | 10-9 |

| 11-1  | Cable Connections, Methode Plugs 3F1-3F9     | 11-4 |

#### CHAPTER 1

#### INTRODUCTION

# PURPOSE AND SCOPE

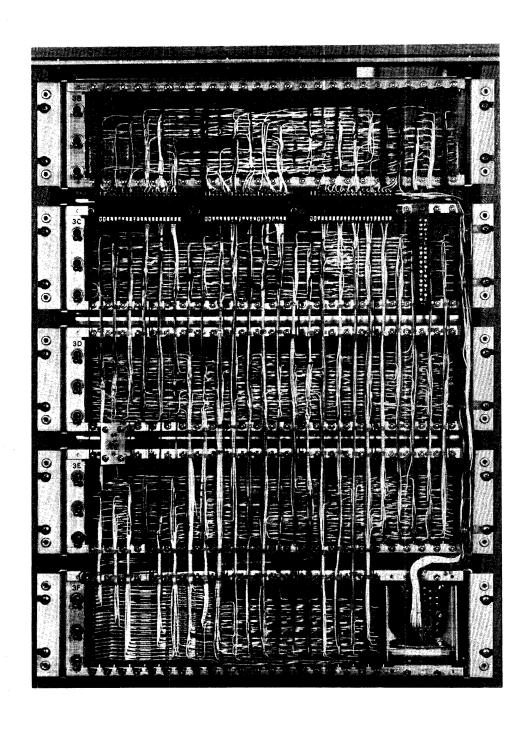

The purpose of this instruction manual is to aid personnel in the installation, operation, and maintenance of the DEC Magnetic Tape Control 516 and the associated Interface Unit Type 520, 521, or 522A (Figure 1-1).

# MANUAL ORGANIZATION

Volume I presents a brief description of the system application and specifications in Chapter 1, Introduction. Chapter 2, Tape Control Inputs and Outputs, explains the principal signals exchanged between the tape control and the adjacent units of the PDP-6 system. The next four chapters, Chapters 3 through 6, contain the theory of operation of the tape control logic itself. Chapters 7 through 9 describe the theory of operation for the three types of interface unit that may be used with the tape control, the 520, 521, and 522A, respectively. Chapter 10, Maintenance, contains information useful for inspection, troubleshooting, and repair. Chapter 11, Installation, explains the procedures to be followed when first unpacking and installing the tape control and interface.

Volume II presents complete signal glossary lists in Chapter 12 for the Type 516 Tape Control, and Types 520, 521, and 522A Tape Control Interface Units. Chapter 13 contains introductory information on DEC drawing conventions and all pertinent engineering drawings for this manual.

## **Figures**

This manual includes four general classes of figures: engineering logic drawings; flow diagrams; circuit schematics; and miscellaneous figures such as photographs, block diagrams, and logic rack layout diagrams. The complete system logic for the tape control is shown in the engineering logic diagrams referenced in Chapter 3 and contained in Volume II. The interface logic is shown in the engineering logic diagrams referenced in Chapters 7, 8, and 9. Flow

Figure 1–1 Magnetic Tape Control Type 516 and Tape Control Interface Type 521

diagrams of the various system operations are presented in text with Chapters 3 through 6. Circuit schematics and logic rack layout diagrams are contained in Chapter 13.

At the date of issue of this manual, up-to-date engineering drawings are included in Chapter 13. However, in time engineering changes do occur, thus if any discrepency exists between the engineering drawings of this manual and a current set of engineering drawings, the current engineering drawing set is correct.

All engineering logic drawings in Chapter 13 are arranged numerically for quick reference. Furthermore, all circuit schematics of Chapter 13 are arranged in order of circuit type designation (e.g., Negative Diode Module 4114 precedes Diode Module 4115).

#### USE OF MANUAL

This manual is intended to serve two purposes: instruction and reference. Chapters 2 through 9 on theory of operation are intended primarily for instruction. These chapters cover the major logical networks and operating sequences of the system in a systematic and detailed manner, but they are not organized for rapid reference. After being read, they rarely need be referred to again.

Once they have been thoroughly understood, the engineering logic drawings and the flow diagrams provide the fastest and most extensive source of reference data. After a reasonable learning period a competent maintenance engineer can orient logic function with particular drawings and even the approximate area of the drawing which shows given sections of the logic.

The flow diagrams add a time dimension to the logic drawings by providing sequential summaries of the specific operations performed during each type of command. Further reference data is provided in Chapter 12, which contains signal glossaries for the tape control and the three interface units.

#### SYSTEM APPLICATION

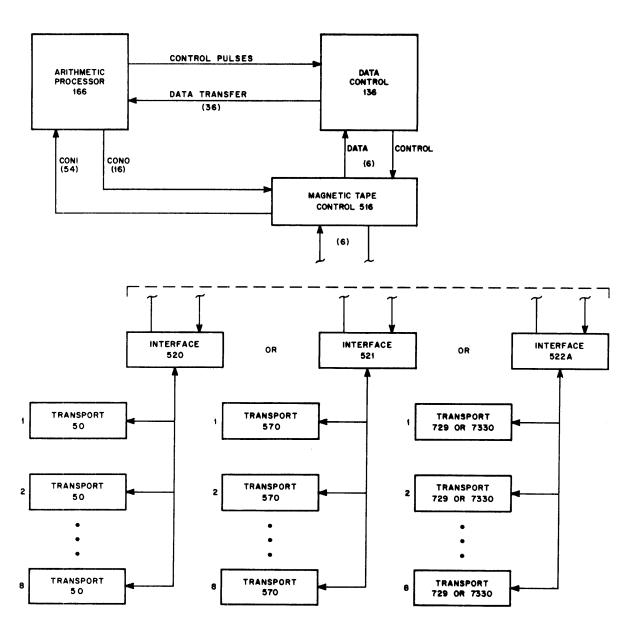

The magnetic tape system provides computer input-output at much faster data rates than most other peripheral devices. It is frequently used as high-capacity storage to augment core memory. Figure 1-2 is a block diagram showing typical tape system configurations. A given system

uses one of three types of interface units; the choice depends on the type of tape transport to be driven. Up to eight transports can be used by each interface-control combination. During both output and input operations, the Magnetic Tape Control 516 receives control information from the processor and generates appropriate signals to cause the interface and selected transport to correctly execute the programmed command.

Figure 1-2 Tape Systems Configurations

For output, 36-bit computer words are transferred from the PDP-6 processor to the Data Control 136. The data control, through six sequential shifts out of the high-order end of its

accumulator, sends the six 6-bit characters (converted from each computer word) to the tape control to be written on tape. The tape control applies the output data characters to the write logic of the selected tape transport via the transport interface.

For input, the sequence is reversed. Data read from the tape in 6-bit characters is sent to the data control via the interface and the tape control. The data control shifts the data into its accumulator until six characters have been assembled into a 36-bit computer word (the end of the accumulator chosen and the direction of the shift depend upon the direction of tape motion, i.e., upon whether the command is read or backward read). The data control then transfers the full 36-bit word into the processor.

## PROGRAMMED OPERATIONS

Both CONI and CONO tape control instructions may be addressed to the Magnetic Tape Control 516.

## **CONI** Instruction

The processor samples 54 tape control status bits by means of CONI instructions. Three separate device selection addresses are provided; each samples 18 status bits. This permits tape control and transport status information to be sampled directly from the processor control console.

## CONO Instruction

The processor sends 16 bits of control information to the tape control at each CONO 220 tape control instruction. (The tape control also receives CONO 224 and CONO 230 instructions for more specialized functions described later in this chapter under Parity and Priority Interrupt.) The functions controlled by this information include:

- 1. the choice of the command to be executed (read, write, write file, etc.)

- 2. the selection of the tape transport that is to carry out the command

- 3. whether or not the selected transport is to be kept reserved after completing the command

- 4. the parity mode (binary or BCD)

- 5. the density at which data is to be written on tape (200, 556, or 800 bits per inch)

- 6. the slice level at which data is to be read from tape

- 7. whether or not end of record gaps are to be ignored

- 8. the priority interrupt channel to be assigned to the tape control.

The functions determined by the 12 more significant CONO 220 bits are listed in Table 3-1 (CB Register Bit Assignment). The remaining four CONO bits are never transferred into the CB register, but they make up two of the control fields listed above. Bit 32 is the maintenance bit; when programmed to be a 1, it causes the tape control to ignore the record gap and treat the entire tape as a single record. Bits 33-35 assign the tape control priority interrupt channel.

# Command Repertoire

By suitably coded CONO 220 instructions, the processor can cause the Magnetic Tape Control 516 to execute any of the following ten commands.

and stops.

Rewind

The selected transport rewinds the tape to load point

Rewind Unload

Rewinds the tape off the takeup reel of the selected transport.

Write

Writes N words of six characters each (from consecutive or nonconsecutive memory locations) into one tape record. A lateral parity bit (binary or BCD) is generated for each character written. All characters are read and checked for parity after writing. At the end of the record, an EOR gap is spaced out, and an EOR mark (longitudinal parity check character) is written.

Write End of File

Writes an end-of-file record consisting of an end-of-file character (17 octal, BCD) followed by an EOR mark. The tape control does this automatically without use of the Data Control 136.

Write Blank Tape

Writes about 3 inches of blank tape and stops. The Data Control 136 is not used.

Read Compare

Reads a full record from tape and compares it character by character with output data from the processor memory. Any discrepancy sets the RCE flag. (The EOR mark that follows the tape record is not compared.)

Read

Reads one complete record from tape. Each character is shifted into the low-order end of the data accumumulator in the Data Control 136 for assembly into 36-bit computer words and transferred into the PDP-6 processor. Although the tape control always reads a full record, the processor can be programmed to read in any lesser amount of data.

Read Backward

Identical to read except for the direction of tape motion.

Because data is shifted into the high-order end of the data control accumulator, the ordering of characters within each 6-character computer word is the same as for read. The word order is, of course, still inverted.

Space Forward

All spacing is done without the use of the Data Control 136. To space forward one record, the tape control reads the record, but does not apply the resulting data to the data control. If a 1 is programmed in bit 24, the space forward command is iterated until a file mark record is reached.

Space Backward

To space backward one record, the tape control executes a backward read but does not apply the resulting data to the data control. If a 1 is programmed in bit 24, the space backward command is iterated until a file mark record is reached.

#### **Parity**

Both lateral and longitudinal parity are checked during all commands except rewind and read compare. Separate error flags are provided for the two types of parity error. The PER flag indicates lateral parity errors, and the LPE flag indicates longitudinal parity errors. Longitudinal parity is always even; lateral parity can be programmed to be odd or even (binary or BCD).

# Priority Interrupt

Seven priority interrupt channels are available. See Chapter 2, Priority Interrupt, for a description of interrupt conditions.

# TAPE FORMAT

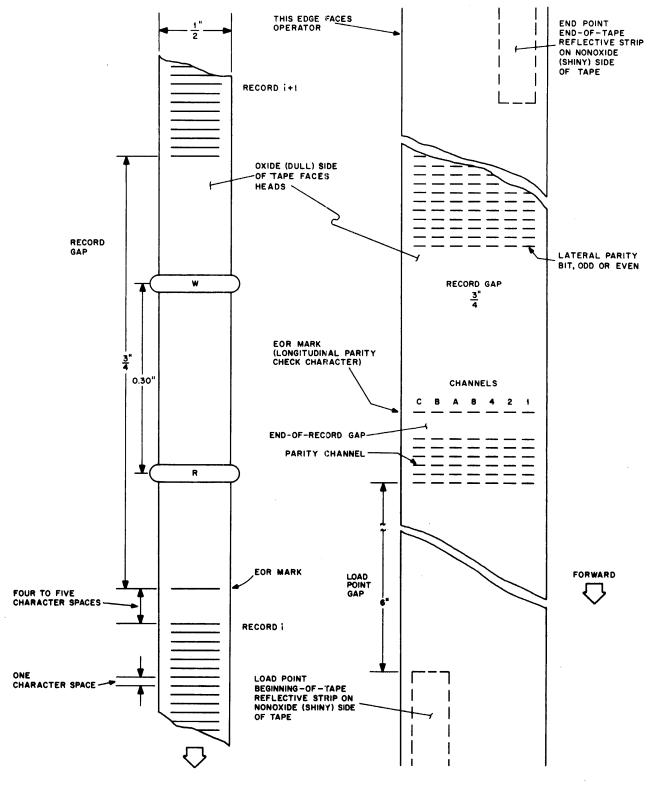

All transports driven by the Magnetic Tape Control 516 use 1/2-inch tape containing seven information channels. The tape format is shown in Figure 1-3. The left portion of the figure shows the tape in relation to the read and write heads. The tape moves by the heads vertically—forward direction being downward. The tape is composed of a mylar base coated on one side with an iron oxide composition. The oxide or dull side of the tape faces the heads, with the left edge toward the transport drive plate. The recording density may be either 200, 556, or 800 characters per inch. Tape speed varies depending upon the type of transport used.

The method of recording used is nonreturn-to-zero (NRZI). Although the tape has two basic states of remnant magnetization, the remaining magnetic state of the tape at a given bit position does not determine the value of that bit. A logical 1 is represented by a change from one state of magnetization to the other, in either direction. A logical 0 is represented by a constant state of magnetization. Therefore, to write a series of characters containing all 0s

Figure 1-3 Tape Format

is equivalent to writing a section of blank tape. Each time a character is transferred into the write buffer, the NRZI writers produce an equivalent character on the tape. However, because of NRZI method of recording, a transfer into the write buffer is not a normal 1 transfer. Instead, whenever a 1 bit is to be written in a given tape channel, the corresponding flipflop of the write buffer is complemented, producing a change in tape magnetization. When a 0 is to be written, the corresponding bit of the write buffer remains in its initial state, and there is no change in tape magnetization.

The structure and relative spacing of the individual tape characters is shown in the right portion of Figure 1-3. Each 36-bit computer word is divided into six 6-bit characters. However, the write buffer contains seven flip-flops WBO-6 corresponding to the seven tape channels. The seventh channel (WB6) is the parity channel. A lateral parity bit is generated for each 6-bit data character and written into the parity channel. WBO writes the most significant data bit; WB5, the least significant. The parity of the character may be either odd (binary) or even (BCD) as specified by the program. In reading the tape, only 1s are detected.

The smallest unit of information that can be written on the tape is a record. Since each computer word contains six 6-bit characters, a record normally contains 6N data characters, where N is the number of words that the processor BLKO (or DATAO) instructions transfer out to the Data Control 136. After the last data character of the record is written, the tape control writes slightly over four character spaces of blank tape (the EOR gap), and clears the write buffer to produce an end-of-record character, the EOR mark. The bit configuration of the EOR mark produced by the write buffer clear leaves an even number of 1 bits in each of the seven channels of the tape (all bits of the write buffer start in the 0 state, and to end in the 0 state they must undergo an even number of transitions). For this reason, the EOR mark is sometimes referred to as the longitudinal parity check character.

This does not mean, however, that the entire record must be deposited in computer memory. Although the tape control always reads the entire record and always sends every data character to the data control accumulator (unless the Data Control 136 is disconnected), the processor need not read in the full record. The processor accepts 6N data characters, where N is the number of words that the processor BLKI (or DATAI) instructions request from the Data Control 136.

After the processor has accepted the last word of input data from the data control data buffer, the data control advances one more word from the data accumulator to the data buffer. All additional characters are then shifted into the data accumulator. These characters, with the exception of the final six characters of the record, are shifted out the end of the accumulator and lost.

The distance that the EOR mark moves beyond the read head, before the tape is stopped, added to the acceleration distance which the tape moves before writing is allowed, produces a section of blank tape between records. This section of blank tape is called a record gap; it is approximately 3/4 inch long. The EOR character always moves slightly further beyond the heads in writing than in reading. This is an added precaution to prevent the generation of inter-record "gap-trash" which might otherwise be produced by failing to erase the entire record gap when writing on previously recorded tape. As long as the erase heads are functioning properly, the precaution is unnecessary. (Since the direction of tape magnetization changes only when 1s are written on tape, the absence of write output data during a write command erases the tape, that is, writes blank tape with a uniform state of magnetization.)

Besides detecting changes in magnetization through the read heads, the tape transports also include a photoelectric system for sensing the beginning and end of the tape (TLP — tape load point, and TEP — tape end point).

The load point and end point of the tape are marked by reflective strips mounted on the side of the tape away from the heads. These strips are detected by photodiodes which sense light reflected from them. In writing on a newly mounted or rewound tape, a gap of about 6 inches is left from the load point before writing can begin.

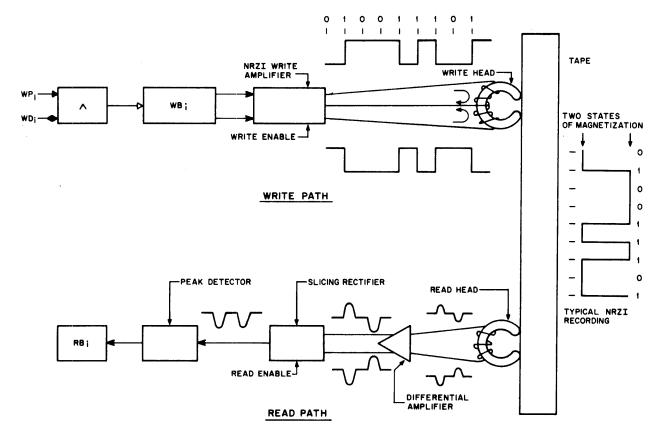

## TAPE WRITE AND READ SIGNAL FLOW

Figure 1-4 is a simplified block diagram of the tape system write and read paths for a single channel. The actual circuit modules used, and the distribution of these modules between the tape transport and the transport interface, varies depending on the choice of interface and transport. (Refer to the appropriate interface chapter for a description of the specific circuits used with a given transport-interface combination.)

Figure 1-4 Tape Write and Read Signal Flow

#### Write Path

The write path is shown at the top of the figure. The WB<sub>i</sub> flip-flop is complemented at each WP pulse that occurs while the WD<sub>i</sub> level is asserted. Both outputs of the WB<sub>i</sub> flip-flop are connected (through various drivers not shown in the figure) to an NRZI write amplifier. When gated by a write enable signal, this write amplifier drives one of two oppositely wound coils at the write head. The choice depends on the state of the WB<sub>i</sub> flip-flop. If the write enable level is not present, no current flows through either coil.

Whenever a 1 is to be written on tape, WD; causes the WB; flip-flop to be complemented at the WP pulse. The transition of WB; terminates the current through one coil and starts it in the other, changing the direction of tape magnetization and writing a 1 on the tape. As long as WB; remains in the same state, current continues to flow through one side of the coil, and 0s are written on the tape. (The tape is then magnetized in the same direction over a series of character spaces.)

#### Read Path

The read path is shown at the bottom of Figure 1-4. The tape reaches the read head shortly after traversing the write head. As long as the direction of tape magnetization remains constant, no current flows through the read head coil. Each change in the direction of tape magnetization induces a current in the read head. The read current produced by two consecutive tape 1s is shown in the waveforms near the read head.

These signals are applied to a differential read amplifier that provides considerable amplification for difference signals but only fractional amplification for common mode signals. The output of the read amplifier is then sent through a slicing rectifier. This circuit can produce an output only when the read enable level is present. This prevents read signals from being sent to the tape control when tape is in motion but not being read; for example, during the rewind operation. The rectifier produces an output pulse (of one polarity) for every input pulse of either polarity from the read amplifier. However, the rectifier input circuit, to prevent a low-level noise input from generating an unwarranted output pulse, requires a minimum threshold level.

The slicing rectifier output is applied to a peak detector. The peak detector produces a logic pulse output at the peak of the input pulse which, therefore, sets the read buffer flip-flop whenever a 1 is read from the tape.

#### SYSTEM DATA

System specifications and physical characteristics are listed in Tables 1-1 and 1-2, respectively.

TABLE 1-1 SYSTEM OPERATING SPECIFICATIONS

| Syste                                 | m Parameters                     |

|---------------------------------------|----------------------------------|

| Number of transports per tape control | 1-8                              |

| Recording method                      | NRZI                             |

| Characters                            | 7 bits: 6 data, 1 parity         |

| Parity                                |                                  |

| Lateral                               | Odd or even                      |

| Longitudinal                          | Even (data channels only)        |

| Density                               | 200, 556, or 800 characters/inch |

TABLE 1-1 SYSTEM OPERATING SPECIFICATIONS (continued)

| Maximum transfer rate (in characters/second)                                                                                        | <u>200</u>                    | <u>556</u>                  | 800                |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|--------------------|

| Interface 520, Transport                                                                                                            | 15 kc                         | 41.6 kc                     |                    |

| Interface 521, Transport 570 or<br>Interface 522A, Transport 729<br>(at 112.5 ips)<br>(at 75 ips)<br>Interface 522A, Transport 7330 | 22.5 kc<br>15 kc<br>7.2 kc    | 62.5 kc<br>41.6 kc<br>20 kc | 90 kc<br>60 kc<br> |

| Load point gap                                                                                                                      | 6 inches                      |                             |                    |

| Inter-record gap                                                                                                                    | 3/4 inch                      |                             |                    |

| EOR gap (longitudinal parity character spacing)                                                                                     | 4–5 character                 | spaces                      |                    |

| Error flags                                                                                                                         | Function                      |                             |                    |

| PER                                                                                                                                 | lateral parit                 | y error                     |                    |

| LPE                                                                                                                                 | longitudinal                  | parity error                |                    |

| RCE                                                                                                                                 | read compar                   | ison error                  |                    |

| ILC                                                                                                                                 | illegal comm                  | nand                        |                    |

| Priority interrupt; 7 channels available                                                                                            | Interrupt occ<br>illegal comn | curs at end of each         | record and at      |

| Status bits                                                                                                                         | 54 status bit<br>console      | s available for samp        | oling at PDP-6     |

| <u>Trans</u>                                                                                                                        | port Parameters               | •                           |                    |

| Read-write heads                                                                                                                    | 7 channel                     |                             |                    |

| Таре                                                                                                                                |                               |                             |                    |

| Material                                                                                                                            | 1.5 mil poly                  | ester                       |                    |

| Width                                                                                                                               | 1/2 inch                      |                             |                    |

| Length                                                                                                                              | 2400 feet                     |                             |                    |

| Reel diameter                                                                                                                       | 10-1/2 inch                   | es                          |                    |

| Data protection                                                                                                                     | Write enable                  | lockout ring                |                    |

TABLE 1-1 SYSTEM OPERATING SPECIFICATIONS (continued)

| Tape Position Indications            |             |                      |                 |          |

|--------------------------------------|-------------|----------------------|-----------------|----------|

| Load point and end point detection   | Photoe      | lectric              |                 |          |

| Full reel and low reel               | Mechai      | nical (Used only     | for Transport T | ype 50.) |

| Meaning of Position Indications      |             |                      |                 |          |

| Load point                           | 10 feet     | from physical b      | eginning of tap | е        |

| End point                            | 14 feet     | from physical e      | nd of tape      |          |

| Full reel                            | Less the    | an 100 feet on to    | akeup reel      |          |

| Low reel                             | Less the    | an 100 feet on su    | upply reel      |          |

| Transport Type                       | <u>, 50</u> | <u>570</u>           | 729             | 7330     |

| Multicontrol operation               | no          | yes                  | no              | no       |

| Slice levels available               | 1           | 2                    | 2               | 2        |

| Tape speed (inches/second)           | 75          | <i>7</i> 5+<br>112.5 | 75+<br>112.5    | 36       |

| Maximum rewind speed (inches/second) | 225         | 450                  | 550             | 220      |

| Rewind time full reel (seconds)      | 400         | <90                  | <90             | 1330     |

TABLE 1-2 PHYSICAL CHARACTERISTICS

# Construction

One standard, all-steel construction DEC cabinet.

| Magnetic Tape Control 516 | Four racks |  |

|---------------------------|------------|--|

| Interface 520             | One rack   |  |

| Interface 521             | One rack   |  |

| Interface 522A            | Two racks  |  |

Standard DEC system plug-in units, series 100 and 4000.

TABLE 1-2 PHYSICAL CHARACTERISTICS (continued)

## Power Equipment

For

Use

Mangetic Tape Control 516, and any interface

Power Control Type 834-836 and two

Magnetic Tape Control 516, Data

728 Power Supplies

Control 136, and Interface 520 or 521

Power Control Type 834-836 and two

Magnetic Tape Control 516, Data Control 136, and Interface 522A

728 Power Supplies

Power Control Type 834-836 and two

728 Power Supplies

#### Logic

Solid state. Transistors and crystal diodes utilizing static logic levels (0 vdc and -3 vdc).

|                           | Dimensions    |  |

|---------------------------|---------------|--|

| Height                    | 69-1/2 inches |  |

| Width                     | 22-1/4 inches |  |

| Depth                     | 27-1/8 inches |  |

| Clearance, front doors    | 8-3/4 inches  |  |

| Clearance, rear doors     | 14-7/8 inches |  |

|                           | Weight (lbs)  |  |

| Magnetic Tape Control 516 | 120           |  |

| Interface 520 or 521      | 20            |  |

| Interface 522A            | 40            |  |

| Cabinet                   | 160           |  |

#### TABLE 1-3 POWER REQUIREMENTS

#### Line Voltage Input

105 to 125 volts, 60 cycle, single phase

Power plug - Hubble Twist-Loc 3-prong, 30 ampere, 250 volt

TABLE 1-3 POWER REQUIREMENTS (continued)

|                           | Current Consumption |                |

|---------------------------|---------------------|----------------|

|                           | Surge Amperes       | Normal Amperes |

| Magnetic Tape Control 516 | 6                   | 4              |

| Interface 520 or 521      | 1.5                 | 1              |

| Interface 522A            | 3                   | 2              |

|                           | Power Consumption   |                |

|                           | <u>Watts</u>        |                |

| Magnetic Tape Control 516 | 460                 |                |

| Interface 520 or 521      | 115                 |                |

| Interface 522A            | 230                 |                |

|                           | Heat Dissipation    |                |

|                           | Btu/Hour            |                |

| Magnetic Tape Control 516 | 1560                |                |

| Interface 520 or 521      | 392                 |                |

| Interface 522A            | <b>7</b> 85         |                |

# REFERENCE CONVENTIONS

The Digital Equipment Corporation engineering drawing conventions and instruction manual referencing should be understood at this point. A study of the material contained in Chapter 13 and the following paragraphs before proceeding with detailed descriptions will save considerable reference time and preserve thought continuity when reading the text that follows.

Any reference to an illustration by a chapter-oriented figure number indicates that the figure is to be found in text following the reference. Any reference to an engineering drawing number indicates that the drawing is to be found in a special drawing section or chapter. All engineering drawings are referenced first by the full drawing number.

Example: BS-D-516-0-CM

To locate a specific signal or function on a drawing, a system of coordinates is used. As shown on the drawings of Chapter 13, coordinates are designated by a number and letter. Thus, in any drawing reference, coordinate location appears immediately after the number separated by a colon.

Example: BS-D-516-0-CM:D1

To avoid needless repetition of the full drawing number, in-text references can use a short designation form that includes only the difference modifier(s) of the drawing designation plus the coordinates.

Example: -CM:D1

One last text reference convention must be noted. Occasionally it is desirable to indicate the condition of a circuit within a logic description. As shown on the drawings of Chapter 13, circuit locations are identified. For reference in text, this designation is noted; for example, CB24. If the condition of the circuit is to be stated the reference becomes either CB24(1) or CB24(0).

The signal glossaries of Chapter 12 also are an important adjunct to both the text and drawings. These glossaries can be used in a cross indexing manner so that any signal and the conditions that generate it can be easily and completely referenced.

#### REFERENCE DOCUMENTS

Systems Modules Catalog, C-100

by Digital Equipment Corp.

FLIP CHIP Modules Catalog, C-105

by Digital Equipment Corp.

#### CHAPTER 2

#### TAPE CONTROL INPUTS AND OUTPUTS

#### **PROCESSOR**

Signals between the processor and the Magnetic Tape Control 516 fall into four major categories: clear signals; signals required for the CONO command; signals required for the CONI command; and priority interrupt request signals.

#### Clear Signals

The IOB RESET pulse (see BS-D-516-0-CM:D1) is an ungated clear pulse which is applied to all I/O devices and control units when computer power goes on, or when the operator presses the I/O reset key on the computer console. The program may also generate this reset. The IOB RESET is amplified and sent on to the transport interfaces as POWER CLEAR.

Within the tape control, the IOB RESET clears the command hold buffer, and resets the command sync quad-flop and the tape status quint-flop. It also generates two additional clear pulses MCL and CCB which complete the tape control clear operation. These two clear pulses are also applied to the transport interface (with the new designations STATUS CLEAR and 0 —> CM). The tape control engineering drawings show one additional clear signal called INT CLR. This pulse is not used at present.

# CONO Signals

The processor CONO (conditions-out) instruction produces an IOB CONO CLR pulse followed 1 µsec later by an IOB CONO SET pulse (BS-D-516-0-CM:A1). These two command pulses are effective only at the I/O device or control unit specified by the CONO instruction device selection code. Although the tape control may occasionally receive CONO 224 and CONO 230 instructions for certain specialized functions (described in Chapter 10), these instructions are exceptions; nearly all tape control CONO instructions use device selection code 220.

When gated by the SEL (Select Tape Control 516) level, which is only asserted when IOS3-9 represent 220 octal (BS-D-516-0-CM:C1), the IOB CONO CLR pulse generates a CLR pulse which clears the command hold buffer CHB20-35. The IOB CONO SET pulse, when gated by the SEL level, transfers the CONO control information into the command hold buffer CHB20-35.

## CONI Signals

The processor CONI (conditions-in) instruction produces an IOB STATUS level. This level is effective only at the I/O device or control unit specified by the CONI instruction device selection code. The IOB STATUS level places status information from the selected device or control unit on the I/O bus for 2.5 µsec. The processor reads the information from the bus into its arithmetic register at the 2-µsec point.

Each of the three device addresses assigned to the tape control, SEL (220 octal), SLT (224 octal), and SCS (230 octal) gates 18 status bits onto the bus (see BS-D-516-0-ST for the specific gating control of the 54 status bits). For maintenance purposes, the most relevant tape control and tape transport status information can be monitored directly at the processor console.

# Priority Interrupt

The processor can assign a priority-interrupt request channel to the tape control by means of a CONO instruction which sets CHB33-35 to some octal number from 1 to 7. If all three bits are 0, no priority interrupt channel is assigned. By asserting the PIE level (BS-D-516-0-CM:A8), the tape control can request a priority interrupt break on the assigned channel. The PI request is sent to the processor by grounding the appropriate PIR (priority interrupt request) line. The lower the channel number, the higher the priority. Breaks on channel 1 take precedence over all other breaks. Breaks on channel 2 take precedence over all breaks except those on channel 1, etc.

The conditions under which the PIE level is asserted are themselves subject to program control. There are four flip-flop switches which determine which of four possible priority interrupt conditions is to be allowed to assert the PIE level (see BS-D-516-0-MD:C6-7). Every CONO 224 instruction sets the four priority interrupt enable switches EFE, LIE, ICE and XNE to the states determined by bits 33, 20, 35, and 21, respectively, of the CONO 224 instruction.

When a given switch flip-flop is set to 1, the corresponding interrupt condition is gated through to assert PIE; when the switch is left in the 0 state, the input condition is not allowed to produce a PIE.

The four priority interrupt conditions that can be enabled to generate PIE are ERF(1), LIF(1), ICR, and XNC. The ERF(1) condition is asserted when the end of record flag is set; this is perhaps the most frequently used interrupt condition. The LIF(1) condition is asserted when the load point interrupt flag is set; this interrupt condition is used primarily during rewind commands. The ICR condition indicates that the interface and control are ready. The XNC condition represents the transfer new command state of the command sync quad-flop (see Chapter 3, Command Sync Quad-Flop). This condition indicates that the tape control is free to accept another CONO 220 command. The XNC interrupt condition is particularly useful during space-to-end-of-file commands when use of the ERE interrupt would be inconvenient. The four interrupt conditions that produce the PIE level are summarized in Table 2-1.

TABLE 2-1 PRIORITY INTERRUPT CONDITIONS

| CONO 224<br>Bit No. | Sets<br>Switch | Permitting Interrupt Condition to Assert PIE |

|---------------------|----------------|----------------------------------------------|

| 33                  | EFE            | End of Record Interrupt ERF(1)               |

| 20                  | LIE            | Load Point Interrupt LIF(1)                  |

| 35                  | ICE            | Interface and Control Ready ICR              |

| 21                  | XNE            | Transfer New Command Interrupt XNC           |

#### DATA CONTROL 136

The signals between the Data Control 136 and the Mangetic Tape Control 516 pertain to either output (write) operations, or input (read) operations. For any operation in which the data control selects the tape control, the SEL 3 level causes the DCS flip-flop (BS-D-516-0-MD:B7) to be set at BRP.

# Output Signals

During RDC (read compare) and WRT (write) commands, the data control applies the contents of its six high-order accumulator bits DA0-5 to the tape control via the output levels DA0(1)-DA5(1). Negative levels represent 1s in the corresponding accumulator bit positions. Although contents of the six high-order accumulator bits are always present at the tape control input terminals (BS-D-516-0-RD:C1-4), the tape control only samples these outputs during the WRT and RDC commands.

The tape control sends TK/GV LT (take or give character shift left) command pulses to the Data Control 136 during RDC and WRT commands (and also during the input command RED). These command pulses synchronize data control operations to the timing requirements of the tape control and the transports. At the receipt of each TK/GV LT pulse, the data control shifts the contents of its accumulator six bit positions left. This shift advances the next 6-bit output character into position to be sampled by the tape control.

Each character requires a single TK/GV LT pulse; no pulses are required for EOR marks. For all three commands during which the tape control sends TK/GV LT command pulses to the data control, the pulse produces certain common effects in the data control logic. At the arrival of the TK/GV LT, the data accumulator is shifted left by six bit positions, and the data control character counter is incremented by 1.

# Input Signals

During RED, SPF, BER, SPB, and RDC commands (see signal glossary), the transport interface applies the contents of its read buffer register RB to the tape control via the input data levels RBBO(1)-RBB5(1) (BS-D-516-0-RD:B2-5). Negative levels represent 1s in the corresponding read buffer bit positions. The RBB input data is read into the Data Control 136 only during the two commands RED (read) and BER (backward read). If the RED or BER command is in BCD (even) parity mode, the Hollerith code 0 character (12 octal) is converted to 00 octal before being applied to the data control (BS-D-516-0-RD:C1-3).

For the RED command only, the tape control strobes each input data character into the six low-order bits of the data control accumulator with a TK/GV LT pulse. On receiving each TK/GV LT,

the data control shifts its accumulator left six bits to make room for the input character and simultaneously strobes the character into the six low-order accumulator bits DA30-35. As in the case of the RDC and WRT output commands, the data control increments its character counter at each TK/GV LT.

For the BER command only, the tape control strobes each input character into the six high-order bits of the data control accumulator with a TK/GV RT pulse. On receiving each TK/GV RT, the data control shifts its previous accumulator contents right six bits to make room for the input character and simultaneously strobes the character into the six high-order accumulator bits DA0-5. The data control also increments its character counter at each TK/GV RT.

The BER command involves one complication not present with the RED command. When executing a RED command, the EOR gap provides a convenient means of sensing the end of the data record, and the EOR mark is not read as data. However, for the BER command, the EOR mark is read first, then the EOR gap, and finally the data record. Therefore, the EOR mark initially looks like data and it is strobed into the data control by the associated TK/GV RT pulse. The tape control must prevent the data control from treating the EOR mark as a valid data character. It does this by following the EOR mark TK/GV RT with a 0 —> CCT pulse. This pulse clears the data control character counter and causes the EOR mark to be shifted out and eliminated.

#### TRANSPORT INTERFACE

For ready reference, signals from the transport interface are listed in Table 2-2, and signals to the transport interface are listed in Table 2-3. The signals between the tape control and transport interface can be better understood if learned in context as encountered in the subsequent chapters of the manual.

TABLE 2-2 SIGNALS FROM TRANSPORT INTERFACE

| Signal Name           |                                           | Function                                                                                               |  |

|-----------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| START 2               |                                           | Steps 5-flop from TCR to UPS or MOS. (Called STM within the tape control.)                             |  |

| ВСТ                   |                                           | Selected transport reserved by other tape control. (Interface 521 only.)                               |  |

| RDY                   |                                           | Transport ready to receive new command.                                                                |  |

| TEP                   |                                           | Tape at end point.                                                                                     |  |

| TLP                   |                                           | Tape at load point.                                                                                    |  |

| TWL                   |                                           | Tape write enable lockout ring out. A data-<br>protection condition that disables write cir-<br>cuits. |  |

| RBCP                  |                                           | Read buffer character present (RBO-5 $\neq$ 0).                                                        |  |

| RBEF                  |                                           | Read buffer end of file. Senses end-of-file character (RBO-5 = 17 octal).                              |  |

| TRPE                  |                                           | Tape read parity error. Lateral parity error detected for character just read.                         |  |

| 1                     | TABLE 2-3 SIGN                            | NALS TO TRANSPORT INTERFACE                                                                            |  |

| Output Signal<br>Name | Signal Name<br>Inside Tape<br>Control 516 | Function                                                                                               |  |

|                       |                                           | Clear Pulses                                                                                           |  |

| POWER CLEAR           | IOB RESET                                 | I/O bus reset (initial ungated clear pulse).                                                           |  |

|                       | 1461                                      | Motion clear; occurs at beginning of each command.                                                     |  |

| STATUS CLEAR          | MCL                                       |                                                                                                        |  |

TABLE 2-3 SIGNALS TO TRANSPORT INTERFACE (continued)

| Output Signal<br>Name    | Signal Name<br>Inside Tape <sup>-</sup><br>Control 516 | Function                |  |  |

|--------------------------|--------------------------------------------------------|-------------------------|--|--|

|                          | Cor                                                    | nmand Levels            |  |  |

| WRITE                    |                                                        |                         |  |  |

| FOW                      | _                                                      | Forward command.        |  |  |

| BAC                      | _                                                      | Backward command.       |  |  |

| REW                      | -                                                      | Rewind command.         |  |  |

| WEF                      | -                                                      | WRF or WBT command.     |  |  |

| NOP                      | -                                                      | No operation.           |  |  |

|                          | Con                                                    | atrol Pulses            |  |  |

| IOT 7104                 | СТТ                                                    | Start pulse.            |  |  |

| $AC1 \longrightarrow UN$ | JNU                                                    | Unit selected.          |  |  |

| MP                       | MDF                                                    | Motion pulse.           |  |  |

| WP                       | WCP                                                    | Write pulse.            |  |  |

| START 1                  | EOR 2                                                  | Write EOR mark.         |  |  |

| 0 <del>&gt;</del> RB     | -                                                      | Clear read buffer.      |  |  |

| $1 \longrightarrow EFF$  | <del>-</del>                                           | Set end of file flag.   |  |  |

| 0 → EFF                  | _                                                      | Reset end of file flag. |  |  |

### CHAPTER 3

## COMMAND LOGIC

The command logic accepts control information from the PDP-6 processor, decodes the information, and applies the resulting command signals to the transport interface. The command logic is composed of two buffer registers, a 4-state control device (the command sync quad-flop), and a set of decoding networks which process the control information in the buffer register and generate appropriate command levels for transmission to the selected tape transport.

During the CONO tape control instruction, the 16 low-order bits of the CONO effective address are transferred out from the processor to the command hold buffer CHB (BS-D-516-0-CM). Four of these control bits remain in CHB. The remaining twelve control bits are not decoded in CHB; before being decoded these bits are advanced into the command buffer CB. The advance of these twelve bits from CHB into CB takes place in two successive stages. First four selection bits are transferred to CB to select (and, if necessary, reserve) a transport; second, when the selected transport indicates that it is ready for the command, the other eight control bits are also transferred into CB. From CB, the control bits are applied to the decoding networks. The command decoding networks convert the processor control fields into the command levels required at the transport interface.

The primary function of the command sync quad-flop is to control the timing of these control information transfers, and at their completion, to start the selected tape transport.

# COMMAND SYNC QUAD-FLOP

The command sync quad-flop (BS-D-516-0-CS:C6-8) controls the advance of information from CHB to CB by initiating the JNU pulse and the JNC pulse. The JNU pulse causes the selection of a single transport; JNC applies the command levels of the current instruction to that transport via the transport interface. After the command levels have been applied to the transport, the quad-flop causes the generation of a CTT pulse (-CS:B5) and the selected transport to begin the command.

### **Quad-Flop Structure**

The command sync quad-flop is composed of four 3-input negative diode NOR gates (3E19, 20, 25). The inputs to each of these four gates are taken from the outputs of the remaining three gates. The result of this arrangement is that the quad-flop functions as a 4-state flip-flop. It remains stable in any one of its four states; the active output is at ground, and the three quiescent outputs are negative logic levels.

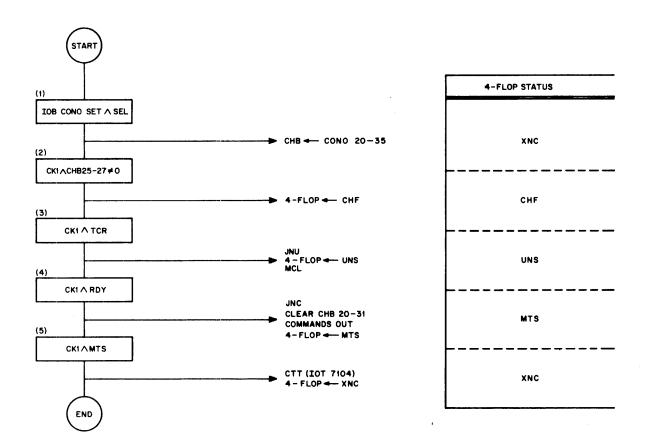

# Basic Quad-Flop Cycle

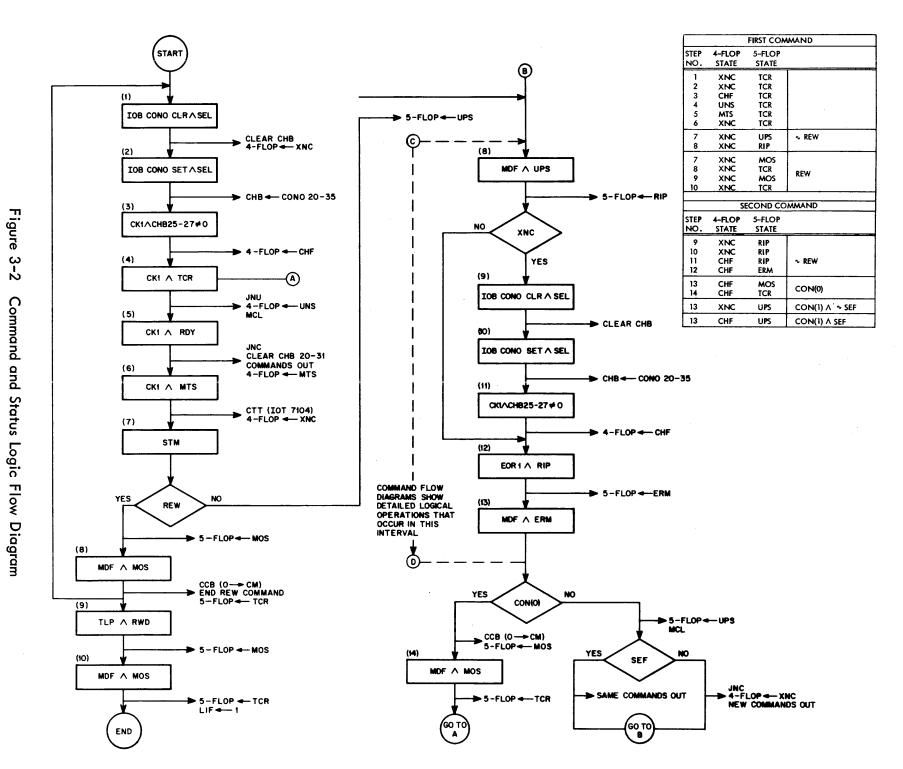

The basic cycle of the command sync quad-flop is shown in Figure 3-1. The basic cycle operations are also shown in steps 1 through 6 of the more detailed command and status logic flow diagram, Figure 3-2. Steps 11 through 13 of the figure show variations from the basic quad-flop cycle which arise during the execution of successive commands in continue mode (CON = 1). These variations are described under Quad-Flop Continue Cycle later in this chapter.

Figure 3-1 Command Sync Quad-Flop Basic Cycle

## **XNC** State

Because the quad-flop is reset to XNC state (Transfer New Command) by IOB RESET and IOB CONO CLR, the quad-flop begins each command in XNC. The quad-flop must be in XNC to advance to its second state CHF (Command Hold Full).

## **CHF** State

The IOB CONO SET pulse (Figure 3-1, step 1) loads the effective address of the current CONO instruction into the command hold buffer. Every tape command code has a 1 in at least one of the three bits 25-27, so CHB25-27 \neq 0 after the IOB CONO SET. Therefore, the first CK1 to occur after IOB CONO SET steps the quad-flop to the CHF state (Figure 3-1, step 2). The CHF state indicates that the command hold buffer is loaded with control information. The quad-flop must be in CHF to advance to its third state UNS (Unit Selected).

### **UNS State**

As soon as the tape control is ready to initiate a command (indicated by the TCR — Tape Control Ready — state of the tape status quint-flop and CNR(0); refer to Chapter 4, Tape Status Quint-Flop), the next CK1 pulse generates a JNU pulse, and steps the quad-flop from CHF to UNS (Figure 3-1, step 3). The quad-flop must be in UNS state to advance to its fourth state MTS (Magnetic Tape Start). The JNU pulse produces an MCL pulse which clears most of the tape control flip-flops. The JNU pulse also advances the device selection information as stated earlier from CHB28-31 to CB28-31. The contents of CB29-31 specify which of the available transports is to receive the current command. The CB28 bit determines whether that transport is to be kept in a reserved status after the completion of the command or is to be returned to the pool. The JNU pulse is sent to the 521 Interface units as AC1 —> UN.

### MTS State

When the selected transport is ready to execute the current command, it sends an RDY level to the tape control. This level enables the next CK1 pulse to generate a JNC pulse (Figure 3-1, step 4). The JNC pulse advances the contents of CHB20-27 into CB20-27. These eight control bits are decoded, and the resulting command levels are applied to the selected transport.

The JNC pulse clears CHB20-31 (once the control information is advanced to CB, it is no longer needed in CHB). The JNC pulse also steps the command sync quad-flop to its fourth and final state MTS.

## Reset to XNC

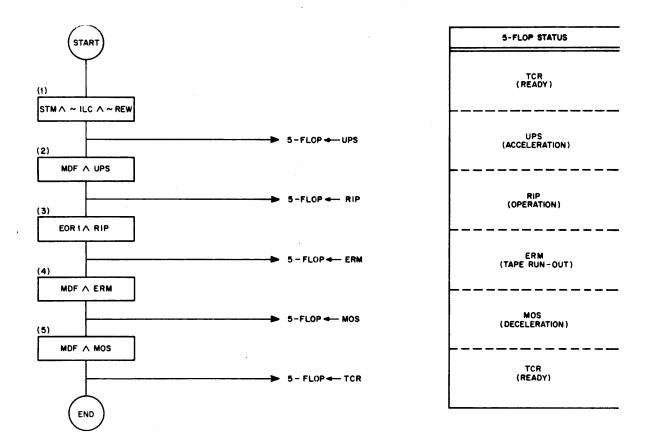

The CK1 pulse immediately following the CK1 that produced JNC (and applied the command levels to the selected transport) generates the CTT pulse (BS-D-516-0-CS:B8). This pulse resets the command sync quad-flop from MTS to XNC. The same pulse is sent to the transport interface as IOT 7104 and returns from the interface (sometimes delayed, depending on the type of interface used) as START 2. After it reenters the Magnetic Tape Control 516, it is called STM (BS-D-516-0-CS:B3).

The IOT 7104 pulse causes the transport to start tape motion. The STM pulse sets the tape status quint-flop to the UPS acceleration state (see Chapter 4, Tape Status Quint-Flop).

## Quad-Flop Continue Cycle

At any time after the command sync quad-flop is reset to XNC and the tape-status quint-flop has been stepped to UPS, a second CONO instruction can be sent to the tape control. This second instruction transfers new control information into CHB (which has been empty since the JNC pulse of the first instruction cycle). The next CK1 pulse can then advance the quad-flop to the CHF state (see Figure 3-2, step 11).

The first command continues to completion while the second command remains stored in CHB. The MDF pulse at the end of the ERM state of the first command (Figure 3-2, step 13) represents a branch point in the tape control cycle. At that MDF pulse, the tape control enters the continue mode if the CON flip-flop is in the 1 state. (Refer to Continue Logic, later in this chapter, for a more detailed description of the significance of the state of CON.)

If CON = 0, the second instruction does not call for continue mode, and the command sync quad-flop follows the same basic cycle as the first instruction. From CHF, it proceeds to UNS, MTS, and is reset to XNC. This sequence is represented by the left branch of the Figure 3-2 flow diagram (including the jump from step 14 to point A).

However, if CON = 1, indicating that the second instruction does call for continuous mode operation, the quad-flop cycle never advances to UNS or MTS. Instead, the quad-flop is reset directly from CHF to XNC (by the JNC pulse). This continue mode operating sequence is represented by the extreme right branch of the Figure 3-2 flow diagram. The basic quad-flop cycle is cut short during continue mode operations because: 1) no JNU pulse is required during continue mode — the second instruction always selects the same transport interface as the first instruction; and 2) no IOT 7104 pulse is sent to the selected transport — the transport is already moving in the required direction. Therefore, since both the JNU and IOT 7104 pulses are omitted during continue mode instructions, there is no need for the quad-flop to step through the UNS and MTS states; instead it can be reset directly from CHF to XNC (Figure 3-2, step 13, right branch). In continue mode, the MDF pulse that ends the tape-status quint-flop ERM state (Figure 3-2, step 13) also produces a JNC pulse. This JNC pulse resets the quad-flop from CHF to XNC state, clears CHB, and advances the new control information in CHB20-27 into CB20-27, thereby applying the new command levels to the transport interface.

Because certain transitions of the command sync quad-flop are conditioned upon the state of the tape-status quint-flop (the quint-flop TCR state is one of the input conditions governing the generation of JNU and JNC, see BS-D-516-0-CS:A3 and A6) the quad-flop cycle should not be considered in isolation; rather the quad-flop and the quint-flop are to be regarded as two interdependent elements of a single control system. The operation of the complete system is shown in Figure 3-2, and described in Chapter 4, Tape Status Quint-Flop.

### COMMAND HOLD BUFFER

The CHB (BS-D-516-0-CM) is a 16-bit buffer register which receives CONO control information from the I/O bus. During the CONO tape control instruction, the 16 low-order bits of the CONO effective address are loaded into CHB20-35. (Physically, the transfer occurs over conductors IOB2-17. This wiring method is chosen to equalize the loading on the two I/O bus cables. The control information entering CHB20-35 is taken from bits 20-35 of the CONO address; so the use of IOB2-17 instead of IOB20-35 has no logical significance.)

The entire CHB is cleared by the CLR pulse which occurs at IOB RESET, INT CLR, and IOB CONO CLR  $\Lambda$  SEL. The JNC pulse clears CHB20-21; i.e., all of the twelve CHB bits that

JNC advances into CB. The remaining four CHB bits CHB32-35 are not cleared by JNC, but only by CLR. Since IOB CONO CLR precedes IOB CONO SET by 1 µsec, the CHB is always ready for new control information at the arrival of the IOB CONO SET. That pulse loads the effective address of the current CONO instruction into CHB by means of a 1 transfer. The IOB CONO SET is gated through to the CHB capacitor-diode inputs only when the device selection code of the current CONO instruction specifies the tape control (220 octal). Decoder 3E3 (BS-D-516-0-CM:C1) then produces a SEL level. The IOB CONO CLR pulse is also gated by the SEL level.

The JNU pulse advances the contents of CHB28-31 into CB28-31. These four bits specify which of the available transports is to receive the current command and whether the selected transport is to be kept in a reserved status after the completion of the instruction or is to be returned to pool.

When the selected transport is ready to execute the current instruction, a JNC pulse is generated. This pulse advances the eight high-order CHB bits from CHB20-27 to CB20-27. Once in CB, these eight bits are decoded to produce the command levels required by the current instruction. The JNC pulse also clears CHB20-31.

The four low-order bits CHB32-35 are never advanced into CB. These four bits are used while they are in CHB. Bit CHB32 is the disable EOR 1 maintenance bit. Setting this bit to a 1 with a CONO instruction inhibits the ERE level and prevents the generation of EOR 1 pulses. When the EOR 1 pulses are disabled, the tape control treats the tape essentially as a single record. This permits the entire tape to be traversed with a single command. Bits CHB33-35 assign a priority interrupt channel to the tape control; for a description of the priority interrupt logic refer to Chapter 2, Priority Interrupt. Device address 220 samples CHB20-35 on IOB20-35.

# COMMAND BUFFER

The CB (BS-D-516-0-CM) is a 12-bit buffer register which receives CONO control information from the CHB at the JNU and JNC pulses. This information is decoded only from CB; it has no effect on the transport interface as long as it remains in CHB.

The CCB pulse (clear command buffer) clears CB. This pulse occurs at IOB RESET, INT CLR, and whenever the ILC flip-flop is set (indicating that the current command is illegal). For all noncontinuous commands except rewind, the CCB also occurs at the end of the ERM state of the tape status quint-flop (Figure 3-2, step 13, left branch). This occurrence of CCB terminates the application of the command levels to the transport interface. During the rewind command, the CCB terminates the command levels at the end of the quint-flop MOS state (step 8, REW). The UNU  $\Lambda$  SNU condition for generating CCB is relevant only at the transport interface.

The contents of CHB28-31 are first advanced into CB28-31 by JNU, and (at least one CK1 interval later) the JNC pulse advances CHB20-27 into CB20-27. The CB contains six data fields. The significance of these fields is indicated in Table 3-1.

TABLE 3-1 CB REGISTER BIT ASSIGNMENT

| Bits    | Function                                                                                                                                 |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CB20    | Governs slice level. Set to 1 for old tapes where more signal is required. (Not applicable to Interface 520.)                            |  |  |  |  |