EK-DEQNA-UG-001

# DEQNA ETHERNET User's Guide

EK-DEQNA-UG-001

# DEQNA ETHERNET User's Guide

Prepared by Educational Services of Digital Equipment Corporation © Digital Equipment Corporation 1984.

All Rights Reserved.

Printed in U.S.A.

NOTE: Multiple DEQNAs may not be configured in the same CPU cabinet. Such a configuration exceeds current Federal guidelines regarding emissions of RFI/EMI and thus cannot be either system integrated or warranted by Digital Equipment Corporation.

Customers may, at their discretion, order and upgrade their systems with multiple DEQNAs in the same CPU cabinet. However, if multiple DEQNAs are integrated by a customer, it is the customer's responsibility to conform to Federal FRI/EMI emission guidelines.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

The software described in this document is furnished under a license and may not be used or copied except in accordance with the terms of such license.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by Digital.

The following are trademarks of Digital Equipment Corporation:

| dígital™     | DIBOL        | RSX            |

|--------------|--------------|----------------|

| DEC          | MASSBUS      | TOPS-10        |

| DECmate      | PDP          | TOPS-20        |

| DECnet       | P/OS         | UNIBUS         |

| DECsystem-10 | Q-Bus        | VAX            |

| DECSYSTEM-20 | Professional | VMS            |

| DECUS        | Rainbow      | VT             |

| DECwriter    | RSTS         | Work Processor |

# CONTENTS

### CHAPTER 1 INTRODUCTION

| 1.1       | ETHERNET OVERVIEW                    |  |

|-----------|--------------------------------------|--|

| 1.1.1     | ETHERNET Layers                      |  |

| 1.1.1.1   | Data Encapsulation                   |  |

| 1.2       | DEQNA DESCRIPTION                    |  |

| 1.2.1     | Q-Bus DMA Transfer Controller (QDTC) |  |

| 1.2.2     | Receive FIFO                         |  |

| 1.2.3     | ETHERNET Protocol Processor (EPP)    |  |

| 1.2.4     | Encoder/Decoder (ED)                 |  |

| 1.3       | DEQNA SYSTEM OPERÁTION               |  |

| 1.3.1     | Port Registers                       |  |

| 1.3.2     | Host Communications Area             |  |

| 1.3.2.1   | Buffer Descriptor List (BDL)         |  |

| 1.3.3     | Initialization                       |  |

| 1.3.3.1   | Bootstrap                            |  |

| 1.3.3.2   | Receiver Enable                      |  |

| 1.3.3.3   | Interrupt Vector                     |  |

| 1.3.4     | Loopback                             |  |

| 1.3.4.1   | Set-Up Mode                          |  |

| 1.3.4.2   | Internal Loopback (ILOOP)            |  |

| 1.3.4.3   | External Loopback (ELOOP)            |  |

| 1.3.4.4   | Internal Extended Loopback (IELOOP)  |  |

| 1.3.5     | Sanity Timer                         |  |

| 1.3.6     | Transmit                             |  |

| 1.3.7     | Receive                              |  |

| 1.4       | Q-BUS INTERFACE                      |  |

| 1.4.1     | Slave Logic                          |  |

| 1.4.2     | Master Logic                         |  |

| 1.5       | DEQNA SPECIFICATIONS                 |  |

| 1.6       | RELATED DOCUMENTS                    |  |

| CHAPTER 2 | INSTALLATION                         |  |

| 2.1       | UNPACKING AND INSPECTION             |  |

|           |                                      |  |

| 2.1     | UNPACKING AND INSPECTION       |  |

|---------|--------------------------------|--|

| 2.2     | PREINSTALLATION VERIFICATION   |  |

| 2.2.1   | Host Boot/Diagnostic ROMs      |  |

| 2.2.2   | Backplane Requirements         |  |

| 2.2.3   | Bus Latency Constraints        |  |

| 2.2.4   | Loading Requirements           |  |

| 2.3     | PREPARATION                    |  |

| 2.3.1   | Backplane                      |  |

| 2.3.2   | M7504 Module                   |  |

| 2.3.2.1 | Device Address Assignment (W1) |  |

|         |                                |  |

# **CONTENTS (Cont)**

# Page

| 2.3.2.2<br>2.3.2.3 | Bus Request Holdoff Timer (W2)<br>Sanity Timer (W3) |      |

|--------------------|-----------------------------------------------------|------|

| 2.3.3              | Patch and Filter Panel Assembly                     |      |

| 2.4                | INSTALLATION                                        |      |

| 2.5                | TESTING                                             |      |

| 2.5.1              | Post-Installation Power Checks                      |      |

| 2.5.2              | Light-Emitting Diode (LED) Checks                   |      |

| 2.5.3              | Diagnostic Acceptance Procedure                     | 2-7  |

| CHAPTER 3          | SERVICE                                             |      |

| 3.1                | MAINTENANCE PHILOSOPHY                              |      |

| 3.2                | DIAGNOSTICS                                         | 3-1  |

| 3.2.1              | Extended Primary Bootstrap (EPB)                    | 3-1  |

| 3.2.2              | Citizenship Test (CQ)                               |      |

| 3.2.2.1            | Test Descriptions                                   |      |

| 3.2.2.2            | Test Results                                        |      |

| 3.2.3              | Field Functional Test                               |      |

| 3.2.3.1            | Configuration and Set-Up                            |      |

| 3.2.3.2            | Test Descriptions                                   |      |

| 3.2.3.3            | Operation                                           |      |

| 3.2.3.4            | Error Reporting                                     |      |

| 3.2.4              | DEQNA DEC/X11 Exerciser                             |      |

| 3.2.4.1            | Configuration and Set-Up                            |      |

| 3.2.4.2            | Commands                                            |      |

| 3.2.4.3            | Error Messages                                      |      |

| 3.3                | CORRECTIVE MAINTENANCE                              | 3-17 |

| CHAPTER 4          | PROGRAMMING                                         |      |

| 4.1                | OVERVIEW                                            | 4-1  |

| 4.2                | CONTROL AND STATUS TRANSFERS                        | 4-1  |

| 4.2.1              | Station Address Registers                           | 4-2  |

| 4.2.2              | BDL Starting Address Registers                      | 4-2  |

| 4.2.3              | Vector Address Register                             | 4-3  |

| 4.2.4              | Control and Status Register (CSR)                   |      |

| 4.3                | DMA TRANSFERS                                       | 4-6  |

| 4.3.1              | Buffer Descriptor List (BDL)                        | 4-6  |

| 4.3.2              | Buffer Descriptor                                   |      |

| 4.3.2.1            | Flags                                               |      |

| 4.3.2.2            | Address                                             |      |

| 4.3.2.3            | Address Descriptor Bits                             |      |

| 4.3.2.4            | Buffer Length (Word Count)                          |      |

| 4.3.2.5            | Status Words                                        |      |

| 4.3.3              | Set-Up Mode                                         |      |

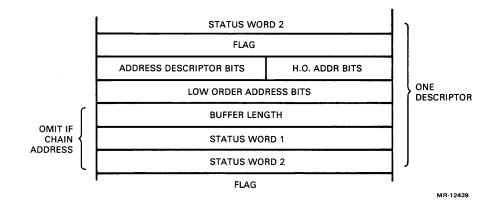

| 4.3.3.1            | Target Address Set-Up                               |      |

| 4.3.3.2            | Operating Condition Set-Up                          |      |

| 4.3.3.3            | Set-Up Packet                                       | 4-12 |

## APPENDIX A GLOSSARY

## APPENDIX B VECTOR AND I/O PAGE ADDRESS ASSIGNMENTS

## APPENDIX C NETWORK INTERCONNECT EXERCISER (NIE)

| C.1     | INTRODUCTION C-1                    |

|---------|-------------------------------------|

| C.2     | OPERATING MODES                     |

| C.2.1   | Unattended Mode C-1                 |

| C.2.1.1 | Build Node Table                    |

| C.2.1.2 | Direct Loop Message Test C-2        |

| C.2.1.3 | Pattern Test C-2                    |

| C.2.1.4 | Multiple Message Activity Test C-2  |

| C.2.2   | Operator Directed Mode C-2          |

| C.3     | SYSTEM REQUIREMENTS C-3             |

| C.4     | COMMAND DESCRIPTION                 |

| C.4.1   | DRS Commands C-3                    |

| C.4.1.1 | Switches C-4                        |

| C.4.1.2 | Flags                               |

| C.4.1.3 | Hardware and Software Questions C-6 |

| C.4.2   | NIE Commands C-6                    |

| C.5     | ERRORS C-13                         |

| C.5.1   | Error Messages                      |

| C.5.1.1 | General C-13                        |

| C.5.1.2 | Basic C-13                          |

| C.5.1.3 | Extended C-13                       |

| C.5.2   | Other Error Messages                |

# FIGURES

# Figure No.

#### Title

## Page

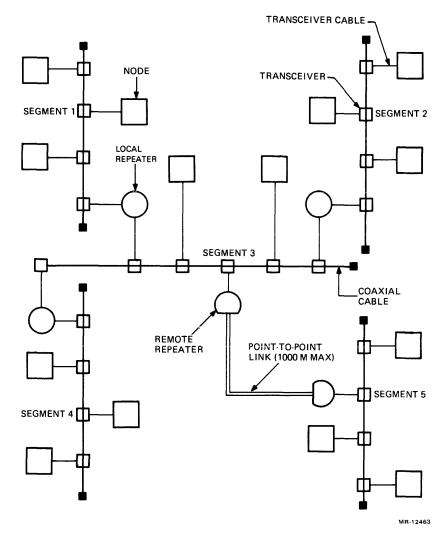

| 1-1 | Large-Scale ETHERNET Configuration                        | 1-2    |

|-----|-----------------------------------------------------------|--------|

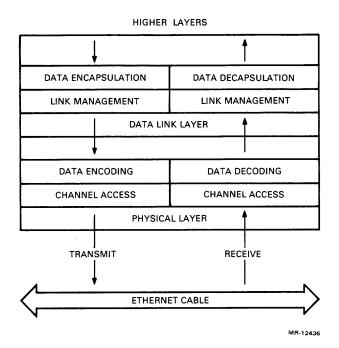

| 1-2 | ETHERNET Layer Functions                                  |        |

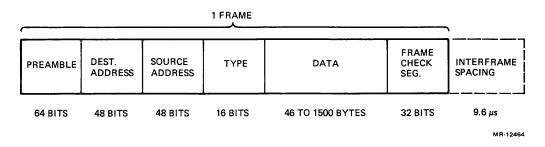

| 1-3 | ETHERNET Packet (Frame) Format                            |        |

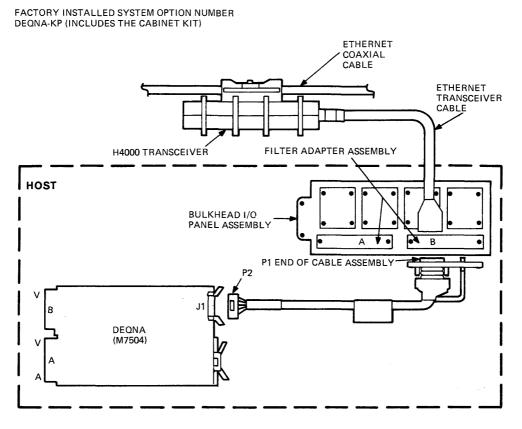

| 1-4 | DEQNA to ETHERNET Connection                              |        |

| 1-5 | DEQNA Major Functional Areas                              |        |

| 1-6 | BDL Format                                                |        |

| 2-1 | Patch and Filter Panel Assembly                           | 2-4    |

| 2-2 | M7054 Showing Jumpers, LEDs, Transceiver Cable Connector, |        |

|     | Station Address PROM, and Boot/Diag PROM                  | 2-5    |

| 3-1 | General Error Message Format                              |        |

| 3-2 | Typical Extended Error Message Format                     |        |

| 3-3 | DEQNA DEC/X11 Exerciser Error Message Format              |        |

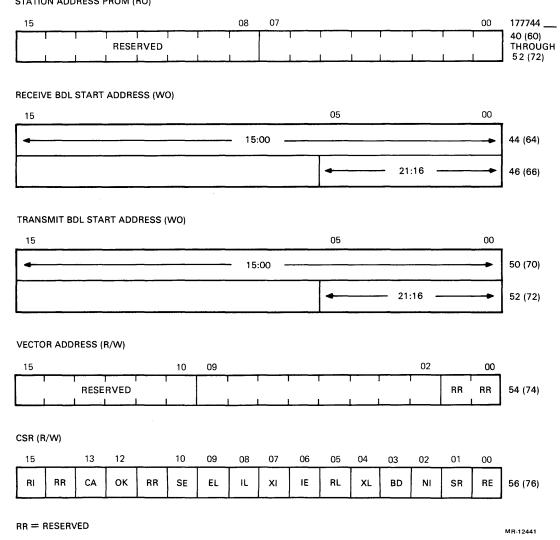

| 4-1 | Port Registers                                            | 4-2    |

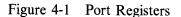

| 4-2 | BDL Format                                                | 4-6    |

| 4-3 | Target Address Set-Up                                     | . 4-11 |

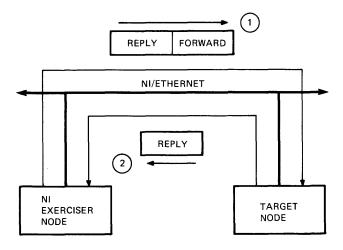

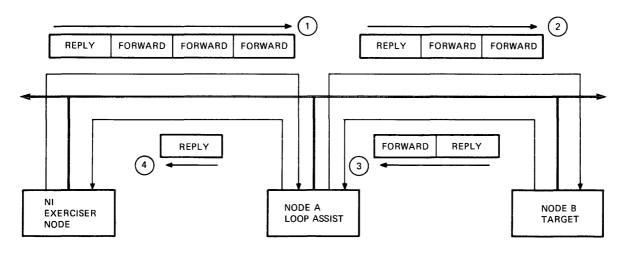

| C-1 | Loop Direct Message Test Path                             | C-10   |

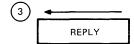

| C-2 | Transmit Assist Loopback Message Test Path                | C-10   |

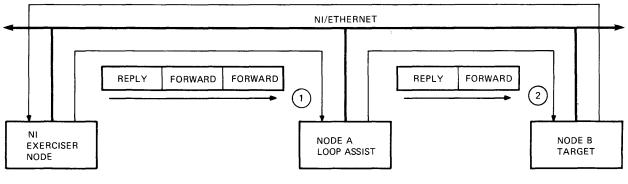

| C-3 | Receive Assist Loopback Message Test Path                 |        |

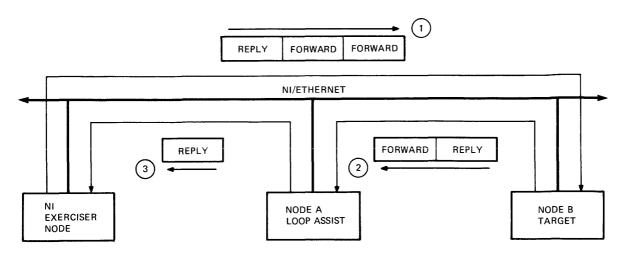

| C-4 | Full Assist Loopback Message Test Path                    |        |

# TABLES

| Table No. | Title                                          | Page |

|-----------|------------------------------------------------|------|

| 1-1       | DEQNA Specifications                           |      |

| 1-2       | Related Documents                              |      |

| 2-1       | DEQNA Parts List                               |      |

| 2-2       | DEQNA Q-Bus Loading                            |      |

| 2-3       | DEQNA Power Requirements                       |      |

| 2-4       | DEQNA Jumper Functions                         |      |

| 2-5       | DEQNA LED Indications                          |      |

| 3-1       | ZQNA Tested Functional Areas                   |      |

| 3-2       | Sanity Timer Time-Out Values                   |      |

| 3-3       | DEQNA DEC/X11 Exerciser Software Register Bits |      |

| 4-1       | Flag Word Bits 15 and 14                       |      |

| 4-2       | Valid and Chain Address Descriptor Bits        |      |

| 4-3       | Status Word 1 Bits 15 and 14                   |      |

| B-1       | Interrupt and Trap Vector Assignments          | B-1  |

| B-2       | I/O Page Addresses                             | B-2  |

| B-3       | Floating Vector Rank                           | B-3  |

| B-4       | Floating Address Rank                          | B-3  |

| C-1       | DRS Commands                                   | C-3  |

| C-2       | DRS Command Switches                           | C-4  |

| C-3       | Switch Application                             | C-4  |

| C-4       | DRS Command Flags                              | C-5  |

| C-5       | NIE Test Message Types                         | C-8  |

| C-6       | Node Pair Array                                |      |

# CHAPTER 1 INTRODUCTION

This chapter introduces the Digital ETHERNET Q-Bus Network Adapter (DEQNA), the M7504 module. The chapter includes an overview of the ETHERNET and a brief description of the DEQNA, its operation, and its specifications. The reader who wants more information about the ETHERNET may refer to a list of related documents in Table 1-2, and the ordering information contained in the last section of this chapter.

#### **1.1 ETHERNET OVERVIEW**

The ETHERNET is a network that supports high-speed data exchange among computers and other digital devices, within a limited geographic area. The branching bus topology of the ETHERNET provides a 10 Mbits/s (10 megabits per second) data rate over a coaxial cable at a distance of 2.8 kilometers (1.74 miles) or less. The ETHERNET is a local area network, with a higher data rate than low-speed networks, which carry data hundreds or thousands of kilometers, and a greater distance than very high-speed interconnects, which are usually limited to tens of meters.

The primary applications for the ETHERNET are office automation, distributed data processing, terminal access, and other applications which require an economical local medium for exchanging data at high peak-data rates. The major characteristics of the ETHERNET are as follows.

| Topology:        | Branching Bus                                                                            |

|------------------|------------------------------------------------------------------------------------------|

| Medium:          | Shielded coaxial cable. Manchester-encoded digital base-band signalling                  |

| Data Rate:       | 10 megabits per second                                                                   |

| Node Separation: | 2.8 kilometers (1.74 miles), maximum                                                     |

| Number of Nodes: | 1,024 maximum                                                                            |

| Network Control: | Multiaccess - fairly distributed to all nodes                                            |

| Access Control:  | Carrier Sense, Multiple Access with Collision Detect (CSMA/CD)                           |

| Allocation:      | 64- to 1518-byte packet length (includes variable length data field of 45 to 1500 bytes) |

As many as 1,024 nodes can be connected together in a local point-to-point/multipoint configuration with a single ETHERNET. Figure 1-1 is an example of a large-scale ETHERNET configuration. The ETHERNET configuration rules ensure the best network performance within physical channel limitations. The parameters for a maximum ETHERNET configuration are the following.

- 1. A cable segment is a coaxial cable terminated in its characteristic impedance at both ends. The maximum length of a segment is 500 meters (1640.5 feet).

- 2. Up to 100 nodes can be connected to any segment of the cable. The minimum distance between nodes on a cable segment is 2.5 meters (8.2 feet).

- 3. Repeaters connect segments to extend the cable. Repeaters do not have to be connected at the ends of a segment; they can occupy any node position; however, there can be no more than two repeaters in the path between any two nodes. Repeaters are included in the maximum node count.

- 4. The maximum length of coaxial cable between any two nodes is 1500 meters (4921.5 feet).

- 5. The maximum length of transceiver cable between a node and its transceiver is 50 meters (164.05 feet).

- 6. The maximum length of a point-to-point (that is, repeater-to-repeater) link is 1000 meters (3281 feet). (See Figure 1-1.)

Figure 1-1 Large-Scale ETHERNET Configuration

#### 1.1.1 ETHERNET Layers

The ETHERNET architecture consists of two layers.

- Data Link Layer

- Physical Layer

These layers correspond to the lowest architectural layers in the International Standards Organization (ISO) Model for Open Systems Interconnection, and are intended to support higher layers of network architectures. The layer functions are shown in Figure 1-2.

Figure 1-2 ETHERNET Layer Functions

**1.1.1.1 Data Encapsulation** – In the ETHERNET, data is transmitted in packets (also called frames) with a specific format, as shown in Figure 1-3.

Figure 1-3 ETHERNET Packet (Frame) Format

A packet begins with a 64-bit preamble. The preamble is a pattern of alternating 1s and 0s, for receiving node synchronization. To mark the end of the preamble, the pattern ends with ...01011, rather than ...01010.

The destination field contains the 48-bit address of the receiving node(s). The address is either a physical address or logical address, and can be one of the following.

- 1. An individual node address (first address bit = 0).

- 2. A multicast address for a group of nodes (first address bit = 1).

- 3. A broadcast address to all nodes (all address bits = 1).

The source field contains the 48-bit sending node's address. This is either a physical address or logical address. The physical address is the default address, set during manufacture and unique to a node. Software can override the physical address, inserting another physical address into the source field upon packet transmission.

The 16-bit type field determines how higher architectural layers interpret the data field.

The data field must contain at least 46 bytes but no more than 1500 bytes. If the data to be sent consists of less than 46 bytes, software must insert null bytes to fill the field.

The frame check sequence contains a 32-bit Cyclic Redundancy Check (CRC) value. The DEQNA calculates this value inserting it upon packet transmission, and checking it upon packet reception.

The interframe spacing, also called the Inter-Packet Gap (IPG) allows the physical channel to recover between packets. It must be at least 9.6 microseconds, but no more than 10.6 microseconds.

#### **1.2 DEQNA DESCRIPTION**

The DEQNA Q-Bus (LSI-11 bus) data communications controller interfaces the Digital Equipment Corporation LSI-11 processor family to the ETHERNET local area network. It works with both 18-bit address and 22-bit address memories. The DEQNA conforms to the ETHERNET specification, Version 2.0, performing the data link layer functions, and part of the physical layer functions. (See Figure 1-2.)

The DEQNA has the following features.

- 1. Transmits and receives data at a rate of 10 Mbits/s.

- 2. Recognizes heartbeat and collision detection.

- 3. Performs packet serialization, formatting, Manchester encoding, and multiple retransmission.

- 4. Generates and checks 32-bit CRC.

- 5. Interfaces with the H4000 ETHERNET transceiver.

- 6. Performs Direct Memory Access (DMA) transfers to and from CPU memory.

- 7. Contains quick-verify diagnostics for power-up and boot.

- 8. Performs internal and external loopback, and can assist on loopback of data from other stations.

- 9. Supports host system identification response.

- 10. Supports host down-line load and remote boot by other nodes on the network.

The DEQNA comprises one dual LSI-11 module. It plugs into the Q-Bus backplane and resides in the same enclosure. The DEQNA is physically and electrically connected to the H4000 transceiver as shown in Figure 1-4.

Figure 1-4 DEQNA to ETHERNET Connection

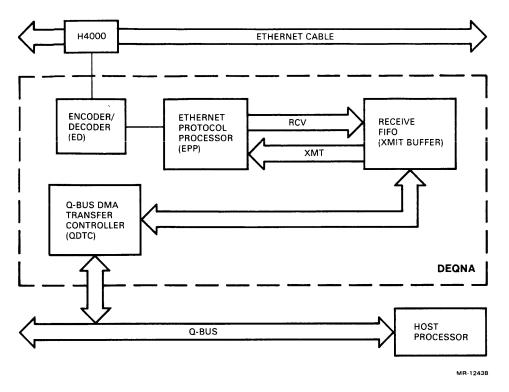

The DEQNA has four major functional areas as shown in Figure 1-5. Each functional area is defined in the following subsections.

Figure 1-5 DEQNA Major Functional Areas

#### 1.2.1 Q-Bus DMA Transfer Controller (QDTC)

The QDTC moves ETHERNET frames and DEQNA control frames between the DEQNA and host memory. It comprises bus transceivers, interrupt control logic, Q-Bus control logic, a DMA registers and counters chip (DMARC), and other control logic. The QDTC performs the host interrupt and DMA transfer functions.

#### 1.2.2 Receive FIFO

The receive FIFO (First-In/First-Out) is a 4 K  $\times$  9-bit RAM. Its usable length for received data is essentially variable from 2 Kbytes to 3565 bytes. In addition to received data, transmit status and receive status are queued in the receive FIFO for transfer to the host.

#### **1.2.3 ETHERNET Protocol Processor (EPP)**

The EPP performs the data link layer functions of link management and data encapsulation/decapsulation. The EPP comprises an Ethernet Data Link Controller (EDLC), a transmit prefill RAM, node address compare logic, and control logic. The EPP performs the following functions.

- 1. Buffers parallel transmit data from the QDTC.

- 2. Converts the parallel transmit data into a serial data stream for the encoder/decoder (ED).

- 3. Maintains the inter-packet gap (IPG) for interframe spacing.

- 4. Generates and strips-off the 64-bit preamble.

- 5. Generates and checks CRC.

- 6. Determines transmit status.

- 7. Initiates retransmission on collision detect.

- 8. Performs address filtering to determine if this is the addressed node.

- 9. Converts the serial received data into parallel data for storage in the receive FIFO.

- 10. Determines receive status.

#### 1.2.4 Encoder/Decoder (ED)

The ED is implemented in high-speed logic, and is connected to the transceiver cable. It performs the following physical layer functions.

- 1. Encodes the serial transmit data stream from the EPP.

- 2. Transmits the Manchester-encoded data to the transceiver.

- 3. Decodes Manchester-encoded data received from the transceiver.

- 4. Sends the serial received data stream to the EPP.

- 5. Signals the EPP when it receives collision detect from the transceiver.

- 6. Performs the carrier sense function and signals the EPP when it detects the presence of a carrier from the coaxial cable.

#### **1.3 DEQNA SYSTEM OPERATION**

The DEQNA and host communicate via two levels of data structures in host memory. First level communication is via eight I/O page addresses in host memory space which correspond to 10 port registers in the DEQNA. This level passes control and status, such as DEQNA error information (as opposed to packet error status), interrupt enable, and DEQNA initialization. Second level communication, via the host communications area, primarily comprises DMA transfers of transmit and receive data.

#### 1.3.1 Port Registers

The DEQNA has 14 port registers, eight of which are in the DMARC. Ten of these registers are accessed through the I/O page, as follows.

- 1. Six read-only registers that are used to read the DEQNA's station address PROM.

- 2. Two 21-bit DMARC registers that hold the starting address of the transmit buffer descriptor list and receive buffer descriptor list.

- 3. The 8-bit read/write DMARC register that holds the DEQNA's interrupt vector.

- 4. The 16-bit read/write DMARC register that is the DEQNA's Control and Status Register (CSR).

The other port registers in the DMARC are not accessed via the I/O page.

- 1. The transmit buffer address and receive buffer address are held in two 21-bit registers.

- 2. The transmit word count and receive word count are held in two 10-bit registers.

A maximum of two DEQNAs can be connected to a host. A unique block of eight I/O page wordaddresses is assigned to each, for control and status transfers. (See Chapter 4, Paragraph 4.2.)

#### **1.3.2** Host Communications Area

An initialized DEQNA has direct access to host memory. When set-up for a DEQNA, host memory has space allocated for receive and transmit buffers and a data base. The data base comprises two sections: the transmit buffer descriptor list, and the receive buffer descriptor list. (See Chapter 4, Paragraph 4.3.)

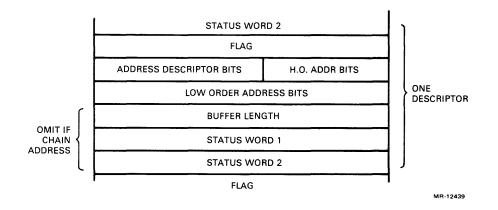

**1.3.2.1 Buffer Descriptor List (BDL)** – A descriptor describes a single buffer by its starting address and length in words. (See Figure 1-6.) Transmit buffer descriptors include other parameters such as unaligned first/last bytes, end of message indicator, and set-up mode flag. Every descriptor includes buffer status and status of the packet that uses the buffer. Initial status is set by the software and updated by the DEQNA.

Figure 1-6 BDL Format

Both buffer descriptor lists (BDLs) are forward-linked lists. The descriptors are either implicitly chained (contiguous descriptors) or explicitly chained (with a chain address). If a list is explicitly chained at some point, the address of the next descriptor (instead of the buffer starting address) is inserted into the current descriptor and its chain address bit is set; buffer length and status words 1 and 2 are omitted.

#### 1.3.3 Initialization

The DEQNA is reset during power-up by BUS INIT and can be reset by host software. At initialization, the host writes the transmit BDL and receive BDL starting addresses to the DEQNA, validating the lists. (See Chapter 4, Paragraph 4.2.4, CSR bits 04 and 05 descriptions.)

#### NOTE

#### The DEQNA will NOT respond to any commands for approximately one second after power-up, although the DEQNA will queue them.

**1.3.3.1 Bootstrap** – The DEQNA contains a 4-Kbyte ROM (BD ROM – Boot/Diagnostic ROM) that host software can read. The BD ROM contains PDP-11 code that is loaded into the host and executed as an extension of the host's primary bootstrap code. (See Chapter 3, Paragraph 3.2.1.)

The BD ROM also contains minimum "good citizen" diagnostic code for the DEQNA. The DEQNA relies on the host for Citizenship Test (CQ) assistance. When executed by the host, this code determines that the DEQNA is a "good citizen" (that is, performing correctly) before it accesses the ETHERNET.

Three LEDs on the DEQNA are all turned on during DEQNA power-up initialization or when the host fetches the boot/diagnostic code (for example, during reboot). The citizenship test turns off the LEDs, one at a time.

- 1. The first is turned off when the test starts running.

- 2. The second when internal loopbacks have successfully completed.

- 3. The third when external loopback has successfully completed.

Citizenship test completion leaves the DEQNA in internal loopback mode, preventing a faulty board from generating spurious ETHERNET transmissions, and with all 14 target addresses set to the DEQNA's physical address. (See Paragraph 1.3.4.1 and Chapter 3, Paragraph 3.2.2.)

**1.3.3.2** Receiver Enable – Software can enable and disable reception in the EPP. The receive function is initialized to the disabled state. Disabling the receive function does not affect a reception in progress; nor does it affect set-up mode, external loopback, or internal extended loopback.

**1.3.3.3** Interrupt Vector – The Q-Bus interrupt controller chip in the QDTC uses the same interrupt vector for transmit, receive, and Nonexistent Memory (NXM) interrupts. The vector assignment is floating, and is written into a DMARC read/write register by software. (See Chapter 4, Paragraph 4.2.4, CSR bits 02, 06, 07, and 15 descriptions.) Software must load the vector before enabling interrupts.

#### 1.3.4 Loopback

There are four loopback modes: set-up mode, internal loopback, external loopback, and internal extended loopback. During set-up mode, internal loopback, and internal extended loopback, the transceiver cable's transmit pair remains idle and the receive and collision pairs are ignored.

Receive status and transmit status are accumulated and stored during all four loopback modes. In internal loopback mode, reception occurs after transmission is complete with transmit status stored. In the other three modes, reception is in parallel with transmission; transmit status is not stored until reception is complete and the receive status is stored.

Note that, with the exception of set-up mode, the loopback modes are exceptional operations, used only for testing, and are not entirely performed in the same way as normal DEQNA operations.

**1.3.4.1** Set-Up Mode – Set-up mode loads a set of 14 target addresses into the DEQNA's target address RAM. The target address RAM is 128 bytes long, and is initialized by software at power-up. It holds 14 target addresses and 2 temporary copies of an incoming packet's destination address.

The target addresses are the node's physical address, the broadcast address, and 12 multicast addresses. The addresses are loaded from a transmit buffer in host memory (the buffer descriptor indicates set-up mode). The frame is stored in the DEQNA instead of being transmitted. However, for verification and synchronization, the information is looped through the receive logic and written into a receive buffer.

Control bits in the set-up mode buffer descriptor can expand the target addresses to include all multicast packets or all packets (Promiscuous Mode). This allows a larger set of packets to be received, with software filtering any unwanted destination addresses. (See Chapter 4, Paragraph 4.3.3.)

**1.3.4.2 Internal Loopback (ILOOP)** – The DEQNA is put in internal loopback mode by asserting (low) CSR bit 08. In this mode, a 10-byte frame is transferred from a transmit buffer to a receive buffer through a full-duplex internal loopback path. This mode exercises most of the DEQNA, and is the only loopback mode that exercises all address recognition logic. The ILOOP packet comprises a 6-byte destination address and a 4-byte CRC appended by the DEQNA.

Any ETHERNET activity concurrent with internal loopback mode is lost. The DEQNA is put in internal loopback mode at initialization and software reset, preventing a failed DEQNA from transmitting on the ETHERNET. (See Chapter 4, Paragraph 4.2.4, CSR bit 08 description.)

**1.3.4.3** External Loopback (ELOOP) – This mode is entered by setting CSR bit 09. Normal packet reception is disabled during operation in this mode. The ELOOP packet is of legal ETHERNET length and is processed similarly to a normal packet. The packet is sent to the transceiver and transmitted on the ETHERNET. The transceiver receive function senses the packet and loops it back to the DEQNA. Address recognition logic is not checked, and the destination address is passed to the host, as usual.

If collisions occur on the ETHERNET while an external loop packet is being received, the Receive FIFO is flushed.

External loopback mode is disabled at initialization and software reset. (See Chapter 4, Paragraph 4.2.4, CSR bit 09 description.)

**1.3.4.4** Internal Extended Loopback (IELOOP) – This mode is similar to external loopback, but the packet is looped back internally instead of going to the transceiver. Internal extended loopback is entered when CSR bits 08 and 09 are both asserted. The packet can be of any legal ETHERNET length; or an illegally long packet can be used to test the LONG receive status bit. Address recognition logic is not checked, and the destination address is passed to the host, as usual.

Because CSR bit 09 is set (as it is in external loopback), normal packet reception is disabled during this mode; and the mode is disabled at initialization and software reset (as is external loopback).

NOTE The DEQNA CRC circuitry is full-duplex and is checked in all loopback modes.

#### 1.3.5 Sanity Timer

The sanity timer is enabled and reset by host software. After the timer is enabled, the software must periodically reset it, otherwise it counts to its limit (that is, it times-out). If time-out occurs, the DEQNA negates Q-Bus DCOK, causing the host power-up/power-down logic to initiate the host's primary bootstrap. Therefore, the timer monitors host software "sanity," triggering a system reboot if software performance degrades to a point of DEQNA driver failure.

At initialization, the timer is disabled (or enabled, if a jumper is removed). The default time-out period is 4 minutes, and is software variable between 1/4 second and approximately 1 hour; the period reverts to 4 minutes following two successive time-outs. In response to a remote node request that it reboot itself, the host can do so by allowing the time-out period to expire. (See Chapter 4, Paragraph 4.2.4, CSR bit 10 description, and Paragraph 4.3.3.2.)

#### 1.3.6 Transmit

To initiate packet transmission, the host builds the transmit BDL and writes the BDL starting address into the transmit descriptor address port register. The QDTC then updates the first descriptor's status to USING (see Chapter 4, Paragraph 4.3.2), and continues by reading the buffer address, descriptor bits, buffer length, and the buffer itself. If the buffer descriptor indicated that this buffer includes the end of the message, the DEQNA attempts to transmit the packet. Otherwise, the message includes additional buffers, and the QDTC updates the status of the additional descriptors, reading the necessary buffers until the end-of-message is indicated, before attempting to transmit.

The QDTC reads the packet data (from one or more transmit buffers in host memory) into the EPP prefill RAM. When it reads a descriptor with the end-of-message bit asserted and the last data has been transferred from that buffer to the prefill RAM, the DEQNA attempts to transmit the packet stored in the prefill RAM. If a collision occurs, the DEQNA attempts to retransmit the stored packet.

Transmit status is accumulated in the receive FIFO during and after successful or aborted packet transmission. Eventually, the accumulated status is written into the two status words of the descriptor for the last buffer of the packet, and the host is notified with an interrupt from the DEQNA.

The QDTC continues by accessing the next buffer descriptor. If the descriptor is valid, another transmission sequence begins. If the descriptor is not valid, the QDTC stops accessing the transmit BDDL and associated buffers.

A valid buffer descriptor can also describe a chaining operation. Then, the descriptor chain address bit is asserted, and the address in the descriptor points to another buffer descriptor instead of a buffer. (See Chapter 4, Paragraph 4.3.2.3.)

The DEQNA transmit sequence is as follows.

- 1. Write USING status into the buffer descriptor.

- 2. Read the buffer address and length from the buffer descriptor.

- 3. Start the buffer read on an odd byte (optional).

- 4. Read the packet from the buffer.

- 5. End the buffer read on an even byte (optional).

- 6. Either:

- a. Write USED status into the buffer descriptor and continue the transmission sequence from the next buffer, or

- b. start the transmission attempts with this buffer.

- 7. Write the transmit status into the buffer descriptor.

- 8. Interrupt the host at the end of the transmission sequence after writing the transmit status.

- 9. Either:

- a. Start the next transmission sequence from the next buffer, or

- b. "chain" to the next BDL, or

- c. invalidate this BDL.

#### 1.3.7 Receive

Packet reception occurs in three states. First, the received packet's destination address field is compared to the set of target addresses stored in the target address RAM. This address filtering occurs in parallel with reception of the first 60 packet bytes. (Because the 4-byte CRC is stripped-off by the EDLC, these 60 bytes constitute a minimum valid reception.)

Second, if there is an address match and the packet is long enough, the packet continues to be stored in the receive FIFO until the message is complete. However, if there is no address match or the packet is a runt packet from a collision, the FIFO is either flushed or compensated. If the FIFO was previously empty, it is flushed; but if the FIFO contained previous good data, it is compensated by setting RUNT in the received status. Runt status is assigned to an incomplete packet stored in the receive FIFO because either address match failed and the reception was truncated, or a collision occurred during reception and the packet was too short.

Third, the QDTC empties the receive FIFO into the receive buffer(s) and writes the receive status into the two status words of the final receive buffer descriptor. Multiple packets are queued in the receive FIFO as they are received.

The DEQNA receive sequence is as follows.

- 1. Write USING status into the buffer descriptor.

- 2. Read the buffer address and length from the buffer descriptor.

- 3. Write the received frame into the buffer.

- 4. Either:

- a. Write USED status into the buffer descriptor and continue the reception sequence into the next buffer, or

- b. end the reception sequence with this buffer.

- 5. Write the receive status into the buffer descriptor.

- 6. Interrupt the host at the end of the reception sequence after writing the receive status.

- 7. Either:

- a. Start the next reception sequence into the next buffer, or

- b. "chain" to the next BDL, or

- c. invalidate this BDL.

#### **1.4 Q-BUS INTERFACE**

The DEQNA works most efficiently with 22-bit block-mode memory. It also works with 18-bit memory and non-block-mode memory. It relies on host software to map DMA addresses into the memory address space.

The Q-Bus interface comprises slave and master logic.

#### 1.4.1 Slave Logic

The slave logic gives the host access to the port registers in the DMARC and the station address PROM.

#### 1.4.2 Master Logic

The master logic performs the QDTC DMA functions, including the following.

- Addressing host memory

- Transferring data

- Fetching descriptors

- Storing status

- Incrementing addresses and word counts

- Monitoring word count overflow

On systems with block mode memories, Q-Bus block mode DMA transfers give a data transfer rate of up to 3.2 Mbytes/second. DMA transfers are automatically blocked at 4 to 16 words per bus acquisition.

The DEQNA includes a holdoff timer. This timer allows other DMA devices to acquire the bus, by causing the DEQNA to wait for approximately 5 microseconds before re-requesting the bus (that is, before reasserting BDMR). The timer is disabled if the receive FIFO is more than half full; for special applications, it can be permanently disabled by adding a jumper.

The DEQNA also includes a bus time-out timer. This timer causes the bus cycle to abort and a Nonexistent Memory (NXM) interrupt to be generated if the bus slave fails to respond within approximately 10 microseconds.

#### **1.5 DEQNA SPECIFICATIONS**

The DEQNA specifications are listed in Table 1.1.

| Specification                                                                                                                          | Description                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Operating Mode                                                                                                                         | Half-duplex (non-loopback)                                                                     |

| Data Format                                                                                                                            | Manchester encoded, serial                                                                     |

| ETHERNET Data Rate                                                                                                                     | 10 megabits per second                                                                         |

| Q-Bus Backplane Loading                                                                                                                | 0.5 dc load<br>2.2 ac loads                                                                    |

| DC Power Requirements (typical)<br>DEQNA<br>H4000 Transceiver                                                                          | +5 V, 3.5 A<br>+12 V, 0.5 A                                                                    |

| Operating Environment (System)<br>Temperature<br>Relative Humidity<br>Wet Bolt Temperature (maximum)<br>Dewpoint (minimum)<br>Altitude | 5 to 50° C (41 to 122° F)<br>10% to 90%<br>28° C (82° F)<br>2° C (36° F)<br>Same as for system |

| Shipping Environment<br>Temperature<br>Relative Humidity<br>Altitude                                                                   | Same as for system<br>Same as for system<br>Same as for system                                 |

#### Table 1-1 DEQNA Specifications

In addition to those listed above, the DEQNA meets ETHERNET Specification, Version 2.0 requirements.

### **1.6 RELATED DOCUMENTS**

Table 1-2 lists documents related to this guide.

| Title                                                                                    | Number          |

|------------------------------------------------------------------------------------------|-----------------|

| H4000 Ethernet Transceiver Field Maintenance Print Set                                   | MP-01369        |

| H4000 Ethernet Transceiver Technical Manual                                              | EK-H4000-TM-PRE |

| The ETHERNET, A Local Area Network, Data Link<br>Layer and Physical Layer Specifications | АА-К759А-ТК     |

| Introduction to Local Area Networks                                                      | EB-22714-18     |

#### Table 1-2 Related Documents

DIGITAL personnel may order hardcopy documents from:

Digital Equipment Corporation 444 Whitney Street Northboro, MA 01532

#### Attn: Publishing and Circulation Services (NR03/W3) Order Processing Section

Customers may order hardcopy documents from:

Digital Equipment Corporation Peripherals and Supplies Group P.O. Box CS2008 Nashua, NH 03061

For information on microfiche libraries, contact:

Digital Equipment Corporation Micropublishing Group (BUO/E46) 12 Crosby Drive Bedford, MA 01730

# CHAPTER 2 INSTALLATION

This chapter describes the procedures to install a DEQNA in an LSI-11 host system. The system described is a MICRO/PDP-11 system. The chapter includes the following sections.

Unpacking and Inspection - Verify that the shipment is complete and not damaged.

**Preinstallation Verification** – Verify that the host system meets the DEQNA installation requirements.

Preparation – Prepare the host system and DEQNA for proper operation.

Installation - Install the DEQNA and transceiver cable in the host system.

**Testing** – Verify correct operation of the DEQNA and host system.

#### 2.1 UNPACKING AND INSPECTION

Unpacking a DEQNA consists of removing the equipment from its shipping containers, verifying that no parts are missing, and inspecting the equipment for damage. Report any damage or shortages to the shipper and notify the Digital representative.

- 1. Before opening the shipping containers, look for external damage such as dents, holes, or crushed corners.

- 2. Open and unpack each container. Inventory the contents using the shipping list. Table 2-1 lists the parts supplied with each DEQNA.

#### NOTE Shipping containers and packing materials should be retained if reshipment is likely.

3. Inspect every DEQNA part for shipping damage. Check carefully for cracks, breaks, and loose components.

| Part Description                                                                                                                                                                                                           | Designation                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| DEQNA Module                                                                                                                                                                                                               | M7504                                                    |  |

| Bulkhead Cable Assembly (one of the following):                                                                                                                                                                            |                                                          |  |

| 53.3 cm (21 in) shielded cable/bulkhead (PDP-11/23)<br>30.5 cm (12 in) shielded cable/bulkhead (MICRO/PDP-11)<br>76.2 cm (30 in) shielded cable/bulkhead (PDP-11/23-PLUS)<br>3.048 m (10 ft) shielded cable (general use*) | CK-DEQNA-KA<br>CK-DEQNA-KB<br>CK-DEQNA-KC<br>CK-DEQNA-KD |  |

| DEQNA User's Guide                                                                                                                                                                                                         | EK-DEQNA-UG-001                                          |  |

| DEQNA PDP-11 Diagnostic Set (Field<br>Diagnostic Resident Code)                                                                                                                                                            | CIQN DAO<br>AC-T612A-MC                                  |  |

#### Table 2-1DEQNA Parts List

\* Non-FCC compliant installations

#### 2.2 PREINSTALLATION VERIFICATION

To verify that the DEQNA can be correctly installed in the host system, the following requirements and constraints must be met.

#### 2.2.1 Host Boot/Diagnostic ROMs

Verify that the correct boot/diagnostic ROMs are installed in the host CPU. That is, the host CPU must be capable of loading the extended bootstrap code from the DEQNA BD ROM.

#### 2.2.2 Backplane Requirements

The DEQNA requires one dual LSI-11 module slot configured for Q22-Bus (that is, extended LSI-11 bus) operation for highest performance.

#### 2.2.3 Bus Latency Constraints

To get the best performance and avoid losing packets, the DEQNA should be the highest priority device on the Q-Bus, that is, the DMA device nearest to the CPU. When two DEQNAs are installed, a blockmode memory is required, if high ETHERNET traffic rates are to be handled. The following is a recommended module installation.

| Processor       | Slot 1      |

|-----------------|-------------|

| Memory          | Slot 2      |

| DEQNA 1         | Slot 3      |

| DEQNA 2 / Other | Slot 4      |

| Others          | Slots 5 – 8 |

#### 2.2.4 Loading Requirements

Check that system loading capacity is not exceeded by installing the DEQNA. Table 2-2 shows the DEQNA Q-Bus loading and Table 2-3 shows the DEQNA and transceiver power requirements.

#### CAUTION

Power supply voltages should be checked before and after installation to verify the absence of overloading and overvoltage conditions.

| Module | Q-Bus dc Loads | Q-Bus ac Loads |

|--------|----------------|----------------|

| M7504  | 0.5            | 2.2            |

| Table 2-2 | DEQNA | <b>Q-Bus</b> | Loading |

|-----------|-------|--------------|---------|

|-----------|-------|--------------|---------|

| Voltage Rating<br>(Typical Values)         | Typical<br>Current | Maximum<br>Current | Backplane<br>Pins                       |

|--------------------------------------------|--------------------|--------------------|-----------------------------------------|

| +5 ± 0.25 V @ 3.5 A                        | 3.5 A              | 5.0 A              | AA2, BA2, BV1                           |

| $+12 \pm 0.60$ V @ 0.5 A (for Transceiver) | 0.5 A              | *                  | BD2                                     |

| Logic Reference                            |                    |                    | AJ1, AM1, AT1,<br>AC2, BJ1, BM1,<br>BC2 |

| Transceiver Return                         |                    |                    | <b>BT</b> 1                             |

Table 2-3 DEQNA Power Requirements

\*At power-up or powered-up connect, transceiver surge current at the power connection is high enough to currentlimit and power-fail some power supplies. The DEQNA does not contain power supply surge protection; it must be provided elsewhere if required by the system configuration.

#### 2.3 PREPARATION

Prepare the host and DEQNA for installation using the following procedure.

#### 2.3.1 Backplane

- 1. Turn system power off, and unplug the ac power cord from the wall socket.

- a. Remove the rear plastic cover of the system unit by holding each end and pulling the cover toward you. (Does not apply to rack-mounted units.)

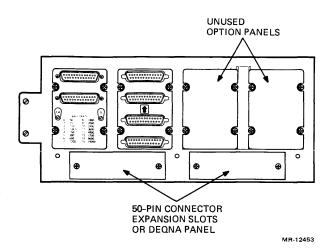

- b. Open the patch and filter panel assembly (also called the system I/O panel, the distribution panel, and the bulkhead). (See Figure 2-1.) Loosen the two screws at the end of the panel opposite the hinge, and swing the panel open.

- c. If necessary, reconfigure the system to accept the DEQNA in the appropriate backplane slot. (See Paragraph 2.2.3.) Remove or relocate M7272 Grant Continuity cards as necessary.

- 2. Plug the ac power cord into the wall socket, and turn system power on.

- 3. Measure the backplane voltages. They should be within the tolerances listed in Table 2-3.

- 4. Turn system power off and unplug the ac power cord from the wall socket.

Figure 2-1 Patch and Filter Panel Assembly

#### 2.3.2 M7504 Module

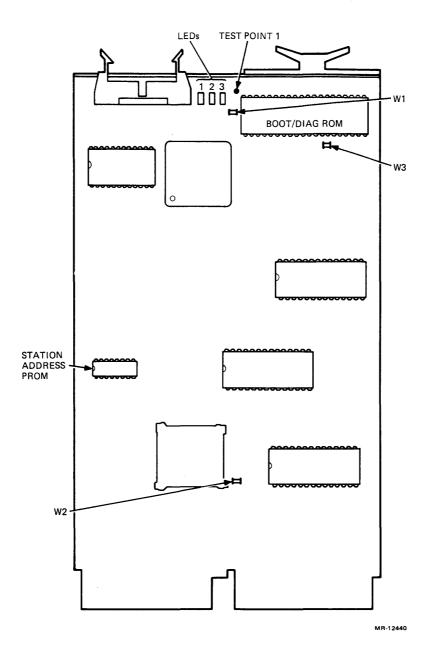

The DEQNA module, M7504, is configured with three jumpers, W1 through W3, installed during manufacture. (See Figure 2-2 and Table 2-4.) The disposition of these jumpers is described in the following paragraphs.

**2.3.2.1 Device Address Assignment (W1)** – The DEQNA I/O page addresses are 17774440 (first DEQNA) and 17774460 (second DEQNA). If two DEQNAs are to be installed, move jumper W1 onto the second DEQNA position, to set its I/O page address to 17774460. (See Chapter 4, Paragraph 4.2.)

**2.3.2.2** Bus Request Holdoff Timer (W2) – Jumper W2 provides "fair" access to all DMA devices using the Q-Bus (see Chapter 1, Paragraph 1.4.2), and should not be added, except for unusual requirements (not supplied).

**2.3.2.3** Sanity Timer (W3) – If not removed, jumper W3 disables the sanity timer at initialization. If removed, jumper W3 enables the sanity timer at initialization. (See Chapter 1, Paragraph 1.3.6.)

#### 2.3.3 Patch and Filter Panel Assembly

The transceiver cable bulkhead assembly will be installed in an unused option panel location on the system I/O panel. (See Figure 2-1.) Remove the option panel by removing the four screws. Save the screws.

#### 2.4 INSTALLATION

Install and cable the DEQNA and the bulkhead assembly as follows. (See Figure 2-3.)

- 1. Slide the M7504 module into the card guides with the component side nearest to the processor module. Do not insert the module all the way into the slot at this time.

- 2. Insert the transceiver cable assembly into the system I/O panel with the four screws saved when the blank panel was removed.

- 3. Connect the keyed cable of the bulkhead assembly to the module.

- 4. Slide the M7504 all the way into the card slot.

Figure 2-2 M7054 Showing Jumpers, LEDs, Transceiver Cable Connector, Station Address PROM, and Boot/Diag PROM

| Jumper     | Function                       | In       | Out/<br>2nd Position |

|------------|--------------------------------|----------|----------------------|

| <b>W</b> 1 | I/O Page Address               | 17774440 | 17774460             |

| W2         | BDMR Holdoff Timer             | No Delay | 5 µs Delay           |

| W3         | Sanity Timer at Initialization | Disabled | Enabled              |

| Table 2 | 2-4 ] | DEQNA | Jumper | Functions |

|---------|-------|-------|--------|-----------|

|---------|-------|-------|--------|-----------|

#### 2.5 TESTING

Perform the following tests to verify that the DEQNA and host system are operating correctly.

NOTE In order to successfully run the citizenship (CQ) diagnostic tests, either an operational ETHERNET transceiver with cable must be connected to the DEQNA, or the loopback connector must be connected to the bulkhead assembly.

#### 2.5.1 Post-Installation Power Checks

Perform the following tests on the backplane slot that contains the M7504 module.

- 1. Plug the ac power cord into the wall socket, and turn the system power on.

- 2. Measure the backplane voltages. They should be within the tolerances listed in Table 2-3.

- 3. Turn system power off.

#### 2.5.2 Light-Emitting Diode (LED) Checks

The M7504 module includes three LEDs which indicate the operational status of the DEQNA. (See Figure 2-2.) Table 2-5 defines the LED indications.

| 1                       | LED<br>2               | 3                     | Definition                                                                                                                                                                                                                         |

|-------------------------|------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF<br>OFF<br>OFF<br>ON | OFF<br>OFF<br>ON<br>ON | OFF<br>ON<br>ON<br>ON | The DEQNA passed all citizenship tests.<br>Transceiver, ETHERNET, or cable error.<br>DEQNA internal error.<br>Cannot upload BD ROM contents, the bootstrap has not yet executed, or<br>the first set-up packet prefill has failed. |

- 1. Connect either an ETHERNET transceiver with cable or a loopback connector to the transceiver er cable connector on the patch and filter panel assembly. (See Figure 2-1.)

- 2. Turn system power on. All three LEDs on the M7504 module should be on within one second.

- 3. Boot the system from the DEQNA. Note that new CPU PROMs (with code for booting from the DEQNA) must have been installed. The LEDs should be turned off, one at a time, until no LEDs are on.

#### 2.5.3 Diagnostic Acceptance Procedure

- 1. Run the field functional test. (See Chapter 3, Paragraph 3.2.3.)

- 2. Turn system power off.

- 3. Close and fasten the patch and filter panel assembly.

- 4. If a loopback test transceiver was used, disconnect it.

- 5. Replace the rear plastic cover on the system unit. (Does not apply to rack-mounted units.)

- 6. If not already connected, connect the system to an installed ETHERNET transceiver.

Installation is now complete.

.

-

# CHAPTER 3 SERVICE

This chapter describes servicing the DEQNA. It includes the following sections.

Maintenance Philosophy - Defines the DEQNA Field Replaceable Units (FRUs).

**Diagnostics** – Describes the DEQNA diagnostic programs.

Corrective Maintenance - Describes the corrective maintenance procedures for the DEQNA.

#### 3.1 MAINTENANCE PHILOSOPHY

Corrective maintenance is performed by FRU replacement. The following are the field replaceable units.

- 1. M7504 module

- 2. Bulkhead cable assembly

- 3. Bulkhead fuse

- 4. Ampere filter (if used)

#### NOTE

When the module is replaced, the user may be able to retain the original ETHERNET address by swapping the station address PROM from the replaced module to the new module, and verifying with diagnostics that the original station address PROM works in the new module.

#### **3.2 DIAGNOSTICS**

The DEQNA diagnostics include software to boot the DEQNA, tests to ensure that the module is working correctly, and tests to isolate faults.

#### 3.2.1 Extended Primary Bootstrap (EPB)

The DEQNA is loaded, or booted, in a way that is similar to mass storage device booting. Host primary boot code passes control to the Extended Primary Bootstrap (EPB) code (loaded from the BD ROM), which continues the bootstrap process by loading the complete contents of the BD ROM into host memory. When the load is complete, the DEQNA citizenship test is run before the DEQNA is allowed to access the ETHERNET.

If the citizenship test is passed, the bootstrap process continues. Control is transferred to either the DECnet bootstrap, which is part of the Maintenance Operation Protocol (MOP) code loaded from the BD ROM, or to an address in host memory.

If the DEQNA fails the citizenship test, the EPB code attempts to halt the CPU, without attempting to boot DECnet or transferring control to a user's program. The LEDs on the DEQNA help to indicate the nature of the failure.

In general, the boot sequence is as follows.

- 1. Load the first 512 bytes of BD ROM. This is the EPB code.

- 2. Verify descriptor status and the CSR.

- 3. In the host, set up registers R0 and R1, and location 12 (octal) of main memory (see next step). Continue.

- 4. If a failure is detected, examine location 12 (octal) of main memory. If location 12 is zero, halt the EPB. If location 12 is non-zero, transfer control to the address contained in location 12.

- 5. Load the remaining bytes of the BD ROM into host memory.

- 6. Verify the BD ROM data transfer using the ROM checksum.

- 7. The host executes the citizenship test.

- 8. If the citizenship test fails, return control to the EPB and halt.

- 9. If the citizenship test passes, transfer control (as determined by the value in host register R0) to either:

- a. The MOP code to boot DECnet. This code continuously attempts to boot DECnet until successful or until stopped by the host.

- b. User defined code.

#### 3.2.2 Citizenship Test (CQ)

The DEQNA Citizenship Test (CQ) is a series of diagnostic test routines that determine if the DEQNA is operating correctly and can access the ETHERNET or is faulty and requires further diagnosis. Test results are indicated by the LEDs on the DEQNA and are returned in host register R0, where they are accessible to software. The CQ test uses internal loopback, internal extended loopback, and external loopback modes, and requires the DEQNA and an H4000 transceiver (or equivalent); connection to the ETHERNET is not required. Prior to executing the tests, CQ turns off the sanity timer. Upon completion of the tests, it turns the sanity timer on if jumper W3 is removed (timer enabled), or leaves the timer off if jumper W3 is in place (timer disabled).

The CQ test is a free-standing subroutine and can be called by other software. For example, during network boot, CQ can determine if the node should be allowed to proceed from the initialized state to either a functional state or nonfunctional state. If a fault exists, MOP code can call CQ to determine if other DEQNA diagnostics or network-level diagnostics are required for fault isolation.

**3.2.2.1** Test Descriptions – The tests are described in the following list. Corresponding bit numbers in host register R0 are given for each possible error reported by the test. An error summary is given in Paragraph 3.2.2.2.

1. Station Address Verification – The default physical address is verified and copied from the station address ROM into a test packet for later use. If this test fails, testing continues until the final external loopback test or another test failure occurs. Possible errors are:

| <b>R0 Bit</b> | Description                                   |

|---------------|-----------------------------------------------|

| 00            | Station address is all zero bits.             |

| 00            | Station address is all one bits.              |

| 00            | Station address is not a valid DEQNA address. |

| 10            | Bus time-out or nonexistent memory error.     |

2. Device Interrupt and Nonexistent Memory – After interrupts are enabled, a transmit buffer descriptor chained to a nonexistent memory location is sent to the Unit Under Test (UUT), that is, one of the two possible DEQNAs. The UUT should generate a transmit interrupt with the CSR NI bit (bit 02) set. Possible errors are:

| <b>R0 Bit</b> | Description                     |

|---------------|---------------------------------|

| 11            | No interrupt occurred.          |

| 11            | Interrupt occurred prematurely. |

| 11            | Wrong interrupt occurred.       |

3. Set-up Mode and Receive FIFO Processing – A series of set-up packets is transmitted to the UUT, to test "stuck-at" faults. The packets contain repeating test patterns which are varied to test each target address RAM byte with all patterns. The set-up packets are echoed into the receive FIFO and verified. The set-up packet lengths are such that all the receive FIFO bytes receive each of the four basic patterns, as the operation is repeated. Possible errors are:

**R0 Bit Description**

| 12,01    | Target address echoed data check.     |

|----------|---------------------------------------|

| 09,12,01 | Set-up packet operation time-out.     |

| 14,12,01 | Set-up packet operation status check. |

4. Internal Loopback and Address Filter – A target address set-up packet with "walking" bit pattern is generated and set-up in the UUT. Then, two internal loopback packets are generated and transmitted for each address in the pattern. The first packet is addressed to the complemented target address (not in the pattern), and must be correctly transmitted and received as a runt. (See Chapter 1, Paragraph 1.3.7.) The second packet is addressed to a target address in the pattern, and must be correctly transmitted.

The test is repeated with the walking bit = 1 and the walking bit = 0. Possible errors are:

| <b>R0 Bit</b> | Description                                               |

|---------------|-----------------------------------------------------------|

| 02            | Transmitted and received and data compare check.          |

| 09,02         | Runt packet transmit and receive operation time-out.      |

| 09,02         | Valid packet transmit and receive operation time-out.     |

| 12,02         | Target address echoed data check.                         |

| 14,02         | Runt packet transmit and receive operation status check.  |

| 14,02         | Valid packet transmit and receive operation status check. |

| 09,12,02      | Set-up packet operation time-out.                         |

| 14,12,02      | Set-up packet operation status check.                     |

5. Internal Extended Loopback and Protocol – The UUT is put in internal extended loopback mode and packets of increasing length are circulated through the transmit buffer (prefill RAM) and the receive FIFO. The packet bit patterns are intended to uncover "stuck-at" conditions and faults in buffer and FIFO processing. The received packets are verified to be sure that data was correctly transferred. The packet lengths increase in 3-byte increments, from the minimum ETHERNET packet size to beyond the maximum size. The test completes when the UUT detects the expected long packet. Possible errors are:

| R0 Bit | Description                                                     |

|--------|-----------------------------------------------------------------|

| 03     | Long packet not detected via device transmit status.            |

| 03     | Internal extended loopback transmit/receive data compare check. |

| 09,03  | Test packet transmit or receive operation timed-out.            |

| 14,03  | General operation status, check, long packet not detected.      |

6. **DMA Q-Bus Interface Processing** – An internal extended loopback packet based on a transmit BDL with contiguous and chained unaligned buffer segments is transmitted using the default physical address. This packet is received and verified. Possible errors are:

| <b>R0 Bit</b> | Description                                               |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 04            | DMA Q-Bus interface transmit (scatter/gather) data check. |  |  |

| 09,04         | Transmit (special) and receive operation time-out.        |  |  |

| 14,04         | Receive or transmit operation status check.               |  |  |

7. **Transceiver Operational and Status** – A set-up packet with the physical address of the UUT is generated and sent to the target address RAM. The packet also turns off LED 2. The CSR carrier bit (bit 13) is monitored to be sure it is cleared; or, if it is set, that it is cleared within approximately 100 microseconds. Possible errors are:

| <b>R0 Bit</b> | Description                                               |

|---------------|-----------------------------------------------------------|

| 12            | Target address packet with LED command echoed data check. |

| 09,12         | Set-up packet operation time-out.                         |

| 14,12         | Set-up packet operation status check.                     |

| 15            | CSR carrier bit on too long.                              |

8. External Loopback and ETHERNET Protocol – This test is executed only if no other errors have been detected.

The physical address of the UUT is assumed to be in the target address RAM. A minimum size ETHERNET packet, with a descending-integers data pattern and addressed to the UUT, is transmitted and received using external loopback. Next, a maximum size ETHERNET packet with the same characteristics is generated and sent to the UUT. Both packets test ETHERNET protocol processing, and the maximum size packet also tests the transmit buffer.

Packets which "go on the wire" are compatible with loopback test packets, have the protocol type set to loopback, and other fields set such that testers ignore these packets. The destination (and source) address of the loopback packet is the assigned ETHERNET station address of the UUT (that is, its default physical address). Possible errors are:

| <b>R0 Bit</b> | Description                                               |  |  |

|---------------|-----------------------------------------------------------|--|--|

| 15            | External loopback over ETHERNET cable is not operational. |  |  |

| 05            | Minimum or maximum sized packet data compare check.       |  |  |

| 09,05         | Minimum/maximum packet operation time-out.                |  |  |

| 14,05         | Minimum/maximum packet operation status check.            |  |  |

3.2.2.2 Test Results - The CQ test will either execute successfully or fail. The two possibilities are described below.

- 1. If the CQ test executes successfully, the value of host register R0 is zero and the DEQNA is setup as follows.

- a. All three LEDs are off.

- b. All 14 target addresses are set to the physical address from the station address ROM.

- c. The sanity timer is set to its default interval (4 minutes) and disabled or enabled, according to the disposition of the sanity timer jumper (W3).

- d. Promiscuous and all multicast address modes are off.

- e. The DEQNA has been reset:

Receive is disabled Transmit is disabled

2. If the CQ test fails, the LED indications will display the following error codes.

| LED<br>1         | 2               | 3              | Definition                                                                                                                           |

|------------------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| OFF<br>OFF<br>ON | OFF<br>ON<br>ON | ON<br>ON<br>ON | Transceiver or ETHERNET error<br>DEQNA internal error<br>Cannot upload BD ROM contents or the first set-up packet<br>prefill failed. |

If the DEQNA passed the tests, all the LEDs are off.

The bits in register R0 indicate the test that failed. If bit 15 is the only bit set, the DEQNA passed all the CQ tests except those which require a connected transceiver. The errors/bits are defined as follows (multiple bits can be set).

Error/

| Bit | Error Definition and Source(s)                                                                                                                                                                                                                                         |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | External loopback not operational (Tests 7 and 8)                                                                                                                                                                                                                      |

|     | ETHERNET not operational<br>H4000 not operational (blown fuse, disconnected)                                                                                                                                                                                           |

| 14  | Operation completion status check (all tests)                                                                                                                                                                                                                          |

|     | CSR status after final reset not nominal<br>CSR status after transmit and/or receive not nominal<br>Receive descriptor flags and status word 1 not nominal<br>Received byte length check<br>Transmit descriptor flags and status word 1 not nominal<br>TDR value = $0$ |

| 13  | Sanity timer interrupt (general error)                                                                                                                                                                                                                                 |

|     | Power failed during test<br>Unexpected sanity timer interrupt                                                                                                                                                                                                          |

| 12  | Set-up packet or target address echo check (all tests)                                                                                                                                                                                                                 |

|     | Set-up packet transmit time-out<br>Transmit status not nominal<br>Set-up packet receive time-out<br>Receive status not nominal<br>Echoed data not identical to transmitted data<br>Extra word at end of set-up packet not nominal                                      |

| 11  | Spurious or missing device interrupt (general error)                                                                                                                                                                                                                   |

|     | Expected device interrupt not detected<br>Device did not detect nonexistent memory (NXM) bus state<br>18-bit or 22-bit addressing failure<br>Unexpected DEQNA device interrupt                                                                                         |

| 10  | Bus time-out or NXM interrupt (general error)                                                                                                                                                                                                                          |

|     | I/O page not accessible for read or write<br>Cannot read station address ROM<br>Test code attempted to access nonexistent memory                                                                                                                                       |

| 09  | Device operation time-out (all tests)                                                                                                                                                                                                                                  |

|     | Unit under test failed to complete a transmit and/or receive in time                                                                                                                                                                                                   |

| 08  | Undefined                                                                                                                                                                                                                                                              |

| 07 | Undefined                                                                                                                                              |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06 | Undefined                                                                                                                                              |

| 05 | ETHERNET external loopback test check (Test 8)                                                                                                         |

|    | ETHERNET protocol processing check<br>ETHERNET minimum valid length processing check<br>ETHERNET maximum valid length processing check                 |

| 04 | DMA interface processing check (Test 6)                                                                                                                |

|    | DMA odd/even length and address processing check<br>Multielement transmit descriptor processing check<br>Chained transmit descriptor processing check  |

| 03 | Internal extended loopback transmit buffer data check (Test 5)                                                                                         |

|    | ETHERNET protocol processing check<br>Transmit buffer memory malfunction<br>Packet size processing error (protocol error)                              |

| 02 | Station address compare test check (Test 4)                                                                                                            |

|    | Address filter logic passing all addresses<br>Address filter logic not passing expected addresses                                                      |

| 01 | Station address/receive FIFO processing check (Test 3)                                                                                                 |

|    | Target address RAM malfunction<br>Packets not properly stored in receive FIFO<br>Receive FIFO memory malfunction                                       |

| 00 | Invalid ETHERNET station address (Test 1)                                                                                                              |

|    | I/O page register read failure (see also bit 10)<br>Unit under test is not a DEQNA (M7504)<br>Station address ROM malfunction<br>Invalid DEQNA address |

# **3.2.3** Field Functional Test

The Field Functional Diagnostic Program (ZQNA) tests the DEQNA in Q18 or Q22-Bus systems. It attempts to isolate faults to the following FRUs.

- 1. DEQNA

- 2. Bulkhead assembly

- 3. Bulkhead assembly fuse

- 4. Transceiver cable

- 5. Transceiver

The ZQNA also attempts to localize faults to the failing DEQNA functional area(s).

- 1. Q-Bus DMA Transfer Controller (QDTC)

- 2. Receive First-In/First-Out (FIFO) and transmit buffer memory

- 3. ETHERNET Protocol Processor (EPP)

- 4. Manchester Encoder/Decoder (ED/DE)

Tests are executed under the supervision of the XXDP/DRS, and controlled by an operator from a console (hard copy or video). For DRS commands, see Appendix C, Paragraph C.4, or the XXDP+ User's Manual.

Note that the ZQNA diagnostic program is not an ETHERNET network exerciser. The ZQNA assures that the module can execute ETHERNET protocol and that valid network traffic can be transmitted and that valid network traffic can be received. The network exerciser (see Appendix C) provides a higher level of testing.