# On Interprocess Communication

Leslie Lamport

December 25, 1985

## Systems Research Center

DEC's business and technology objectives require a strong research program. The Systems Research Center (SRC) and three other research laboratories are committed to filling that need.

SRC began recruiting its first research scientists in 1984—their charter, to advance the state of knowledge in all aspects of computer systems research. Our current work includes exploring high-performance personal computing, distributed computing, programming environments, system modelling techniques, specification technology, and tightly-coupled multiprocessors.

Our approach to both hardware and software research is to create and use real systems so that we can investigate their properties fully. Complex systems cannot be evaluated solely in the abstract. Based on this belief, our strategy is to demonstrate the technical and practical feasibility of our ideas by building prototypes and using them as daily tools. The experience we gain is useful in the short term in enabling us to refine our designs, and invaluable in the long term in helping us to advance the state of knowledge about those systems. Most of the major advances in information systems have come through this strategy, including time-sharing, the ArpaNet, and distributed personal computing.

SRC also performs work of a more mathematical flavor which complements our systems research. Some of this work is in established fields of theoretical computer science, such as the analysis of algorithms, computational geometry, and logics of programming. The rest of this work explores new ground motivated by problems that arise in our systems research.

DEC has a strong commitment to communicating the results and experience gained through pursuing these activities. The Company values the improved understanding that comes with exposing and testing our ideas within the research community. SRC will therefore report results in conferences, in professional journals, and in our research report series. We will seek users for our prototype systems among those with whom we have common research interests, and we will encourage collaboration with university researchers.

Robert W. Taylor, Director

### On Interprocess Communication

Leslie Lamport December 25, 1985

Much of this research was performed while the author was a member of the Computer Science Laboratory at SRI International, where it was sponsored by the Office of Naval Research Project under contract number N00014-84-C-0621 and the Rome Air Development Command Project under contract number F30602-85-C-0024.

| Publication History                                |                  |                                |   |  |  |  |

|----------------------------------------------------|------------------|--------------------------------|---|--|--|--|

| The two parts of this report will ap $Computing$ . | pear as separate | articles in <i>Distributed</i> | d |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

|                                                    |                  |                                |   |  |  |  |

Copyright 1986 by Springer-Verlag. All rights reserved. Printed with permission.

#### Author's Abstract

A formalism, not based upon atomic actions, for specifying and reasoning about concurrent systems is defined. It is used to specify several classes of interprocess communication mechanisms and to prove the correctness of algorithms for implementing them.

#### Capsule Review by Andrei Broder

Concurrent systems are customarily described hierarchically, each level being intended to implement the level above it. On each level certain actions are considered atomic with respect to that level, although they decompose into a set of actions at a lower level. Furthermore there are cases when, for efficiency purposes, their components might be interleaved in time at a lower level with no loss of semantic correctess, despite the fact that the atomicity specified on the higher level is not respected. In this paper a very clean formalism is developed that allows a cohesive description of the different levels and axiomatic proofs of the implementation properties, without using the atomic action concept.

#### Capsule Review by Paul McJones

A common approach to dealing with concurrency is to introduce primitives allowing the programmer to think in terms of the more familiar sequential model. For example, database transactions and linguistic constructs for mutual exclusion such as the monitor give a process the illusion that there is no concurrency. In contrast, Part II of this paper presents the approach of designing and verifying algorithms that work in the face of manifest concurrency.

Starting from some seemingly minimal assumptions about the nature of communication between asynchronous processes, the author proposes a classification of twelve partially-ordered kinds of single-writer shared registers. He provides constructions for implementing many of these classes from "weaker" ones, culminating in a multi-value, single-reader, atomic register. The constructions are proved both informally and using the formalism of Part I.

Much of the paper is of a theoretical nature. However, its ideas are worth study by system builders. For example, its algorithms and verification techniques could be of use in designing a "conventional" synchronization mechanism (e.g. a semaphore) for a multiprocessor system. A more exciting possibility would be to extend its approach to the design of a higher level concurrent algorithm such as taking a snapshot of an online database.

### Contents

| Ι  | Basic Formalism                                | 1  |

|----|------------------------------------------------|----|

| 1  | System Executions                              | 2  |

| 2  | Hierarchical Views                             | 6  |

| 3  | Systems                                        | 12 |

|    |                                                |    |

| II | f Algorithms                                   | 17 |

| 4  | The Nature of Asynchronous Communication       | 17 |

| 5  | The Constructions                              | 22 |

| 6  | Register Axioms                                | 31 |

| 7  | Correctness Proofs for the Constructions       | 38 |

|    | 7.1 Proof of Constructions 1, 2, and 3 $\dots$ | 38 |

|    | 7.2 Proof of Construction 4                    | 40 |

|    | 7.3 Proof of Construction 5                    |    |

| 8  | Conclusion                                     | 45 |

### Part I

### Basic Formalism

This paper addresses what I believe to be fundamental questions in the theory of interprocess communication. Part I develops a formal definition of what it means to implement one system with a lower-level one and provides a method for reasoning about concurrent systems. The definitions and axioms introduced here are applied in Part II to algorithms that implement certain interprocess communication mechanisms. Readers interested only in these mechanisms and not in the formalism can skip Part I and read only Sections 4 and 5 of Part II.

Most treatments of concurrent processing assume the existence of atomic operations—an atomic operation being one whose execution is performed as an indivisible action. The term operation is used to mean a class of actions such as depositing money in a bank account, and the term operation execution to mean one specific instance of executing such an action—for example, depositing \$100 in account number 14335 at 10:35 AM on December 14, 1987. Atomic operations must be implemented in terms of lower-level operations. A high-level language may provide a P operation to a semaphore as an atomic operation, but this operation must be implemented in terms of lower-level machine-language instructions. Viewed at the machine-language level, the semaphore operation is not atomic. Moreover, the machine-language operations must ultimately be implemented with circuits in which operations are manifestly nonatomic—the possibility of harmful "race conditions" shows that the setting and the testing of a flip-flop are not atomic actions.

Part II considers the problem of implementing atomic operations to a shared register with more primitive, nonatomic operations. Here, a more familiar example of implementing atomicity is used: concurrency control in a database. In a database system, higher-level transactions, which may read and modify many individual data items, are implemented with lower-level reads and writes of single items. These lower-level read and write operations are assumed to be atomic, and the problem is to make the higher-level transactions atomic. It is customary to say that a semaphore operation is atomic while a database transaction appears to be atomic, but this verbal distinction has no fundamental significance.

In database systems, atomicity of transactions is achieved by implementing a *serializable* execution order. The lower-level accesses performed by the

different transactions are scheduled so that the net effect is the same as if the transactions had been executed in some serial order—first executing all the lower-level accesses comprising one transaction, then executing all the accesses of the next transaction, and so on. The transactions should not actually be scheduled in such a serial fashion, since this would be inefficient; it is necessary only that the effect be the same as if that were done.<sup>1</sup>

In the literature on concurrency control in databases, serializability is usually the only correctness condition that is stated [1]. However, serializability by itself does not ensure correctness. Consider a database system in which each transaction either reads from or writes to the database, but does not do both. Moreover, assume that the system has a finite lifetime, at the end of which it is to be scrapped. Serializability is achieved by an implementation in which reads always return the initial value of the database entries and writes are simply not executed. This yields the same results as a serial execution in which one first performs all the read transactions and then all the writes. While such an implementation satisfies the requirement of serializability, no one would consider it to be correct.

This example illustrates the need for a careful examination of what it means for one system to implement another. It is reconsidered in Section 2, where the additional correctness condition needed to rule out this absurd implementation is stated.

### 1 System Executions

Almost all models of concurrent processes have indivisible atomic actions as primitive elements. For example, models in which a process is represented by a sequence or "trace" [11, 15, 16] assume that each element in the sequence represents an indivisible action. Net models [2] and related formalisms [10, 12] assume that the firing of an individual transition is atomic. These models are not appropriate for studying such fundamental questions as what it means to implement an atomic operation, in which the nonatomicity of operations must be directly addressed.

More conventional formalisms are therefore eschewed in favor of one introduced in [7] and refined in [6], in which the primitive elements are

<sup>&</sup>lt;sup>1</sup>In the context of databases, atomicity often denotes the additional property that a failure cannot leave the database in a state reflecting a partially completed transaction. In this paper, the possibility of failure is ignored, so no distinction between atomicity and serializability is made.

operation executions that are not assumed to be atomic. This formalism is described below; the reader is referred to [7] and [6] for more details.

A system execution consists of a set of operation executions, together with certain temporal precedence relations on these operation executions. Recall that an operation execution represents a single execution of some operation. When all operations are assumed to be atomic, an operation execution A can influence another operation execution B only if A precedes B—meaning that all actions of A are completed before any action of B is begun. In this case, one needs only a single temporal relation  $\longrightarrow$ , read "precedes", to describe the temporal ordering among operation executions. While temporal precedence is usually considered to be a total ordering of atomic operations, in distributed systems it is best thought of as an irreflexive partial ordering (see [8]).

Nonatomicity introduces the possibility that an operation execution A can influence an operation execution B without preceding it; it is necessary only that some action of A precede some action of B. Hence, in addition to the precedence relation  $\longrightarrow$ , one needs an additional relation  $-\rightarrow$ , read "can affect", where  $A - \rightarrow B$  means that some action of A precedes some action of B.

**Definition 1** A system execution is a triple  $\langle S, \longrightarrow, -- \rightarrow \rangle$ , where S is a finite or countably infinite set whose elements are called operation executions, and  $\longrightarrow$  and  $-- \rightarrow$  are precedence relations on S satisfying axioms A1-A5 below.

To assist in understanding the axioms for the  $\longrightarrow$  and  $-- \rightarrow$  relations, it is helpful to have a semantic model for the formalism. The model to be used is one in which an operation execution is represented by a set of primitive actions or events, where  $A \longrightarrow B$  means that all the events of A precede all the events of B, and  $A \longrightarrow B$  means that some event of A precedes some event of B. Letting E denote the set of all events, and  $\longrightarrow$  the temporal precedence relation among events, we get the following formal definition.

**Definition 2** A model of a system execution  $\langle S, \longrightarrow, --+ \rangle$  consists of a triple  $\mathbf{E}, \longrightarrow, \mu$ , where  $\mathbf{E}$  is a set,  $\longrightarrow$  is an irreflexive partial ordering on  $\mathbf{E}$ , and  $\mu$  is a mapping that assigns to each operation execution A of S a nonempty subset  $\mu(A)$  of  $\mathbf{E}$ , such that for every pair of operation executions A and B of S:

$$A \longrightarrow B \equiv \forall a \in \mu(A) : \forall b \in \mu(B) : a \longrightarrow b$$

$$A \longrightarrow B \equiv \exists a \in \mu(A) : \exists b \in \mu(B) : a \longrightarrow b \text{ or } a = b$$

(1)

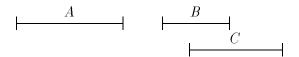

Figure 1: Three operation executions in a global-time model.

Note that the same symbol  $\longrightarrow$  denotes the "precedes" relation both between operation executions in S and between events in E.

Other than the existence of the temporal partial-ordering relation  $\longrightarrow$ , no assumption is made about the structure of the set of events  $\mathbf{E}$ . In particular, operation executions may be modeled as infinite sets of events. An important class of models is obtained by letting  $\mathbf{E}$  be the set of events in four-dimensional spacetime, with  $\longrightarrow$  the "happens before" relation of special relativity, where  $a \longrightarrow b$  means that it is temporally possible for event a to causally affect event b.

Another simple and useful class of models is obtained by letting  $\mathbf{E}$  be the real number line and representing each operation execution A as a closed interval.

**Definition 3** A global-time model of a system execution  $\langle \mathcal{S}, \longrightarrow, - \rightarrow \rangle$  is one in which **E** is the set of real numbers,  $\longrightarrow$  is the ordinary  $\langle$  relation, and each set  $\mu(A)$  is of the form  $[s_A, f_A]$  with  $s_A \langle f_A \rangle$ .

Think of  $s_A$  and  $f_A$  as the starting and finishing times of A. In a globaltime model,  $A \longrightarrow B$  means that A finishes before B starts, and  $A \dashrightarrow B$ means that A starts before (or at the same time as) B finishes. These relations are illustrated by Figure 1, where operation executions A, B, and C, represented by the three indicated intervals, satisfy:  $A \longrightarrow B$ ,  $A \longrightarrow C$ ,  $B \dashrightarrow C$ , and  $C \dashrightarrow B$ . (In this and similar figures, the number line runs from left to right, and overlapping intervals are drawn one above the other.)

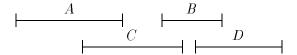

To complete Definition 1, the axioms for the precedence relations  $\longrightarrow$  and  $--\rightarrow$  of a system execution must be given. They are the following, where A, B, C, and D denote arbitrary operation executions in S. Axiom A4 is illustrated (in a global-time model) by Figure 2; the reader is urged to draw similar pictures to help understand the other axioms.

A1. The relation  $\longrightarrow$  is an irreflexive partial ordering.

A2. If

$$A \longrightarrow B$$

then  $A \longrightarrow B$  and  $B \longrightarrow A$ .

Figure 2: An illustration of Axiom A4.

A3. If

$$A \longrightarrow B \longrightarrow C$$

or  $A \longrightarrow B \longrightarrow C$  then  $A \longrightarrow C$ .

A4. If

$$A \longrightarrow B \longrightarrow C \longrightarrow D$$

then  $A \longrightarrow D$ .

A5. For any A, the set of all B such that  $A \longrightarrow B$  is finite.

(These axioms differ from the ones in [6] because only terminating operation executions are considered here.)

Axioms A1–A4 follow from (1), so they do not constrain the choice of a model. Axiom A5 does not follow from (1); it restricts the class of allowed models. Intuitively, A5 asserts that a system execution begins at some point in time, rather than extending into the infinite past. When **E** is the set of events in space-time, A5 holds for any model in which: (i) each operation occupies a finite region of space-time, (ii) any finite region of space-time contains only a finite number of operation executions, and (iii) the system is not expanding faster than the speed of light.<sup>2</sup>

Most readers will find it easiest to think about system executions in terms of a global-time model, and to interpret the relations  $\longrightarrow$  and  $--\rightarrow$  as indicated by the example in Figure 1. Such a mental model is adequate for most purposes. However, the reader should be aware that in a system execution having a global-time model, for any distinct operation executions A and B, either  $A \longrightarrow B$  or  $B \dashrightarrow A$ . (In fact, this is a necessary and sufficient condition for a system execution to have a global-time model [5].) However, in a system execution without a global-time model, it is possible for neither  $A \longrightarrow B$  nor  $B \dashrightarrow A$  to hold. As a trivial counterexample, let S consist of two elements and let the relations  $\longrightarrow$  and  $-\rightarrow$  be empty.

While a global-time model is a valuable aid to acquiring an intuitive understanding of a system, it is better to use more abstract reasoning when proving properties of systems. The relations  $\longrightarrow$  and  $-- \Rightarrow$  capture the essential temporal properties of a system execution, and A1-A5 provide the

<sup>&</sup>lt;sup>2</sup>A system expanding faster than the speed of light could have an infinite number of operation executions none of which are preceded by any operation.

necessary tools for reasoning about these relations. It has been my experience that proofs based upon these axioms are simpler and more instructive than ones that involve modeling operation executions as sets of events.

### 2 Hierarchical Views

A system can be viewed at different levels of detail, with different operation executions at each level. Viewed at the customer's level, a banking system has operation executions such as deposit \$1000. Viewed at the programmer's level, this same system executes operations such as  $dep\_amt[cust] := 1000$ . The fundamental problem of system building is to implement one system (like a banking system) as a higher-level view of another system (like a Pascal program).

A higher-level operation consists of a set of lower-level operations—the set of operations that implement it. Let  $\langle \mathcal{S}, - \to, - \to \rangle$  be a system execution and let  $\mathcal{H}$  be a set whose elements, called higher-level operation executions, are sets of operation executions from  $\mathcal{S}$ . A model for  $\langle \mathcal{S}, - \to, - \to \rangle$  represents each operation execution in  $\mathcal{S}$  by a set of events. This gives a representation of each higher-level operation execution H in  $\mathcal{H}$  as a set of events—namely, the set of all events contained in the representation of the lower-level operation executions that comprise H. This in turn defines precedence relations  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{\longrightarrow}$ , where  $G \stackrel{*}{\longrightarrow} H$  means that all events in (the representation of) G precede all events in H, and  $G \stackrel{*}{\longrightarrow} H$  means that some event in G precedes some event in G and G and G and G in G.

To express all this formally, let  $\mathbf{E}, \longrightarrow, \mu$  be a model for  $\langle \mathcal{S}, \longrightarrow, -- \rightarrow \rangle$ , define the mapping  $\mu^*$  on  $\mathcal{H}$  by

$$\mu^*(H) = \bigcup \{\mu(A) : A \in H\}$$

and define the precedence relations  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{\longrightarrow}$  on  $\mathcal{H}$  by

Using (1), it is easy to show that these precedence relations are the same ones obtained by the following definitions:

$$G \xrightarrow{*} H \equiv \forall A \in G : \forall B \in H : A \longrightarrow B$$

$$G \xrightarrow{*} H \equiv \exists A \in G : \exists B \in H : A \longrightarrow B \text{ or } A = B$$

(2)

Observe that  $\stackrel{*}{\longrightarrow}$  and  $-\stackrel{*}{\longrightarrow}$  are expressed directly in terms of the  $\longrightarrow$  and  $-\stackrel{*}{\longrightarrow}$  relations on  $\mathcal{S}$ , without reference to any model. We take (2) to be the definition of the relations  $\stackrel{*}{\longrightarrow}$  and  $-\stackrel{*}{\longrightarrow}$ .

For the triple  $\langle \mathcal{H}, \stackrel{*}{\longrightarrow}, \stackrel{*}{-} \stackrel{*}{\rightarrow} \rangle$  to be a system execution, the relations  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{-} \stackrel{*}{\rightarrow}$  must satisfy axioms A1-A5. If each element of  $\mathcal{H}$  is assumed to be a nonempty set of operation executions, then Axioms A1-A4 follow from (2) and the corresponding axioms for  $\longrightarrow$  and  $\stackrel{*}{-} \rightarrow$ . For A5 to hold, it is sufficient that each element of  $\mathcal{H}$  consist of a finite number of elements of  $\mathcal{S}$ , and that each element of  $\mathcal{S}$  belong to a finite number of elements of  $\mathcal{H}$ . Adding the natural requirement that every lower-level operation execution be part of some higher-level one, this leads to the following definition.

**Definition 4** A higher-level view of a system execution  $\langle S, - \rightarrow, - \rightarrow \rangle$  consists of a set  $\mathcal{H}$  such that:

- H1. Each element of  $\mathcal{H}$  is a finite, nonempty set of elements of  $\mathcal{S}$ .

- H2. Each element of S belongs to a finite, nonzero number of elements of H.

In most cases of interest,  $\mathcal{H}$  is a partition of  $\mathcal{S}$ , so each element of  $\mathcal{S}$  belongs to exactly one element of  $\mathcal{H}$ . However, Definition 4 allows the more general case in which a single lower-level operation execution is viewed as part of the implementation of more than one higher-level one.

Let us now consider what it should mean for one system to implement another. If the system execution  $\langle \mathcal{S}, -\to, -\to \rangle$  is an implementation of a system execution  $\langle \mathcal{H}, \stackrel{\mathcal{H}}{\longrightarrow}, -\stackrel{\mathcal{H}}{\longrightarrow} \rangle$ , then we expect  $\mathcal{H}$  to be a higher-level view of  $\mathcal{S}$ —that is, each operation in  $\mathcal{H}$  should consist of a set of operation executions of  $\mathcal{S}$  satisfying H1 and H2. This describes the elements of  $\mathcal{H}$ , but not the precedence relations  $\stackrel{\mathcal{H}}{\longrightarrow}$  and  $-\stackrel{\mathcal{H}}{\longrightarrow}$ . What should those relations be?

If we consider the operation executions in  $\mathcal{S}$  to be the "real" ones, and the elements of  $\mathcal{H}$  to be fictitious groupings of the real operation executions into abstract, higher-level ones, then the induced precedence relations  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{-}\stackrel{*}{\rightarrow}$  represent the "real" temporal relations on  $\mathcal{H}$ . These induced relations make the higher-level view  $\mathcal{H}$  a system execution, so they are an obvious choice for the relations  $\stackrel{\mathcal{H}}{\longrightarrow}$  and  $\stackrel{\mathcal{H}}{\longrightarrow}$ . However, as we shall see, they may not be the proper choice.

Let us return to the problem of implementing atomic database operations. Atomicity requires that, when viewed at the level at which the

Figure 3: An example with  $G \longrightarrow H$  and  $H \longrightarrow G$ .

operation executions are the transactions, the transactions appear to be executed sequentially. In terms of our formalism, the correctness condition is that, in any system execution  $\langle \mathcal{H}, \stackrel{\mathcal{H}}{\longrightarrow}, \stackrel{\mathcal{H}}{\longrightarrow} \rangle$  of the database system, all the elements of  $\mathcal{H}$  (the transactions) must be totally ordered by  $\stackrel{\mathcal{H}}{\longrightarrow}$ . This higher-level view of the database operations is implemented by lower-level operations that access individual database items. The higher-level system execution  $\langle \mathcal{H}, \stackrel{\mathcal{H}}{\longrightarrow}, \stackrel{\mathcal{H}}{\longrightarrow} \rangle$  must be implemented by a lower-level one  $\langle \mathcal{S}, \longrightarrow, - \rightarrow \rangle$  in which each transaction H in H is implemented by a set of lower-level operation executions in  $\mathcal{S}$ .

Suppose  $G = \{G_1, \ldots, G_m\}$  and  $H = \{H_1, \ldots, H_n\}$  are elements of  $\mathcal{H}$ , where the  $G_i$  and  $H_i$  are operation executions in  $\mathcal{S}$ . For  $G \stackrel{*}{\longrightarrow} H$  to hold, each  $G_i$  must precede  $(\longrightarrow)$  each  $H_j$ , and, conversely,  $H \stackrel{*}{\longrightarrow} G$  only if each  $H_j$  precedes each  $G_i$ . In a situation like the one in Figure 3, neither  $G \stackrel{*}{\longrightarrow} H$  nor  $H \stackrel{*}{\longrightarrow} G$  holds. (For a system with a global-time model, this means that both  $G \stackrel{*}{\longrightarrow} H$  and  $H \stackrel{*}{\longrightarrow} G$  hold.) If we required that the relations  $\stackrel{\mathcal{H}}{\longrightarrow}$  and  $\stackrel{\mathcal{H}}{\longrightarrow}$  be the induced relations  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{\longrightarrow}$ , then the only way to implement a serializable system, in which  $\stackrel{\mathcal{H}}{\longrightarrow}$  is a total ordering of the transactions, would be to prevent the type of interleaved execution shown in Figure 3. The only allowable system executions would be those in which the transactions were actually executed serially—each transaction being completed before the next one is begun.

Serial execution is, of course, too stringent a requirement because it prevents the concurrent execution of different transactions. We merely want to require that the system behave as if there were a serial execution. To show that a given system correctly implements a serializable database system, one specifies both the set of lower-level operation executions corresponding to each higher-level transaction and the precedence relation  $\xrightarrow{\mathcal{H}}$  that describes the "as if" order, where the transactions act as if they had occurred in that order. This order must be consistent with the values read from the database—each read obtaining the value written by the most recent write of that item, where "most recent" is defined by  $\xrightarrow{\mathcal{H}}$ .

As was observed in the introduction, the condition that a read obtain a

value consistent with the ordering of the operations is not the only condition that must be placed upon  $\xrightarrow{\mathcal{H}}$ . For the example in which each transaction either reads from or writes to the database, but does not do both, we must rule out an implementation that throws writes away and lets a read return the initial values of the database entries—an implementation that achieves serializability with a precedence relation  $\xrightarrow{\mathcal{H}}$  in which all the read transactions precede all the write transactions. Although this implementation satisfies the requirement that every read obtain the most recently written value, this precedence relation is absurd because a read is defined to precede a write that may really have occurred years earlier.

Why is such a precedence relation absurd? In a real system, these database transactions may occur deep within the computer; we never actually see them happen. What is wrong with defining the precedence relation  $\xrightarrow{\mathcal{H}}$  to pretend that these operation executions happened in any order we wish? After all, we are already pretending, contrary to fact, that the operations occur in some serial order.

In addition to reads and writes to database items, real systems perform externally observable operation executions such as printing on terminals. By observing these operation executions, we can infer precedence relations among the internal reads and writes. We need some condition on  $\xrightarrow{\mathcal{H}}$  and  $\xrightarrow{\mathcal{H}}$  to rule out precedence relations that contradict such observations.

It is shown below that these contradictions are avoided by requiring that if one higher-level operation execution "really" precedes another, then that precedence must appear in the "pretend" relations. Remembering that  $\stackrel{*}{\longrightarrow}$  and  $\stackrel{*}{\longrightarrow}$  are the "real" precedence relations and  $\stackrel{\mathcal{H}}{\longrightarrow}$  and  $\stackrel{\mathcal{H}}{\longrightarrow}$  are the "pretend" ones, this leads to the following definition.

**Definition 5** A system execution  $\langle S, \longrightarrow, - \rightarrow \rangle$  implements a system execution  $\langle \mathcal{H}, \xrightarrow{\mathcal{H}}, -\xrightarrow{\mathcal{H}} \rangle$  if  $\mathcal{H}$  is a higher-level view of S and the following condition holds:

H3. For any

$$G, H \in \mathcal{H}$$

: if  $G \xrightarrow{*} H$  then  $G \xrightarrow{\mathcal{H}} H$ , where  $\xrightarrow{*}$  is defined by (2).

One justification for this definition in terms of global-time models is given by the following proposition, which is proved in [5]. (Recall that a global-time model is determined by the mapping  $\mu$ , since the set of events and their ordering is fixed.)

Figure 4: An illustration of Proposition 1.

**Proposition 1** Let  $\langle S, \longrightarrow, -- \rightarrow \rangle$  and  $\langle S, \stackrel{\prime}{\longrightarrow}, -\stackrel{\prime}{\longrightarrow} \rangle$  be system executions, both of which have global-time models, such that for any  $A, B \in S: A \longrightarrow B$  implies  $A \stackrel{\prime}{\longrightarrow} B$ . For any global-time model  $\mu$  of  $\langle S, \longrightarrow, -- \rightarrow \rangle$  there exists a global-time model  $\mu'$  of  $\langle S, \stackrel{\prime}{\longrightarrow}, -\stackrel{\prime}{\longrightarrow} \rangle$  such that  $\mu'(A) \subseteq \mu(A)$  for every A in S.

This proposition is illustrated in Figure 4, where: (i)  $\mathcal{S} = \{A, B, C\}$ , (ii)  $A \longrightarrow C$  is the only  $\longrightarrow$  relation, and (iii)  $B \xrightarrow{\prime} A \xrightarrow{\prime} C$ . To apply Proposition 1 to Definition 5, substitute  $\mathcal{S}$  for  $\mathcal{H}$ , substitute  $\xrightarrow{*}$  and  $-\overset{*}{\rightarrow}$  for  $\longrightarrow$  and  $-\overset{*}{\rightarrow}$ , and substitute  $\xrightarrow{\mathcal{H}}$  and  $-\overset{\mathcal{H}}{\rightarrow}$  for  $\xrightarrow{\prime}$  and  $-\overset{\prime}{\rightarrow}$ . The proposition then states that the "pretend" precedence relations are obtained from the real ones by shrinking the time interval during which the operation execution is considered to have occurred.

Let us return to the example of implementing a serializable database system. The formal requirement is that any system execution  $\langle \mathcal{S}, -\to, -\to \rangle$ , whose operation executions consist of reads and writes of individual database items, must implement a system  $\langle \mathcal{H}, \stackrel{\mathcal{H}}{\longrightarrow}, -\stackrel{\mathcal{H}}{\longrightarrow} \rangle$ , whose operations are database transactions, such that  $\stackrel{\mathcal{H}}{\longrightarrow}$  is a total ordering of  $\mathcal{H}$ . By Proposition 1, this means that not only must the transactions be performed as if they had been executed in some sequential order, but that this order must be one that could have been obtained by executing each transaction within some interval of time during the period when it actually was executed. This rules out the absurd implementation described above, which implies a precedence relation  $\stackrel{\mathcal{H}}{\longrightarrow}$  that makes writes come long after they actually occurred.

Another justification for Definition 5 is derived from the following result, which is proved in [5]. Its statement relies upon the obvious fact that if  $\langle \mathcal{S}, - , - , - , - \rangle$  is a system execution, then  $\langle \mathcal{T}, - , - , - , - \rangle$  is also a system execution for any subset  $\mathcal{T}$  of  $\mathcal{S}$ . (The symbols  $\longrightarrow$  and  $- \rightarrow$  denote both the relations on  $\mathcal{S}$  and their restrictions to  $\mathcal{T}$ . Also, in the proposition, the set  $\mathcal{T}$  is identified with the set of all singleton sets  $\{A\}$  for  $A \in \mathcal{T}$ .)

**Proposition 2** Let  $S \cup T$ ,  $\longrightarrow$ ,  $-\rightarrow$  be a system execution, where S and T are disjoint; let  $\langle S, \longrightarrow, -\rightarrow \rangle$  be an implementation of a system execution  $\langle \mathcal{H}, \frac{\mathcal{H}}{\longrightarrow}, -\frac{\mathcal{H}}{\rightarrow} \rangle$ ; and let  $\stackrel{*}{\longrightarrow}$  and  $-\stackrel{*}{\longrightarrow}$  be the relations defined on  $\mathcal{H} \cup T$  by (2). Then there exist precedence relations  $\stackrel{\mathcal{H}T}{\longrightarrow}$  and  $\stackrel{\mathcal{H}T}{\longrightarrow}$  such that:

- $\mathcal{H} \cup \mathcal{T}, \xrightarrow{\mathcal{H}\mathcal{T}}, \xrightarrow{\mathcal{H}\mathcal{T}}$  is a system execution that is implemented by  $\mathcal{S} \cup \mathcal{T}, \longrightarrow, -- \rightarrow$ .

- The restrictions of  $\xrightarrow{\mathcal{H}T}$  and  $\xrightarrow{\mathcal{H}T}$  to  $\mathcal{H}$  equal  $\xrightarrow{\mathcal{H}}$  and  $\xrightarrow{\mathcal{H}}$ , respectively.

- The restrictions of

→ and → and → to T are extensions of the relations

→ and → →, respectively.

To illustrate the significance of this proposition for Definition 5, let  $\langle S, -\to, -\to \rangle$  be a system execution of reads and writes to database items that implements a higher-level system execution  $\langle \mathcal{H}, \frac{\mathcal{H}}{\to}, -\frac{\mathcal{H}}{\to} \rangle$  of database transactions. The operation executions of S presumably occur deep inside the computer and are not directly observable. Let  $\mathcal{T}$  be the set of all other operation executions in the system, including the externally observable ones. Proposition 2 means that, while the "pretend" precedence relations  $\stackrel{\mathcal{H}}{\to}$  and  $\stackrel{\mathcal{H}}{\to}$  may imply new precedence relations on the operation executions in  $\mathcal{T}$ , these relations ( $\stackrel{\mathcal{H}}{\to}$  and  $\stackrel{\mathcal{H}}{\to}$ ) are consistent with the "real" precedence relations  $\stackrel{*}{\to}$  and  $\stackrel{*}{\to}$  on  $\mathcal{T}$ . Thus, pretending that the database transactions occur in the order given by  $\stackrel{\mathcal{H}}{\to}$  does not contradict any of the real, externally observable orderings among the operations in  $\mathcal{T}$ .

When implementing a higher-level system, one usually ignores all operation executions that are not part of the implementation. For example, when implementing a database system, one considers only the transactions that access the database, ignoring the operation executions that initiate the transactions and use their results. This is justified by Proposition 2, which shows that the implementation cannot lead to any anomalous precedence relations among the operation executions that are being ignored.

A particularly simple kind of implementation is one in which each higherlevel operation execution is implemented by a single lower-level one.

**Definition 6** An implementation  $\langle S, - \rightarrow, - \rightarrow \rangle$  of  $\langle \mathcal{H}, \xrightarrow{\mathcal{H}}, - \xrightarrow{\mathcal{H}} \rangle$  is said to be trivial if every element of  $\mathcal{H}$  is a singleton set.

In a trivial implementation, the sets  $\mathcal{S}$  and  $\mathcal{H}$  are (essentially) the same; the two system executions differ only in their precedence relations. A trivial implementation is one that is not an implementation in the ordinary sense, but merely involves choosing new precedence relations ("as if" temporal relations).

### 3 Systems

A system execution has been defined, but not a system. Formally, a system is just a set of system executions—a set that represents all possible executions of the system.

#### **Definition 7** A system is a set of system executions.

The usual method of describing a system is with a program written in some programming language. Each execution of such a program describes a system execution, and the program represents the system consisting of the set of all such executions. When considering communication and synchronization properties of concurrent systems, the only operation executions that are of interest are ones that involve interprocess communication—for example, the operations of sending a message or reading a shared variable. Internal "calculation" steps can be ignored. If x, y, and z are shared variables and a is local to the process in question, then an execution of the statement x := y + a \* z includes three operation executions of interest: a read of y, a read of z, and a write of x. The actions of reading a, computing the product, and computing the sum are independent of the actions of other processes and could be considered to be either separate operation executions or part of the operation that writes the new value of x. For analyzing the interaction among processes, what is significant is that each of the two reads precedes  $(-\rightarrow)$  the write, and that no precedence relation is assumed between the two reads (assuming that the programming language does not specify an evaluation order within expressions).

A formal semantics for a programming language can be given by defining, for each syntactically correct program, the set of all possible executions. This is done by recursively defining a succession of lower and lower higher-level views, in which each operation execution represents a single execution of a syntactic program unit.<sup>3</sup> At the highest-level view, a system execution

<sup>&</sup>lt;sup>3</sup>For nonterminating programs, the formalism must be extended to allow nonterminating higher-level operation executions, each one consisting of an infinite set of lower-level

consists of a single operation execution that represents an execution of the entire program. A view in which an execution of the statement S;T is a single operation execution is refined into one in which an execution consists of an execution of S followed by (---) an execution of  $T.^4$  While this kind of formal semantics may be useful in studying subtle programming language issues, it is unnecessary for the simple language constructs generally used in describing synchronization algorithms like the ones in Part II, so these ideas will just be employed informally.

Having defined what a system is, the next step is to define what it means for a system S to implement a higher-level system H. The higher-level system H can be regarded as a specification of the lower-level one S, so we must decide what it should mean for a system to meet a specification.

The system executions of **S** involve lower-level concepts such as program variables; those of **H** involve higher-level concepts such as transactions. The first thing we need is some way of interpreting a "concrete" system execution  $\langle \mathcal{S}, \longrightarrow, -- \rightarrow \rangle$  of the "real" implementation **S** as an "abstract" execution of the "imaginary" high-level system **H**. Thus, there must be some mapping  $\iota$  that assigns to any system execution  $\langle \mathcal{S}, \longrightarrow, -- \rightarrow \rangle$  of **S** a higher-level system execution  $\iota(\langle \mathcal{S}, \longrightarrow, -- \rightarrow \rangle)$  that it implements. The implementation **S**, which is a set of system executions, yields a set  $\iota(\mathbf{S})$  of higher-level system executions. What should be the relation between  $\iota(\mathbf{S})$  and **H**?

There are two distinct approaches to specification, which may be called the *prescriptive* and *restrictive* approaches. The prescriptive approach is generally employed by methods in which a system is specified with a high-level program, as in [10] and [12]. An implementation must be equivalent to the specification in the sense that it exhibits all the same possible behaviors as the specification. In the prescriptive approach, one requires that every possible execution of the specification  $\mathbf{H}$  be represented by some execution of  $\mathbf{S}$ , so  $\iota(\mathbf{S})$  must equal  $\mathbf{H}$ .

The restrictive approach is employed primarily by axiomatic methods, in which a system is specified by stating the properties it must satisfy. Any implementation that satisfies those properties is acceptable; it is not necessary for the implementation to allow all possible behaviors that satisfy the properties. If **H** is the set of all system executions satisfying the required properties, then the restrictive approach requires only that every execution

operation executions.

<sup>&</sup>lt;sup>4</sup>In the general case, we must also allow the possibility that an execution of S; T consists of a nonterminating execution of S.

of S represent some execution of H, so  $\iota(S)$  must be contained in H.

To illustrate the difference between the two approaches, consider the problem of implementing a program containing the statement x := y + a \* z with a lower-level machine-language program. The statement does not specify in which order y and z are to be read, so  $\mathbf{H}$  should contain executions in which y is read before z, executions in which z is read before y, as well as ones in which they are read concurrently. With the prescriptive approach, a correct implementation would have to allow all of these possibilities, so a machine-language program that always reads y first then z would not be a correct implementation. In the restrictive approach, this is a perfectly acceptable implementation because it exhibits one of the allowed possibilities.

The usual reason for not specifying the order of evaluation is to allow the compiler to choose any convenient order, not to require that it produce nondeterministic object code. I therefore find the restrictive approach to be the more natural and adopt it in the following definition.

**Definition 8** The system **S** implements a system **H** if there is a mapping  $\iota : \mathbf{S} \mapsto \mathbf{H}$  such that, for every system execution  $\langle \mathcal{S}, -\rightarrow, -\rightarrow \rangle$  in **S**,  $\langle \mathcal{S}, -\rightarrow, -\rightarrow \rangle$  implements  $\iota(\langle \mathcal{S}, -\rightarrow, -\rightarrow \rangle)$ .

In taking the restrictive approach, one faces the question of how to specify that the system must actually do anything. The specification of a banking system must allow a possible system execution in which no customers happen to use an automatic teller machine on a particular afternoon, and it must include the possibility that a customer will enter an invalid request. How can we rule out an implementation in which the machine simply ignores all customer requests during an afternoon, or interprets any request as an invalid one?

The answer lies in the concept of an interface specification, discussed in [9]. The specification must explicitly describe how certain interface operations are to be implemented; their implementation is not left to the implementor. The interface specification for the bank includes a description of what sequences of keystrokes at the teller machine constitute valid requests, and the set of system executions only includes ones in which every valid request is serviced. What it means for someone to use the machine is part of the interface specification, so the possibility of no one using the machine on some afternoon does not allow the implementation to ignore someone who does use it.

Part II considers only the internal operations that effect communication between processes within the system, not the interface operations that effect communication between the system and its environment. Therefore, the interface specification is not considered further. The reader is referred to [9] for a discussion of this subject.

### Part II

# Algorithms

Part I describes a formalism for specifying and reasoning about concurrent systems. Here in Part II, communication between asynchronous processes in a concurrent system is studied. The next section explains why the problem of achieving asynchronous interprocess communication may be viewed as one of implementing shared registers, and the following section describes algorithms for doing this. These two sections are informal, and may be read without having read the formalism of Part I. The concepts introduced in Section 4 are formally defined in Section 6, and formal correctness proofs of the algorithms of Section 5 are given in Section 7. These latter two sections assume knowledge of the material in Part I.

### 4 The Nature of Asynchronous Communication

All communication ultimately involves a communication medium whose state is changed by the sender and observed by the receiver. A sending processor changes the voltage on a wire and a receiving processor observes the voltage change; a speaker changes the vibrational state of the air and a listener senses this change.

There are two kinds of communication acts: transient and persistent. In a transient communication act, the medium's state is changed only for the duration of the act, immediately afterwards reverting to its "normal" state. A message sent on an Ethernet modifies the transmission medium's state only while the message is in transit; the altered state of the air lasts only while the speaker is talking. In a persistent communication act, the state change remains after the sender has finished its communication. Setting a voltage level on a wire, writing on a blackboard, and raising a flag on a flagpole are all examples of persistent communication.

Transient communication is possible only if the receiver is observing the communication medium while the sender is modifying it. This implies an a priori synchronization—the receiver must be waiting for the communication to take place. Communication between truly asynchronous processes must be persistent, the sender changing the state of the medium and the receiver able to sense that change at a later time.

At a low level, message passing is often considered to be a form of tran-

sient communication between asynchronous processes. However, a closer examination of asynchronous message passing reveals that it involves a persistent communication. Messages are placed in a buffer that is periodically tested by the receiver. Viewed at a low level, message passing is typically accomplished by putting a message in a buffer and setting an interrupt bit that is tested on every machine instruction. The receiving process actually consists of two asynchronous subprocesses: a main process that is usually thought of as the receiver, and an input process that continuously monitors the communication medium and transfers messages from the medium to the buffer. The input process is synchronized with the sender (it is a "slave" process) and communicates asynchronously with the main process, using the buffer as a medium for persistent communication.

The subject of this paper is asynchronous interprocess communication, so only persistent communication is considered. Moreover, attention is restricted to unidirectional communication, in which only a single process can modify the state of the medium. (With this restriction, two-way communication requires at least two separate communication media, one modified by each process.) However, multiple receivers will be considered. Also, only discrete systems, in which the medium has a finite number of distinguishable states, are considered. A receiver is assumed always to obtain one of these discrete values. The sender can therefore set the medium to one of a fixed number of persistent states, and the receiver(s) can observe the medium's state.

This form of persistent communication is more commonly known as a shared register, where the sender and receiver are called the *writer* and *reader*, respectively, and the state of the communication medium is known as the *value* of the register. These terms are used in the rest of this paper, which therefore considers finite-valued registers with a single writer and one or more readers.

In assuming a single writer, the possibility of concurrent writes (to the same register) is ruled out. Since a reader only senses the value of the register, there is no reason why a read operation must interfere with another read or write operation. (While reads do interfere with other operations in some forms of memory, such as magnetic core, this interference is an idiosyncrasy of the particular technology rather than an inherent property of reading.) A read is therefore assumed not to affect any other read or any write. However, it is not clear what effect a concurrent write should have on a read.

In concurrent programming, one traditionally assumes that a writer has

exclusive access to shared data, making concurrent reading and writing impossible. This assumption is enforced either by requiring the programming language to provide the necessary exclusive access, or by implementing the exclusion with a "readers-writers" protocol [3]. Such an approach requires that a reader wait while a writer is accessing the register, and vice versa. Moreover, any method for achieving such exclusive access, whether implemented by the programmer or the compiler, requires a lower-level shared register. At some level, the problem of concurrent access to a shared register must be faced. It is this problem that is addressed by this paper; any approach that requires one process to wait for another is eschewed.

Asynchronous concurrent access to shared registers is usually considered only at the hardware level, so it is at this level that the methods developed here could have some direct application. However, concurrent access to shared data also occurs at higher levels of abstraction. One cannot allow any single process exclusive access to the entire Social Security system's database. While algorithms for implementing a single register cannot be applied to such a database, I hope that insight obtained from studying these algorithms will eventually lead to new methods for higher-level data sharing. Nevertheless, when reading this paper, it is best to think of a register as a low-level component, probably implemented in hardware.

Hardware implementations of asynchronous communication often make assumptions about the relative speeds of the communicating processes. Such assumptions can lead to simplifications. For example, the problem of constructing an atomic register, discussed below, is shown to be easily solved by assuming that two successive reads of a register cannot be concurrent with a single write. If one knows how long a write can take, a delay can be added between successive reads to ensure that this assumption holds. No such assumptions are made here about process speeds. The results therefore apply even to communication between processes of vastly differing speeds.

Writes cannot overlap (be concurrent with) one another because there is only one writer, and overlapping reads are assumed not to affect one another, so the only case left to consider is a read overlapping one or more writes. Three possible assumptions about what can happen in this case are considered.

The weakest possibility is a *safe* register, in which it is assumed only that a read not concurrent with any write obtains the correct value—that is, the most recently written one. No assumption is made about the value obtained by a read that overlaps a write, except that it must obtain one of the possible values of the register. Thus, if a safe register may assume

Figure 5: Two writes and three reads.

the values 1, 2, and 3, then any read must obtain one of these three values. A read that overlaps a write operation that changes the value from 1 to 2 could obtain any of these values, including 3.

The next stronger possibility is a regular register, which is safe (a read not concurrent with a write gets the correct value) and in which a read that overlaps a write obtains either the old or new value. For example, a read that overlaps a write that changes the value from 1 to 3 may obtain either 1 or 3, but not 2. More generally, a read that overlaps any series of writes obtains either the value before the first of the writes or one of the values being written.

The final possibility is an *atomic* register, which is safe and in which reads and writes behave as if they occur in some definite order. In other words, for any execution of the system, there is some way of totally ordering the reads and writes so that the values returned by the reads are the same as if the operations had been performed in that order, with no overlapping. (The precise formal condition was developed in Section 2 of Part I.)

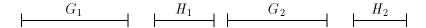

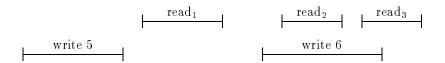

The difference between the three kinds of registers is illustrated by Figure 5, which shows five operations to a register that may assume the three values 5, 6, and 27. The duration of each operation is indicated by a line segment, where time runs from left to right. A write of the value 5 precedes all other operations, including a subsequent write of 6. There are three successive reads, denoted read<sub>1</sub>, read<sub>2</sub>, and read<sub>3</sub>.

For a safe register, read<sub>1</sub> obtains the value 5, since a read that does not overlap a write must obtain the most recently written value. However, the other two reads, which overlap the second write, may obtain 5, 6, or 27.

With a regular register, read<sub>1</sub> must again obtain the value 5, since a regular register is also safe. Each of the other two reads may obtain either a 5 or a 6, but not a 27. In particular, read<sub>2</sub> could obtain a 6 and read<sub>3</sub> a 5.

With an atomic register, read<sub>1</sub> must also obtain the value 5 and the other two reads may obtain the following pairs of values:

| $read_2$ | $_{ m read_3}$ |

|----------|----------------|

| 5        | 5              |

| 5        | 6              |

| 6        | 6              |

For example, the pair of values 5,6 represents a situation in which the operations act as if the first read preceded the write of 6 and the second read followed it. However, unlike a regular register, an atomic register does not admit the possibility of read<sub>2</sub> obtaining the value 6 and read<sub>3</sub> obtaining 5. In general, if two successive reads overlap the same write, then a regular register allows the first read to obtain the new value and the second read the old value, while this is forbidden with an atomic register. In fact, Proposition 5 of Section 6 essentially states that a regular register is atomic if two successive reads that overlap the same write cannot obtain the new then the old value. Thus, a regular register is automatically an atomic one if two successive reads cannot overlap the same write.

These are the only three general classes of register that I have been able to think of. Each class merits study. Safeness<sup>5</sup> seems to be the weakest requirement that allows useful communication; I do not know how to achieve any form of interprocess synchronization with a weaker assumption. Regularity asserts that a read returns a "reasonable" value, and seems to be a natural requirement. Atomicity is the most common assumption made about shared registers, and is provided by current multiport computer memories.<sup>6</sup> At a lower level, such as interprocess communication within a single chip, only safe registers are provided; other classes of register must be implemented using safe ones.

Any method of implementing a single-writer register can be classified by three "coordinates" with the following values:

- safe, regular, or atomic, according to the strongest assumption that the register satisfies.

- boolean or multivalued, according to whether the method produces only boolean registers or registers with any desired number of values.

$<sup>^5{</sup>m The~term}$  "safeness" is used because "safety" already has a technical meaning for concurrent programs.

<sup>&</sup>lt;sup>6</sup>However, the standard implementation of a multiport memory does not meet my requirements for an asynchronous register because, if two processes concurrently access a memory cell, one must wait for the other.

• single-reader or multireader, according to whether the method yields registers with only one reader or with any desired number of readers.

This produces twelve classes of implementations, partially ordered by "strength"—for example, a method that produces atomic, multivalued, multireader registers is stronger than one producing regular, multivalued, single-reader registers. This paper addresses the problem of implementing a register of one class using one or more registers of a weaker class.

The weakest class of register, and therefore the easiest to implement, is a safe, boolean, single-reader one. This seems to be the most natural kind of register to implement with current hardware technology, requiring only that the writer set a voltage level either high or low and that the reader test this level without disturbing it. A series of constructions of stronger registers from weaker ones is presented that allows almost every class of register to be constructed starting from this weakest class. The one exception is that constructing an atomic, multireader register from any weaker one is still an open problem. Most of the constructions are simple; the difficult ones are Construction 4 that implements an m-reader, multivalued, regular register using m-reader, boolean, regular registers, and Construction 5 that implements a single-reader, multivalued, atomic register using single-reader, multivalued, regular registers.

#### 5 The Constructions

In this section, the algorithms for constructing different classes of registers are described and informally justified. Rigorous correctness proofs are post-poned until Section 7.

The algorithms are described by indicating how a write and a read are performed. For most of them, the initial state is not indicated—it is the one that would result from writing the initial value starting from any arbitrary state.

The first construction implements a multireader safe or regular register from single-reader ones. It uses the obvious method of having the writer maintain a separate copy of the register for each reader. The **for all** statement denotes that its body is executed once for each of the indicated values of i; these separate executions can be done in any order or concurrently.

<sup>&</sup>lt;sup>7</sup>This is only safe and not regular if, for example, setting a level high when it is already high can cause a perturbation of the level.

Construction 1 Let  $v_1, \ldots, v_m$  be single-reader, n-valued registers, where each  $v_i$  can be written by the same writer and read by process i, and construct a single n-valued register v in which the operation  $v := \mu$  is performed as follows:

for all

$$i$$

in  $\{1,\ldots,m\}$  do  $v_i := \mu$  od

and process i reads v by reading the value of  $v_i$ . If the  $v_i$  are safe or regular registers, then v is a safe or regular register, respectively.

The proof of correctness for this construction runs as follows. Any read by process i that does not overlap a write of v does not overlap a write of  $v_i$ . If  $v_i$  is safe, then this read gets the correct value, which shows that v is safe. If a read of  $v_i$  by process i overlaps a write of  $v_i$ , then it overlaps the write of the same value to v. This implies that if  $v_i$  is regular, then v is also regular.

Construction 1 does not make v an atomic register even if the  $v_i$  are atomic. If reads by two different processes i and j both overlap the same write, it is possible for i to get the new value and j the old value even though the read by i precedes the read by j—a possibility not allowed by an atomic register.

The next construction is also trivial; it implements an n-bit safe register from n single-bit ones.

**Construction 2** Let  $v_1, \ldots, v_n$  be boolean m-reader registers, each written by the same writer and read by the same set of readers. Let v be the  $2^n$ -valued, m-reader register in which the number with binary representation  $\mu_1 \ldots \mu_n$  is written by

for all

$$i$$

in  $\{1,\ldots,m\}$  do  $v_i := \mu_i$  od

and in which the value is read by reading all the  $v_i$ . If each  $v_i$  is safe, then v is safe.

This construction yields a safe register because, by definition, a read does not overlap a write of v only if it does not overlap a write of any of the  $v_i$ , in which case it obtains the correct values. The register v is not regular even if the  $v_i$  are. A read can return any value if it overlaps a write that changes the register's value from 0...0 to 1...1.

The next construction shows that it is trivial to implement a boolean regular register from a safe boolean register. In a safe register, a read that

overlaps a write may get any value, while in a regular register it must get either the old or new value. However, a read of a safe boolean register must obtain either true or false on any read, so it must return either the old or new value if it overlaps a write that changes the value. A boolean safe register can fail to be regular only if a read that overlaps a write that does not change the value returns the other value—for example, writing the value true when the current value equals true could cause an overlapping read to obtain the value false. To prevent this possibility, one simply does not perform a write that does not change the value.

Construction 3 Let v be an m-reader boolean register, and let x be a variable internal to the writer (not a shared register) initially equal to the initial value of v. Define  $v^*$  to be the m-reader boolean register in which the write operation  $v^* := \mu$  is performed as follows:

if

$$x \neq \mu$$

then  $v := \mu$ ;

$x := \mu$  fi

and a read of  $v^*$  is performed by reading v. If v is safe then  $v^*$  is regular.

There are two known algorithms for implementing a multivalued regular register from boolean ones. The simpler one is given as Construction 4; the second one is described later. Construction 4 employs a unary encoding, in which the value  $\mu$  is denoted by zeros in bits 0 through  $\mu - 1$  and a one in bit  $\mu$ . A reader reads the bits from left to right (0 to n) until it finds a one. To write the value  $\mu$ , the writer first sets  $v_{\mu}$  to one and then sets bits  $\mu - 1$  through 1 to zero, writing from right to left. (While this algorithm has never before been published, the idea of implementing shared data by reading and writing its components in different directions was also used in [4].8)

**Construction** 4 Let  $v_1, \ldots, v_n$  be boolean, m-reader registers, and let v be the n-valued, m-reader register in which the operation  $v := \mu$  is performed by

$$v_{\mu} := 1;$$

for  $i := \mu - 1$  step  $-1$  until  $1$  do  $v_i := 0$  od

<sup>&</sup>lt;sup>8</sup>Although the algorithms in [4] require only that the registers be regular, the assumption of atomicity was added because the editor felt that nonatomicity at the level of individual bits was too radical a concept to appear in *Communications of the ACM*.

and a read is performed by:

```

\mu := 1;

while v_{\mu} = 0 do \mu := \mu + 1 od;

return \mu

```

If each  $v_i$  is regular, then v is regular.

The correctness of this algorithm is not at all obvious. Indeed, it is not even obvious that the **while** loop in the read operation does not "fall off the end" and try to read the nonexistent register  $v_{n+1}$ . This can't happen because, whenever the writer writes a zero, there is a one to the right of it. (Since an initial value is assumed to have been written, some  $v_i$  initially equals one.) As an exercise, the reader of this paper can convince himself that, whenever a reading process sees a one, it was written by either a concurrent write or by the most recent preceding one, so v is regular. The formal proof is given in Section 7.

The value of  $v_n$  is only set to one, never to zero. It can therefore be eliminated; the writer simply never writes it and the reader assumes its value is one instead of reading it.

Even if all the  $v_i$  are atomic, Construction 4 does not produce an atomic register. To see this, suppose that the register initially has the value 3, so  $v_1 = v_2 = 0$  and  $v_3 = 1$ , the writer first writes the value 1 then the value 2, and there are two successive read operations. This can produce the following sequence of actions:

- the first read finds  $v_1 = 0$

- the first write sets  $v_1 := 1$

- the second write sets  $v_2 := 1$

- the first read finds  $v_2 = 1$  and returns the value 2

- the second read finds  $v_1 = 1$  and returns the value 1.

In this scenario, the first read obtains a newer value (the one written by the second write) than the second read (which obtains the one written by the first write), even though it precedes the second read. This shows that the register is not atomic.

Construction 4 uses n-1 boolean regular registers to make an n-valued one, so it is practical only for small values of n. One would like an algorithm that requires  $O(\log n)$  boolean registers to construct an n-valued

register. The second method for constructing a regular multivalued register uses an algorithm of Peterson [14] that implements an m-reader, n-valued, atomic register with m+2 safe, m-reader, n-valued registers; 2m atomic, boolean, one-reader registers; and two atomic, boolean m-reader registers. However, there is no known algorithm for constructing the atomic, m-reader registers required by Peterson's algorithm from simpler ones. Nevertheless, we can apply his algorithm to construct an n-valued, single-reader, atomic register using three safe, single-reader, n-valued registers and four single-reader, atomic, boolean registers. The safe registers can be implemented with Construction 2, and the atomic boolean registers can be implemented with Construction 5 below. Since an atomic register is regular, Construction 1 can then be used to make an m-reader, n-valued, regular register from  $O(3m\log n)$  single-reader, boolean, regular registers.

Before giving the algorithm for constructing a two-reader atomic register, a result is proved that indicates why no trivial algorithm will work. It asserts that there can be no algorithm in which the writer only writes and the reader only reads; any algorithm must involve two-way communication between the reader and the writer.

**Theorem:** There exists no algorithm to implement an atomic register using a finite number of regular registers that can be written only by the writer (of the atomic register).

Proof: We assume such an algorithm and derive a contradiction. Any algorithm that uses multiple registers can be replaced by one in which these registers are combined into a single large register. A read in the original algorithm is replaced by one that reads all the combined register and ignores the other components; a write in the original algorithm is replaced by one that changes only the desired component of the combined register. (This is possible because there is only a single writer.) Therefore, without loss of generality, we can assume that there is only a single regular register v written by the writer and read by the reader.

Let  $v^*$  denote the atomic register that is being implemented. Since the algorithm must work if the writer never stops writing, we may suppose that the writer performs an infinite number of writes that change the value of  $v^*$ . There must be some pair of values assumed by  $v^*$ , call them 0 and 1, such that there are an infinite number of writes that change  $v^*$ 's value from 0 to 1. Since v can assume only a finite number of values (the hypothesis states that the original algorithm has only a finite number of registers, and

all registers are taken to have only a finite number of possible values), there must exist values  $v_0, \ldots, v_n$  of v such that: (i)  $v_0$  is the final value of v after each one of an infinite number of writes of 0 to  $v^*$ , (ii)  $v_n$  is the final value of v after each one of an infinite number of writes of 1 to  $v^*$ , and (iii) for each i < n, the value of v is changed from  $v_i$  to  $v_{i+1}$  during infinitely many writes that change the value of  $v^*$  from 0 to 1.9

A read of  $v^*$  may involve several reads of v. However, in our quest for a contradiction, we may restrict our attention to scenarios in which each of those reads of v obtains the same value, so we may assume that each read of  $v^*$  reads v only once. Since v assumes each value  $v_i$  infinitely often, it must be possible for a sequence of n+1 consecutive reads of v to obtain the values  $v_n, v_{n-1}, \ldots, v_0$ .

The read that finds v equal to  $v_i$  and the subsequent read that finds v equal to  $v_{i-1}$  could both have overlapped the same write of v, which could have been a write that occurred in the process of changing  $v^*$ 's value from 0 to 1. Therefore, if the read of  $v^*$  that finds v equal to  $v_i$  returns the value 1, then the subsequent read that finds v equal to  $v_{i-1}$  must also return the value 1, since both reads could be overlapping the same write and, in that case, two successive reads of an atomic register cannot return first the new value, then the old one.

The first read, which finds v equal to  $v_n$ , must return the value 1, since it could have occurred after the completion of a write of 1. By induction, this implies that the last read, which found v equal to  $v_0$ , must return the value 1. However, this read could have occurred after a write of 0 and before any subsequent write, so returning the value 1 would violate the assumption that the register  $v^*$  is safe. (An atomic register is a fortiori safe.) This is the required contradiction.

•

This theorem could be expressed and proved using the formalism of Part I and the definitions of the next section, but doing so would lead to no new insight. The formalization of this theorem is therefore left as an exercise for the reader who wishes to gain practice in using the formalism.

The theorem is false if no bound is placed on the number of values a register can hold. Given a regular register v that can assume an unbounded

<sup>&</sup>lt;sup>9</sup>If we assume that the writer has only a finite number of internal states, then we can conclude that the precise sequence of values  $v_0, \ldots, v_n$  is written infinitely many times when changing the value of  $v^*$  from 0 to 1. However, with an infinite number of internal states, it is possible for the writer never to perform the same sequence of writes to v twice.

number of values, an atomic register  $v^*$  is implemented as follows. The writer sets v equal to a pair consisting of the value of  $v^*$  and a sequential version number. The reader reads v and compares the version number with the previous one it read. If the new version number is higher, then it uses the value it just read; if the new version number is lower, then it forgets the value and version number it just read and uses the previously read value. The correctness of this algorithm follows easily from Proposition 5 of Section 6. By assuming that registers hold only a bounded set of values, such algorithms are disallowed.

Finally, we come to the algorithm for constructing a single-reader, multivalued, atomic register from regular ones. Let  $v^*$  denote the atomic register being implemented, and let the writer set this register by writing into a shared regular register v. Suppose that some value  $\mu$  of  $v^*$  is represented by letting v equal  $v_0$ , and that to change the value of  $v^*$  to another value v, the writer successively sets v to the values  $v_1, v_2, \ldots, v_n$ , where  $v = v_n$  represents  $v^* = v$ . The proof of the above theorem rested upon showing that the reader is in a quandary if v successive reads return the values  $v_n, v_{n-1}, \ldots, v_0$ . If the v-represented the integral of v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that the reader is in a quandary if v-represented upon showing that v-represents v-represented upon showing that v-represents v-rep

The way out of this problem is to encode, as part of v's value, a boolean quantity called a color. Each value of  $v^*$  is represented by two different values of v—one of each color. Every time the reader reads v, it sets a boolean register c to the color of the value it just read. When the writer wants to write a new value of  $v^*$ , it first reads c and then makes the series of values  $v_1, \ldots, v_n$  it writes to v have the opposite color to c. (Thus, the reader tries to keep c equal to the color of v, and the writer tries to keep the color of v different from c.) It can be shown that if  $v \ge 0$ , so at least three intermediate values are written when changing the value of  $v^*$ , then successive reads cannot obtain the sequence  $v_n, \ldots, v_0$ . This enables one to devise an algorithm in which the writer changes the value of the register from v to v by first writing a series of intermediate values v0. However, one can do better, and an algorithm is developed below that uses only two intermediate values.

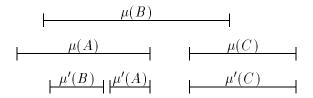

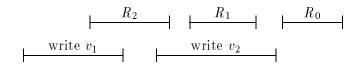

When n=3, so the writer writes the sequence  $v_1, v_2, v_3$ , with  $v_3$  representing the new value  $\nu$ , it is possible for three successive reads  $R_3, R_2$ ,

Figure 6: Reads  $R_2$  and  $R_1$  overlapping the write of  $v_2$ .

$R_1$  to obtain the values  $v_3$ ,  $v_2$ , and  $v_1$ , respectively. However, it will be shown that this can happen only if the two reads  $R_2$  and  $R_1$  both overlap a single write of  $v_2$ . As indicated by Figure 6, this implies that a fourth read  $R_0$  cannot overlap the write of the value  $v_1$  that was obtained by  $R_1$ . Therefore, if the fourth read  $R_0$  obtains  $v_0$ , the reader can return the value  $\mu$  represented by  $v_0$  with no fear of the pair  $R_1$ ,  $R_0$  returning a forbidden "new-old" sequence.